| Citation: |

Hui Zhang, Dan Li, Lei Wan, Hui Zhang, Haijun Wang, Yuan Gao, Feili Zhu, Ziqi Wang, Xuexin Ding. A 430 mW 16 b 170 MS/s CMOS pipelined ADC with 77.2 dB SNR and 97.6 dB SFDR[J]. Journal of Semiconductors, 2016, 37(3): 035003. doi: 10.1088/1674-4926/37/3/035003

****

H Zhang, D Li, L Wan, H Zhang, H J Wang, Y Gao, F L Zhu, Z Q Wang, X X Ding. A 430 mW 16 b 170 MS/s CMOS pipelined ADC with 77.2 dB SNR and 97.6 dB SFDR[J]. J. Semicond., 2016, 37(3): 035003. doi: 10.1088/1674-4926/37/3/035003.

|

A 430 mW 16 b 170 MS/s CMOS pipelined ADC with 77.2 dB SNR and 97.6 dB SFDR

DOI: 10.1088/1674-4926/37/3/035003

More Information

-

Abstract

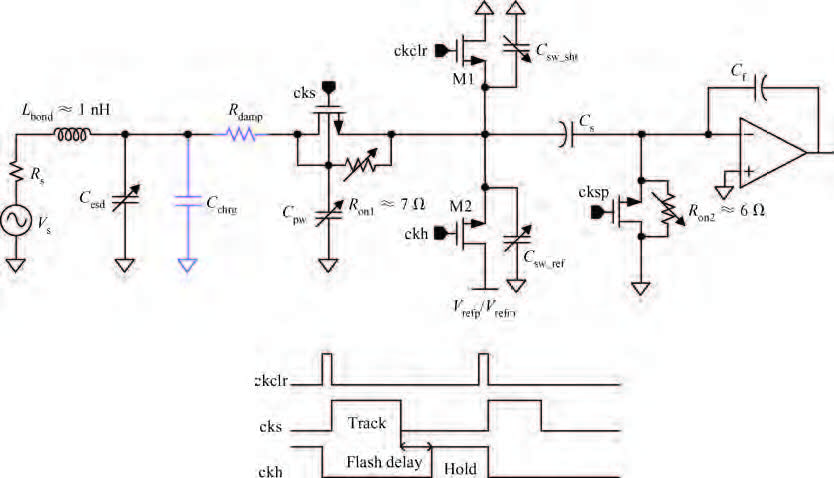

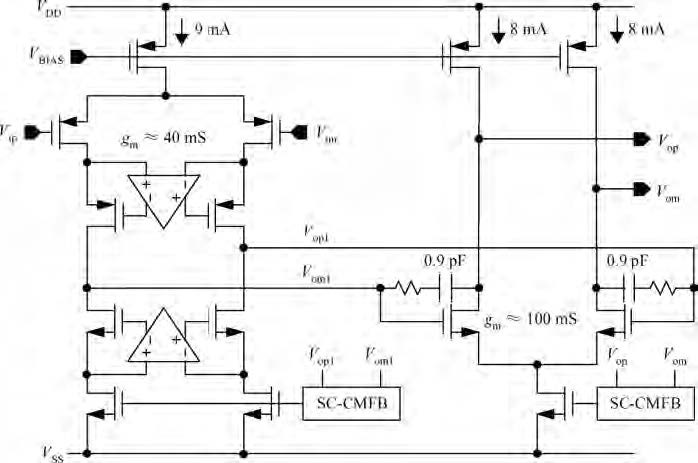

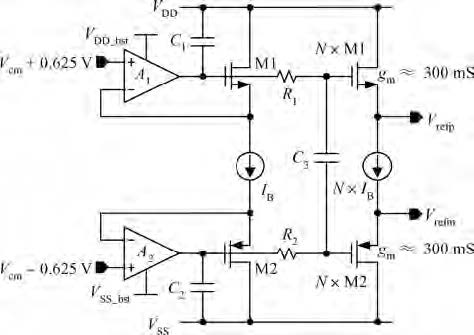

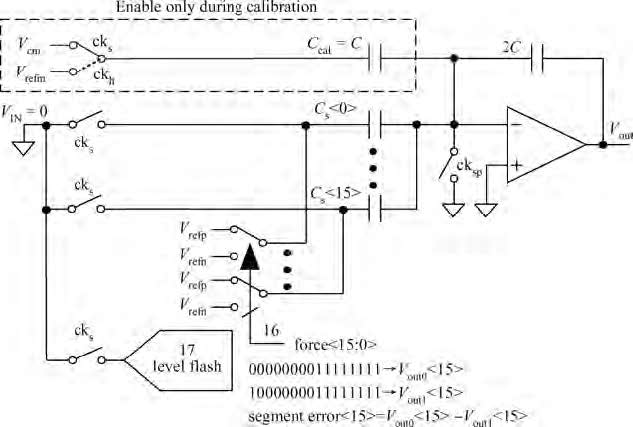

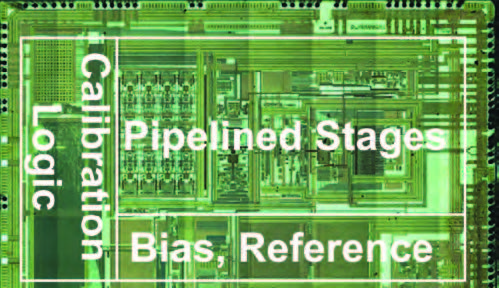

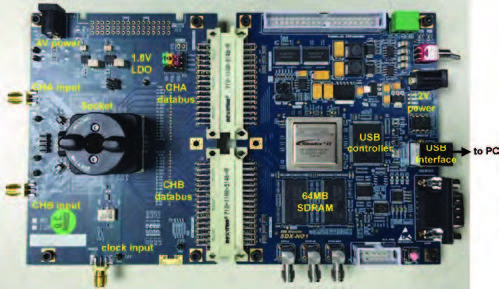

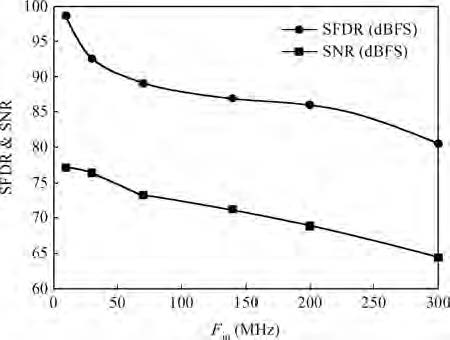

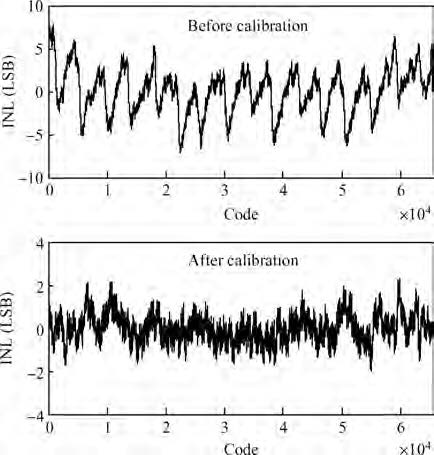

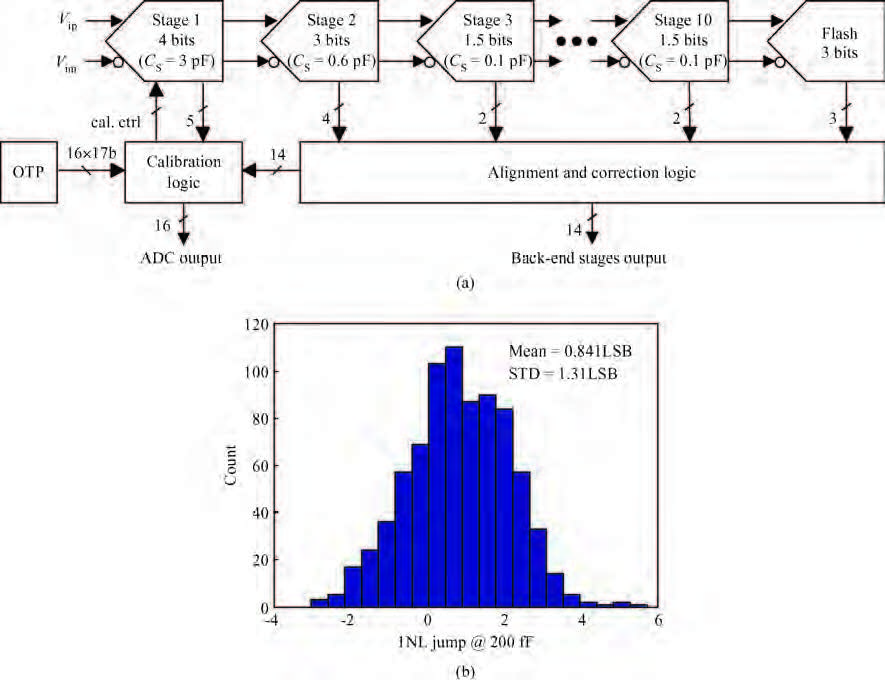

A 16-bit 170 MS/s pipelined ADC implemented in 0.18μm CMOS process is presented in this paper. An improved digital calibration method and a linearized sampling front-end are employed to achieve a high SFDR. The enlarged full scale range makes it possible to obtain a high SNR with smaller sampling capacitors, thus achieving higher speed and low power. This ADC attains an SNR of 77.2 dBFS, an SFDR of 97.6 dBc for a 10 MHz input signal, while preserving an SFDR>80 dBc up to 300 MHz input frequency. The ADC consumes 430 mW from a 1.8 V supply and occupies a 17 mm2 active area.-

Keywords:

- pipelined ADC,

- calibration,

- SHA-less,

- IF sampling

-

References

[1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] -

Proportional views

DownLoad:

DownLoad: