| Citation: |

Jun'an Zhang, Guangjun Li, Ruitao Zhang, Dongbing Fu, Jiaoxue Li, Yafeng Wei, Bo Yan, Jun Liu, Ruzhang Li. A 2.5 GS/s 14-bit D/A converter with 8 to 1 MUX[J]. Journal of Semiconductors, 2016, 37(3): 035004. doi: 10.1088/1674-4926/37/3/035004

****

J Zhang, G J Li, R T Zhang, D B Fu, J X Li, Y F Wei, B Yan, J Liu, R Z Li. A 2.5 GS/s 14-bit D/A converter with 8 to 1 MUX[J]. J. Semicond., 2016, 37(3): 035004. doi: 10.1088/1674-4926/37/3/035004.

|

-

Abstract

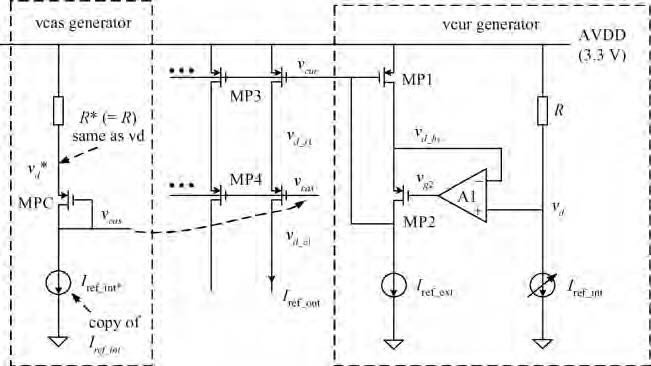

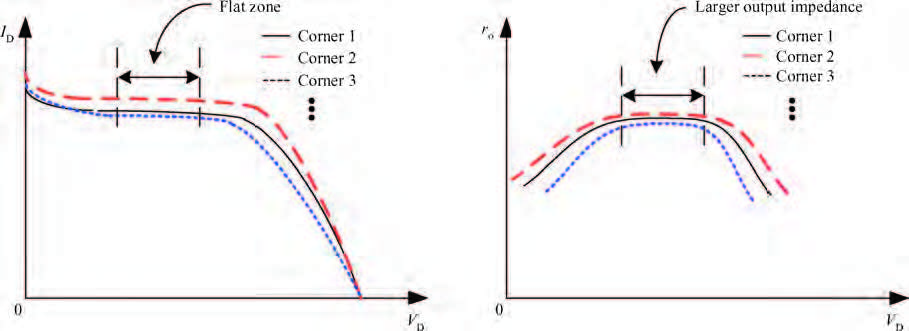

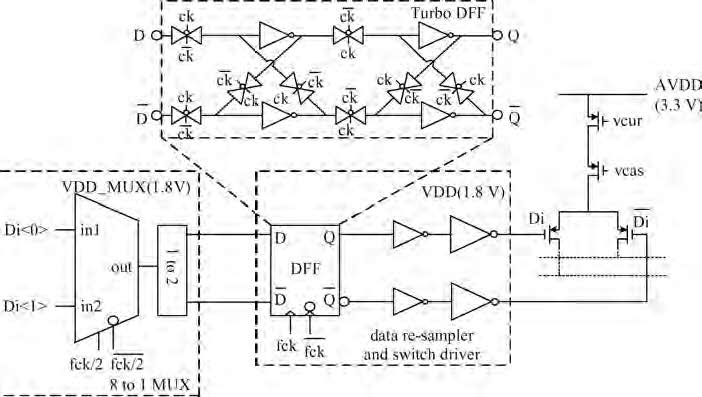

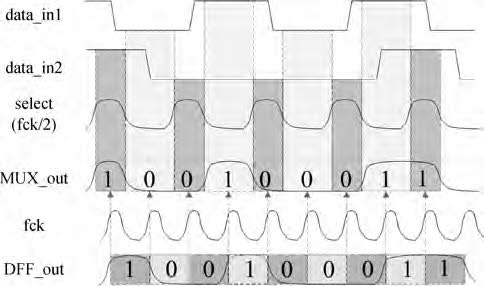

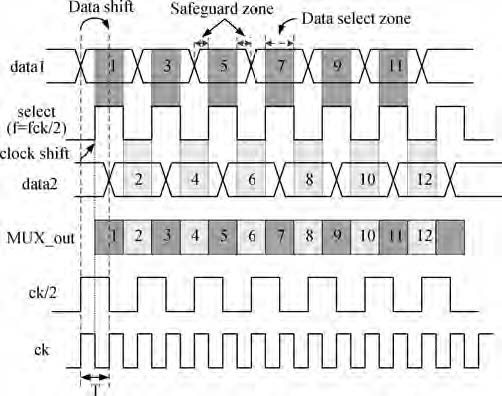

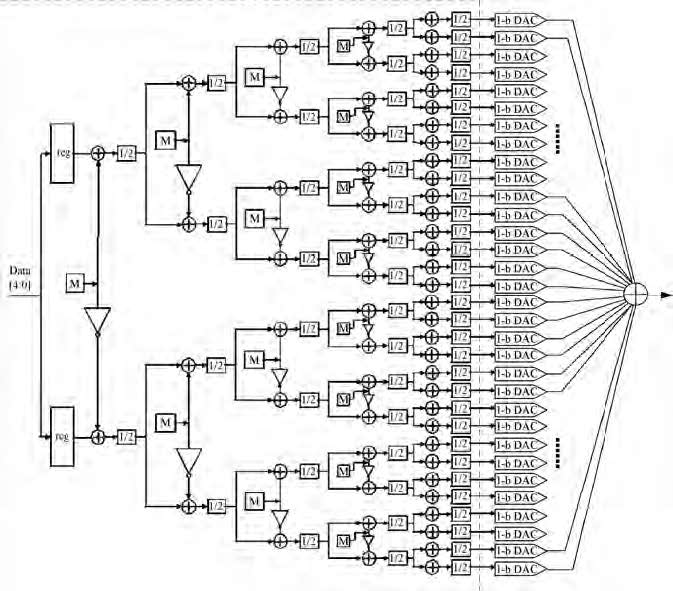

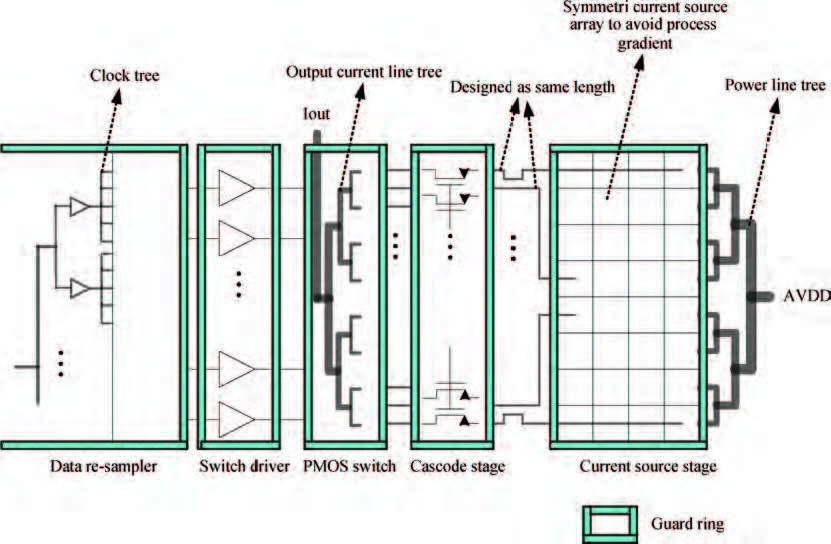

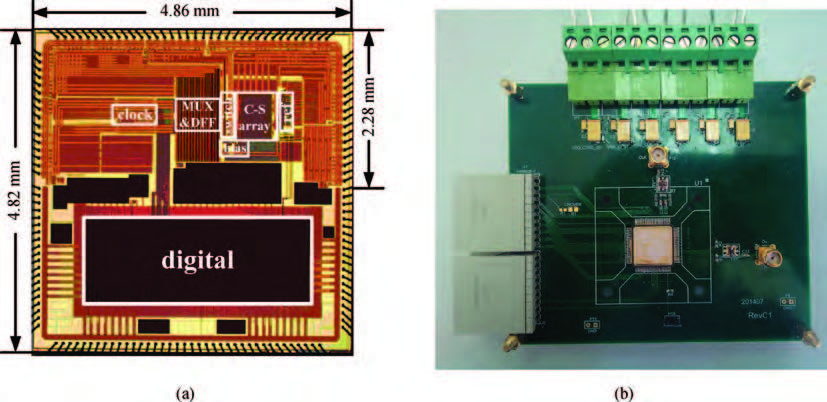

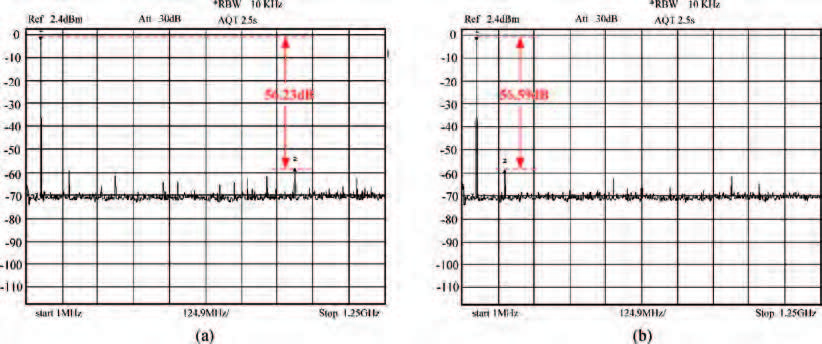

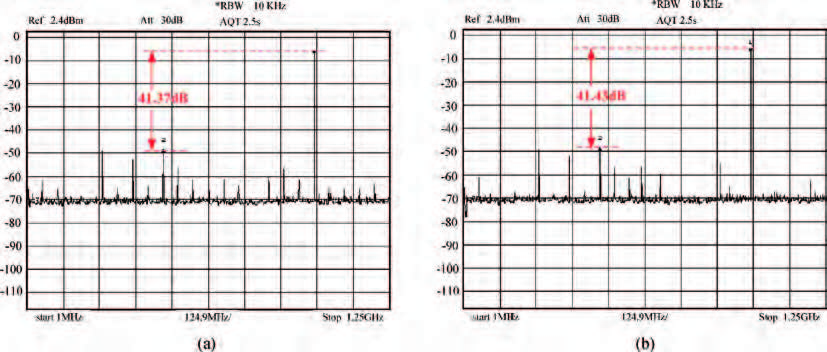

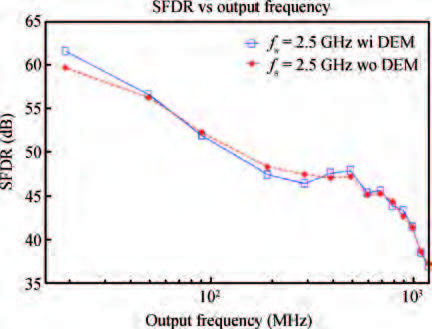

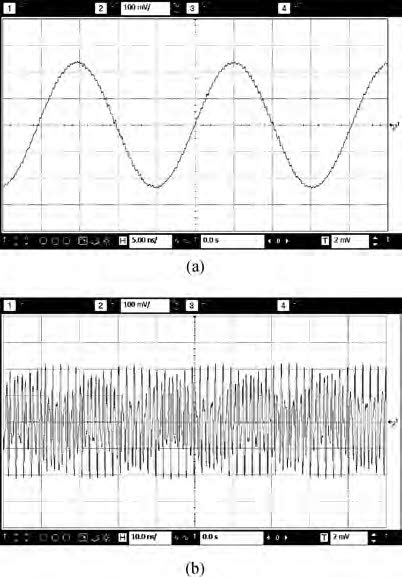

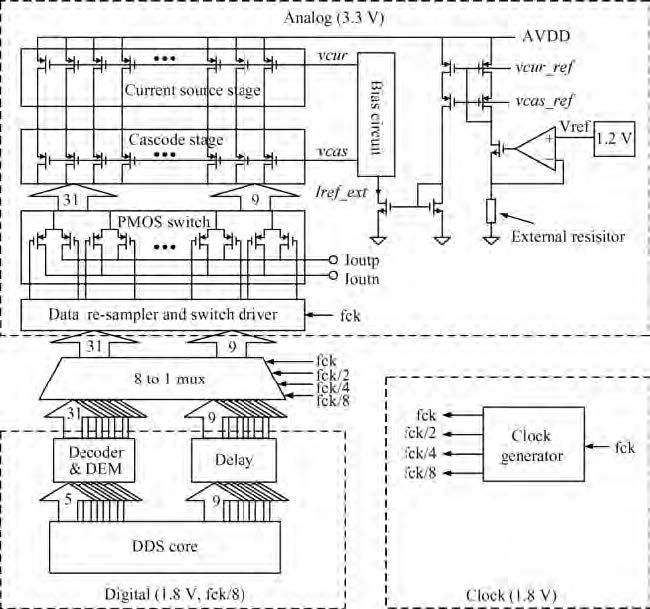

A 2.5 GS/s 14-bit D/A converter(DAC) with 8 to 1 MUX is presented. This 14-bit DAC uses a "5+9" segment PMOS current-steering architecture. A bias circuit which ensures the PMOS current source obtains a larger output impedance under every PVT(process, source voltage and temperature) corner is also presented. The 8 to 1 MUX has a 3 stage structure, and a proper timing sequence is designed to ensure reliable data synthesis. A DEM function which is merged with a "5-31" decoder is used to improve the DAC's dynamic performance. This DAC is embedded in a 2.5 GHz direct digital frequency synthesizer(DDS) chip, and is implemented in a 0.18μm CMOS technology, occupies 4.86×2.28 mm2 including bond pads(DAC only), and the measured performance is SFDR>40 dB(with and without DEM) for output signal frequency up to 1 GHz. Compared with other present published DACs with a non-analog-resample structure(means return-to-zero or quad-switch structure is unutilized), this paper DAC's clock frequency(2.5 GHz) and higher output frequency SFDR(>40 dB, up to 1 GHz) has some competition. -

References

[1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] -

Proportional views

DownLoad:

DownLoad: