| Citation: |

Weihua Ruan, Qingsheng Hu. A 0.18μm CMOS transmit physical coding sublayer IC for 100G Ethernet[J]. Journal of Semiconductors, 2016, 37(3): 035005. doi: 10.1088/1674-4926/37/3/035005

****

W H Ruan, Q S Hu. A 0.18μm CMOS transmit physical coding sublayer IC for 100G Ethernet[J]. J. Semicond., 2016, 37(3): 035005. doi: 10.1088/1674-4926/37/3/035005.

|

A 0.18μm CMOS transmit physical coding sublayer IC for 100G Ethernet

DOI: 10.1088/1674-4926/37/3/035005

More Information

-

Abstract

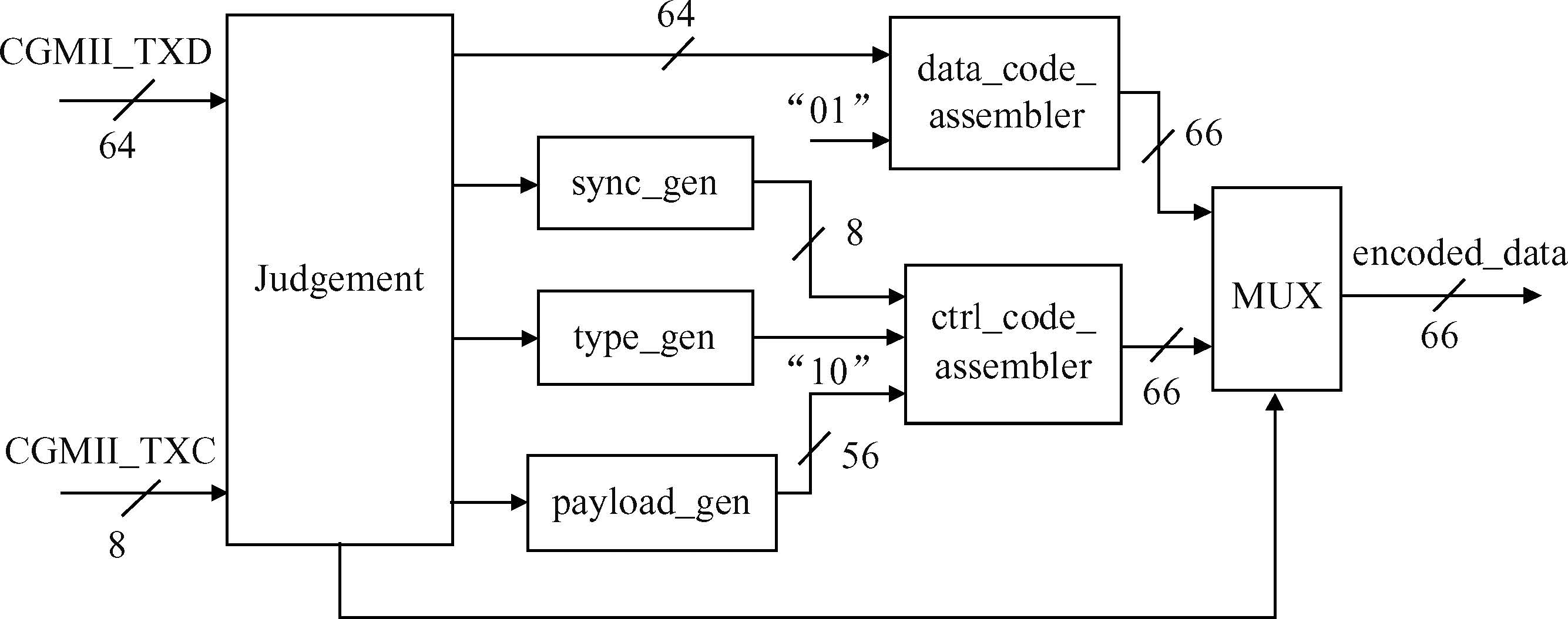

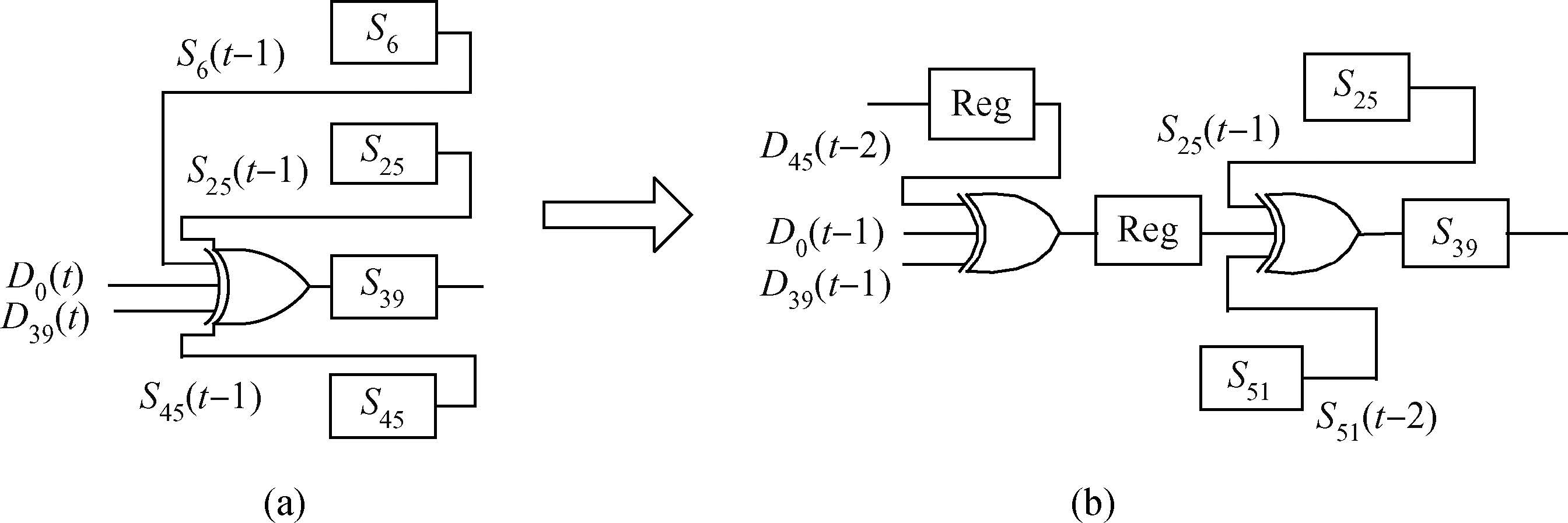

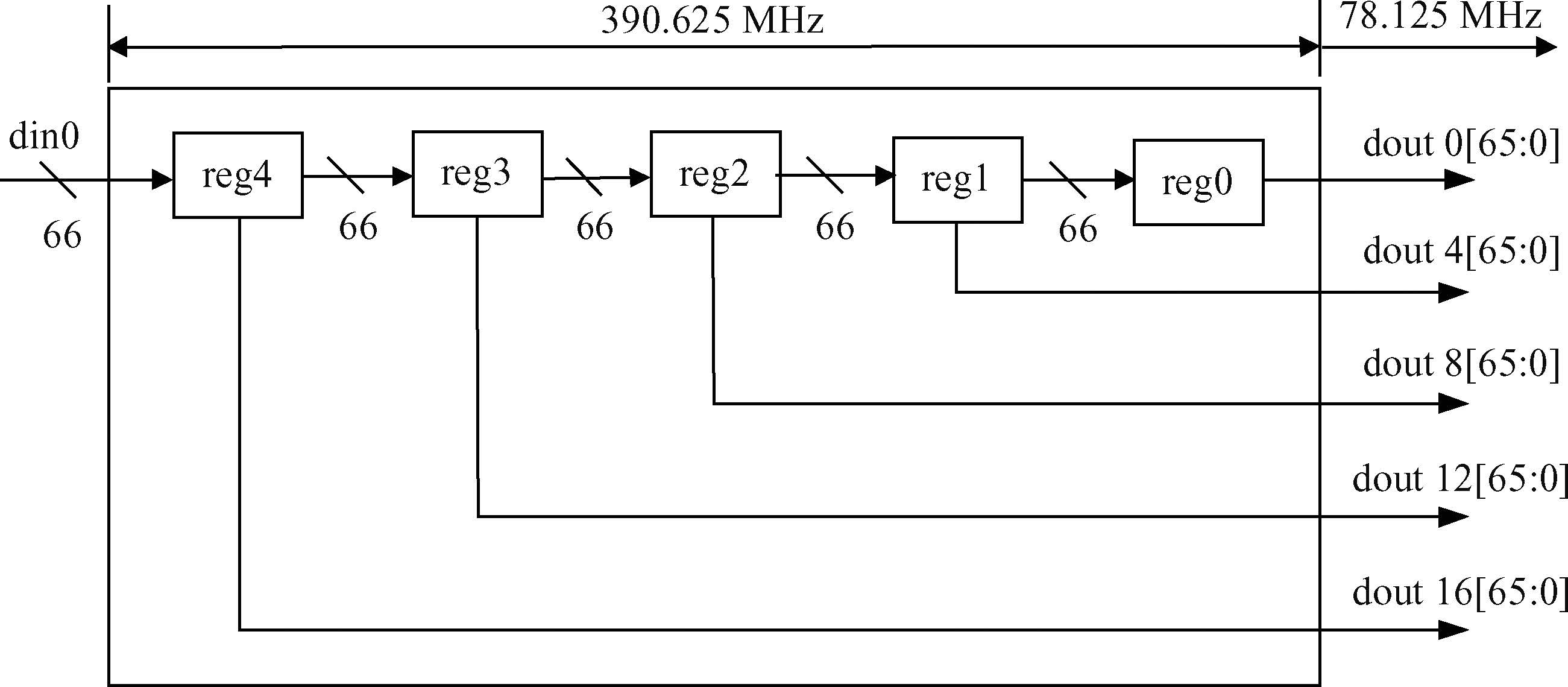

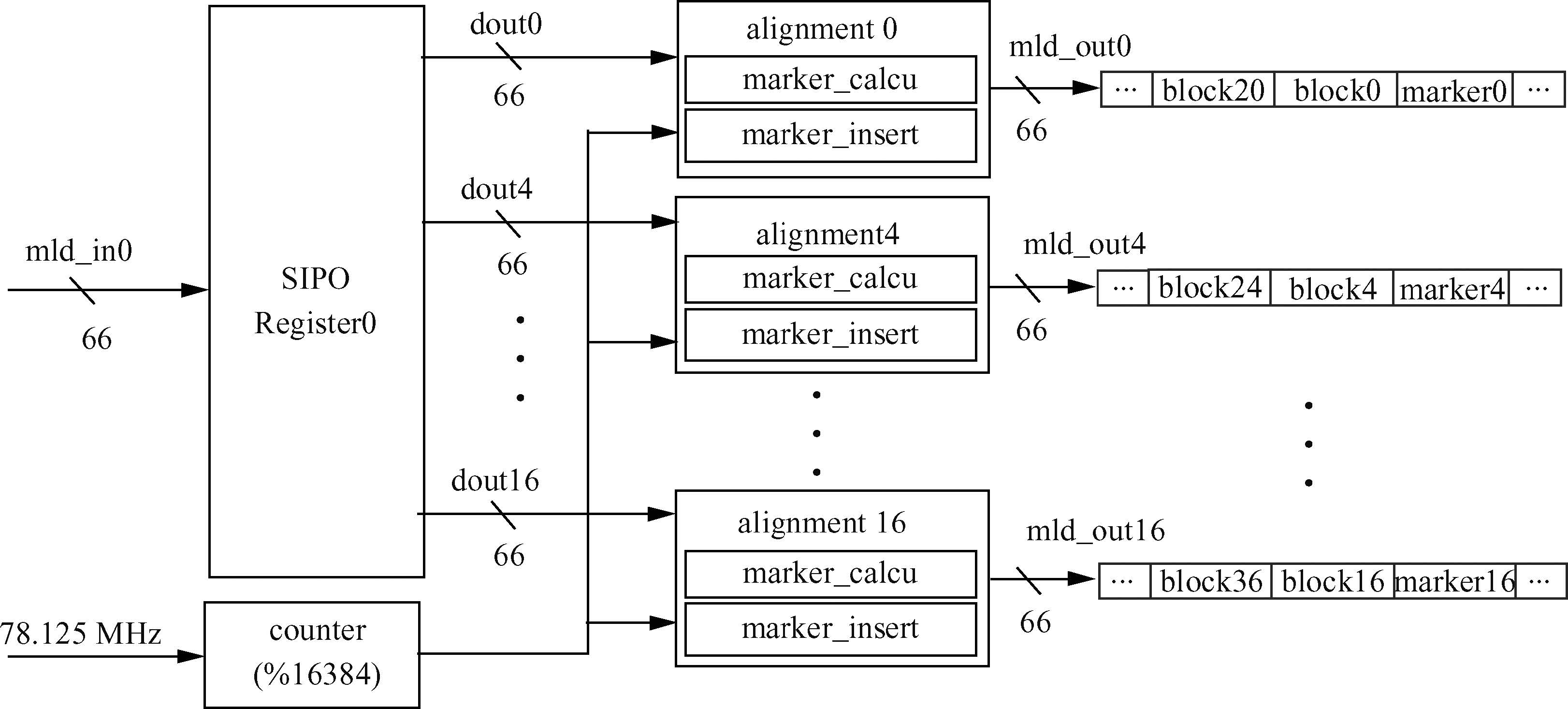

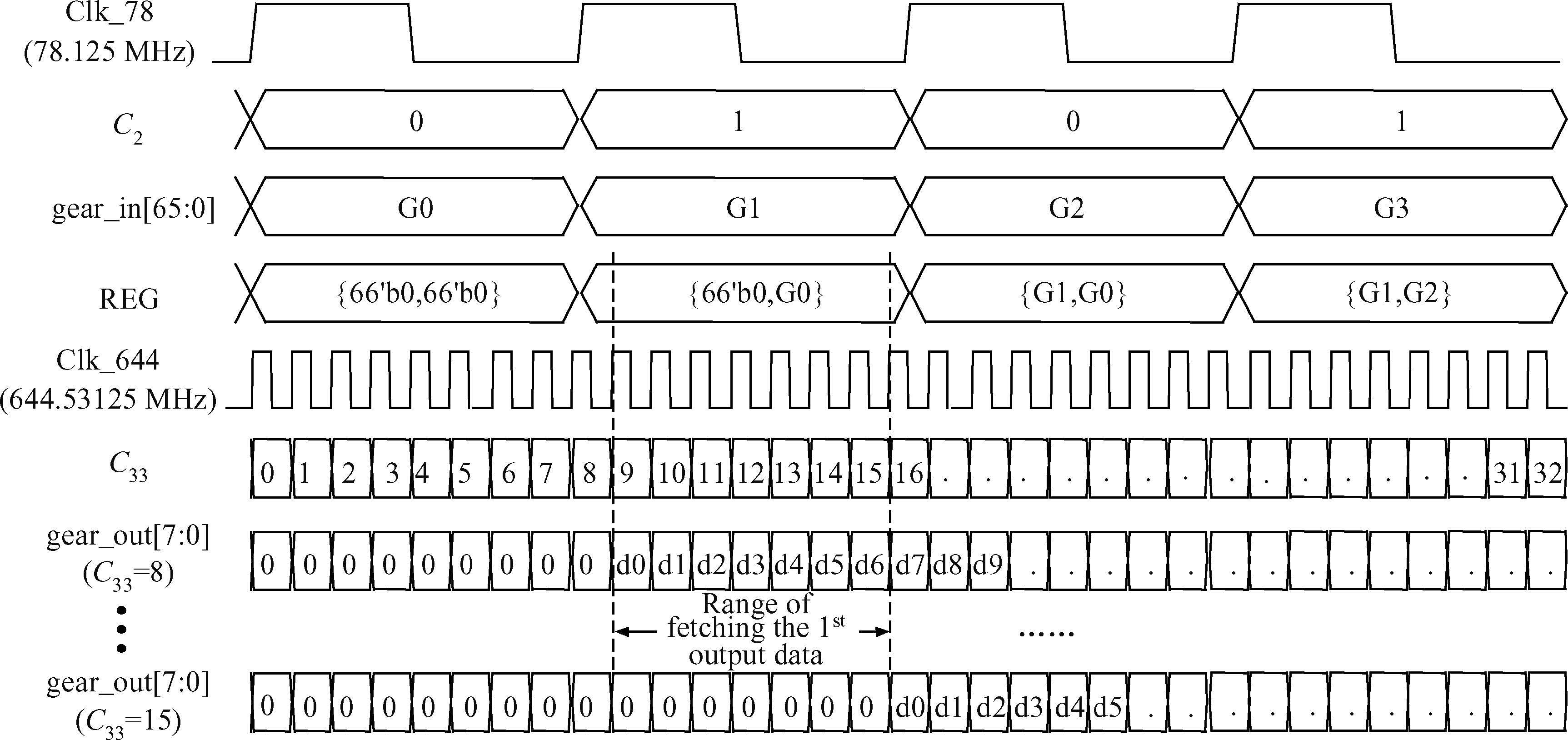

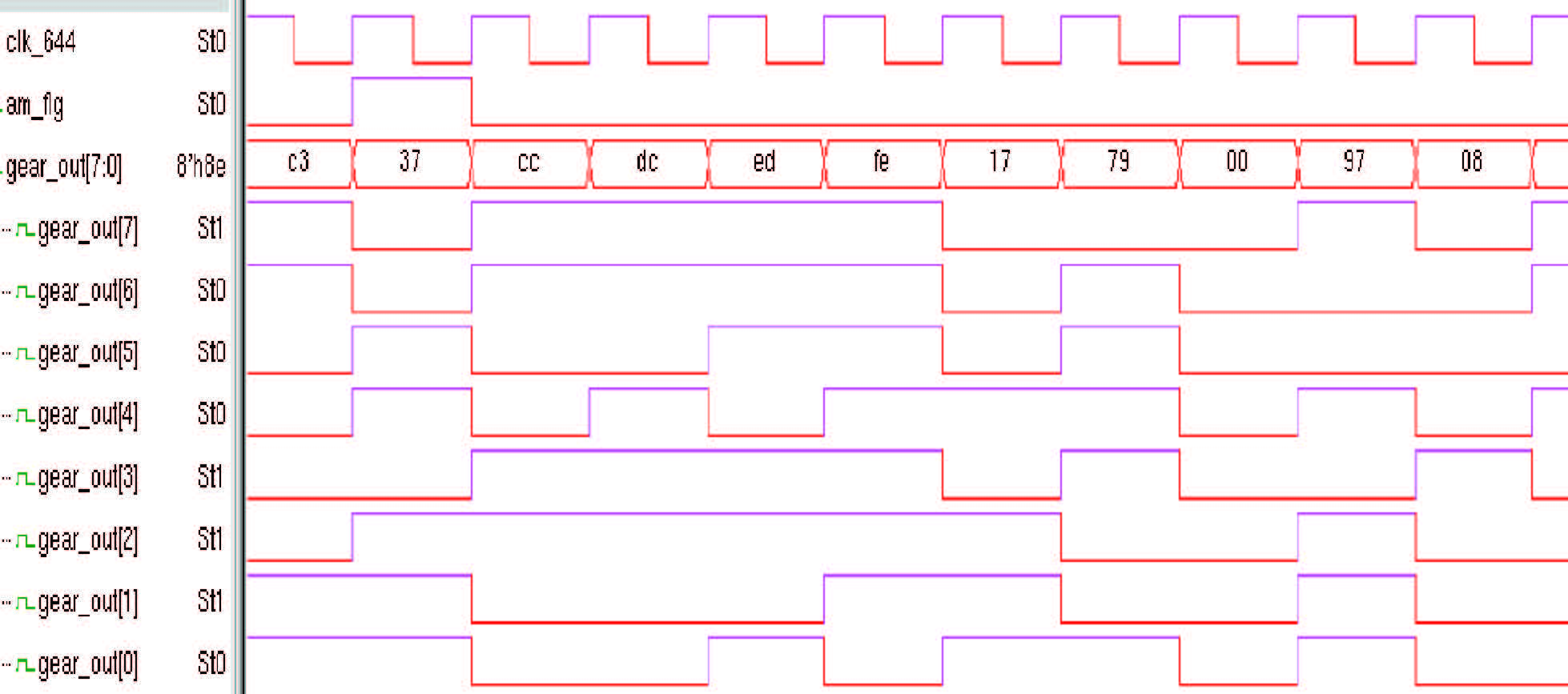

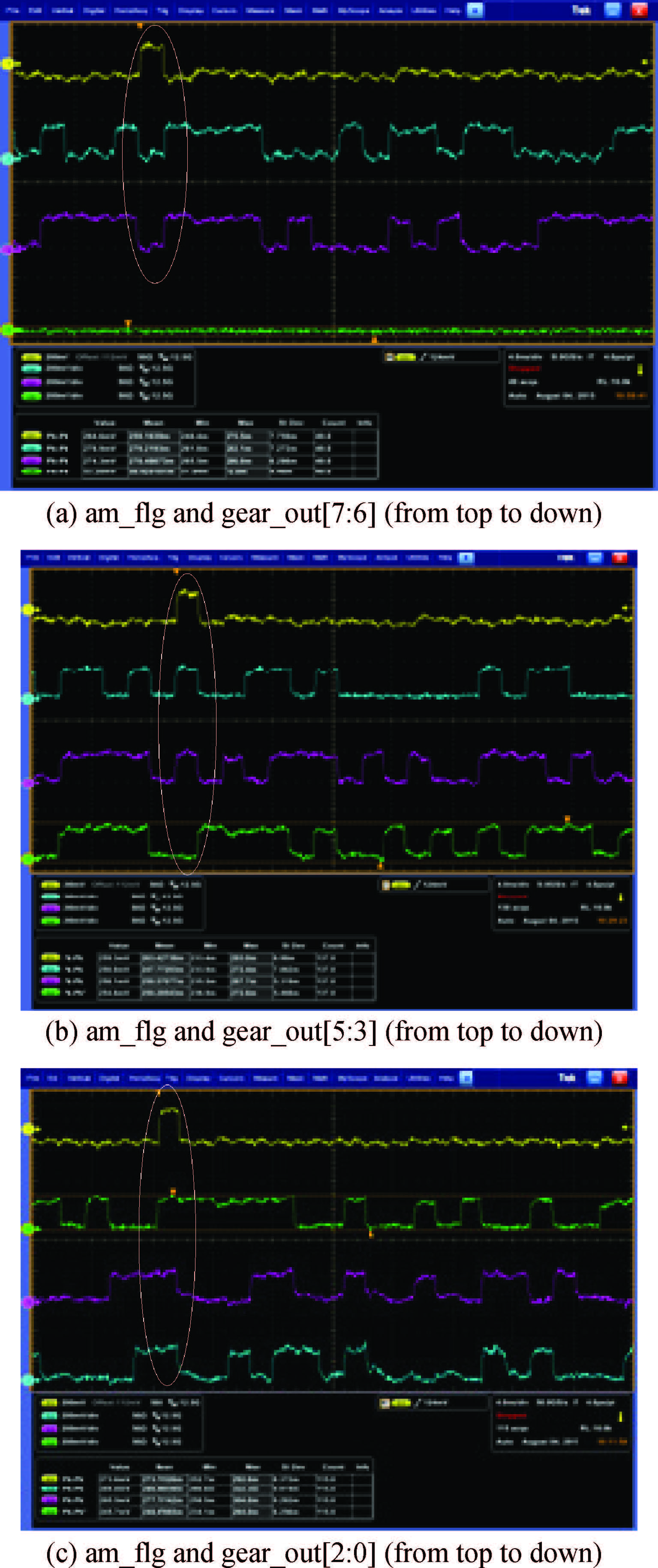

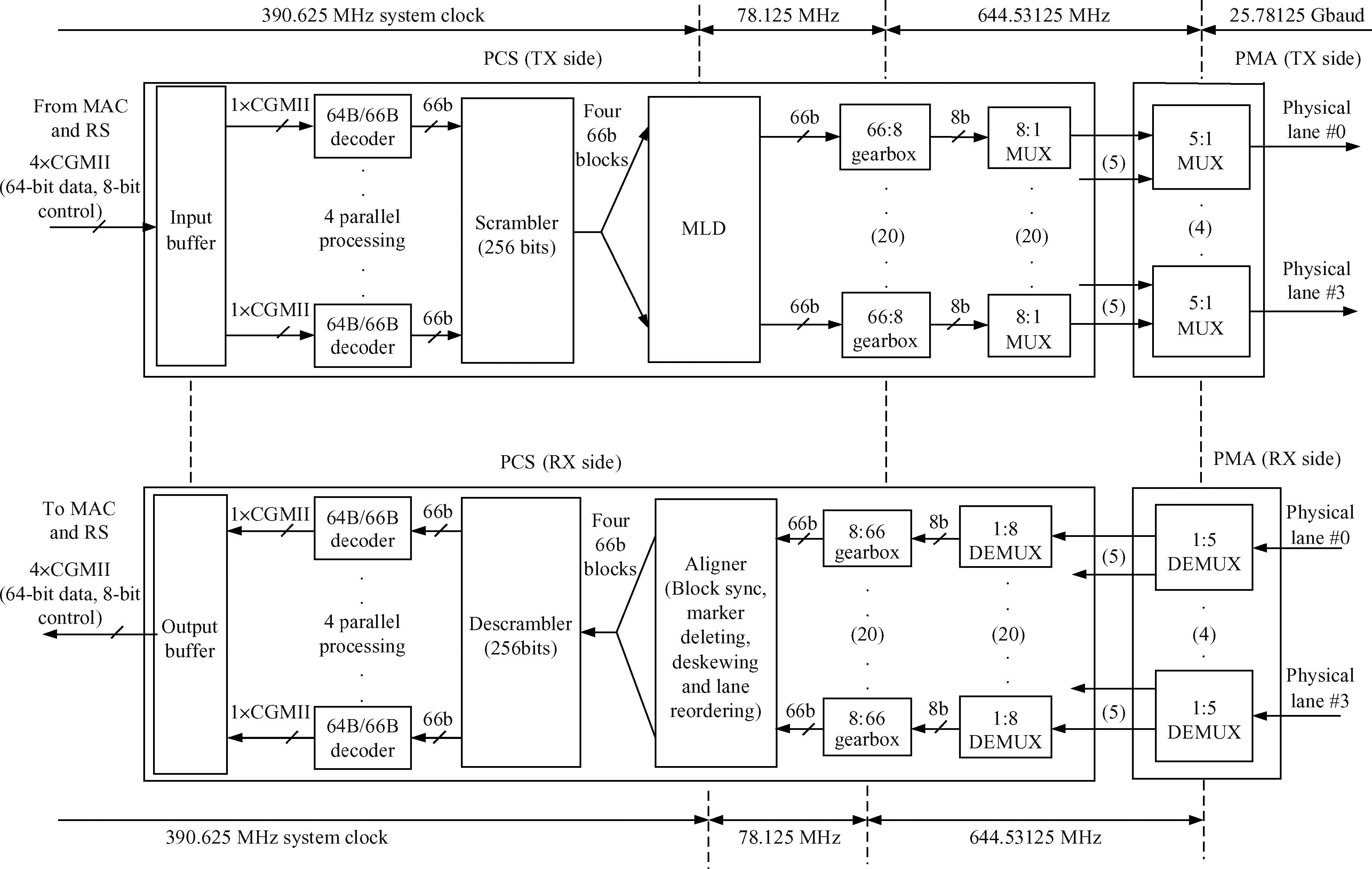

This paper presents a transmit physical coding sublayer(PCS) circuit for 100G Ethernet. Based on the 4×25 Gb/s architecture according to the IEEE P802.3ba and IEEE P802.3bmTM/D1.1 standards, this PCS circuit is designed using a semi-custom design method and consists of 4 modules including 64B/66B encoder, scrambler, multiple lanes distribution and 66:8 gearbox. By using the pipeline structure and several optimization techniques, the working speed of the circuit is increased significantly. The parallel scrambling combined with logic optimization also improve the performance. In addition, a kind of phase-independent structure is employed in the design of the gearbox to ensure it can work stably and reliably at high frequency. This PCS circuit has been fabricated based on 0.18μm CMOS technology and the total area is 1.7×1.7 mm2. Measured results show that the circuit can work properly at 100 Gb/s and the power consumption is about 284 mW with a 1.8 V supply.-

Keywords:

- 100GbE,

- PCS layer,

- 64B/66B encoder,

- scrambler,

- gearbox

-

References

[1] [2] [3] [4] [5] [6] [7] [8] [9] -

Proportional views

DownLoad:

DownLoad: