| Citation: |

Xuemin Li, Mao Ye, Gongyuan Zhao, Yun Zhang, Yiqiang Zhao. A new curvature compensation technique for CMOS voltage reference using |VGS| and ΔVBE[J]. Journal of Semiconductors, 2016, 37(5): 055005. doi: 10.1088/1674-4926/37/5/055005

****

X M Li, M Ye, G Y Zhao, Y Zhang, Y Q Zhao. A new curvature compensation technique for CMOS voltage reference using |VGS| and ΔVBE[J]. J. Semicond., 2016, 37(5): 055005. doi: 10.1088/1674-4926/37/5/055005.

|

A new curvature compensation technique for CMOS voltage reference using |VGS| and ΔVBE

DOI: 10.1088/1674-4926/37/5/055005

More Information

-

Abstract

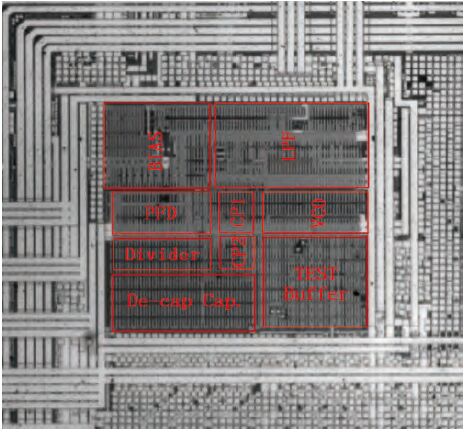

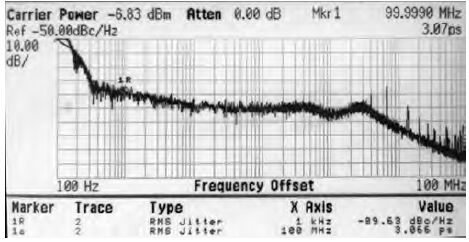

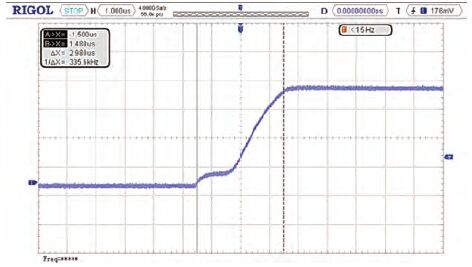

A new mixed curvature compensation technique for CMOS voltage reference is presented, which resorts to two sub-references with complementary temperature characteristics. The first sub-reference is the source-gate voltage |VGS|p of a PMOS transistor working in the saturated region. The second sub-reference is the weighted sum of gate-source voltages |VGS|n of NMOS transistors in the subthreshold region and the difference between two base-emitter voltages ΔVBE of bipolar junction transistors (BJTs). The voltage reference implemented utilizing the proposed curvature compensation technique exhibits a low temperature coefficient and occupies a small silicon area. The proposed technique was verified in 0.18 μm standard CMOS process technology. The performance of the circuit has been measured. The measured results show a temperature coefficient as low as 12.7 ppm/℃ without trimming, over a temperature range from -40 to 120 ℃, and the current consumption is 50 μA at room temperature. The measured power-supply rejection ratio (PSRR) is -31.2 dB @ 100 kHz. The circuit occupies an area of 0.045 mm2.-

Keywords:

- voltage reference,

- sub-reference,

- curvature compensation,

- subthreshold

-

References

[1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] -

Proportional views

DownLoad:

DownLoad: