| Citation: |

Chuang Gao, Xing Zhao, Kai Zhao, Jiantou Gao, Bingqing Xie, Fang Yu, Jiajun Luo. DSOI-a novel structure enabling adjust circuit dynamically[J]. Journal of Semiconductors, 2016, 37(6): 065003. doi: 10.1088/1674-4926/37/6/065003

****

C Gao, X Zhao, K Zhao, J T Gao, B Q Xie, F Yu, J J Luo. DSOI-a novel structure enabling adjust circuit dynamically[J]. J. Semicond., 2016, 37(6): 065003. doi: 10.1088/1674-4926/37/6/065003.

|

DSOI-a novel structure enabling adjust circuit dynamically

DOI: 10.1088/1674-4926/37/6/065003

More Information

-

Abstract

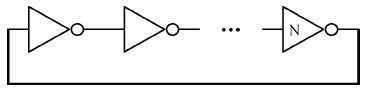

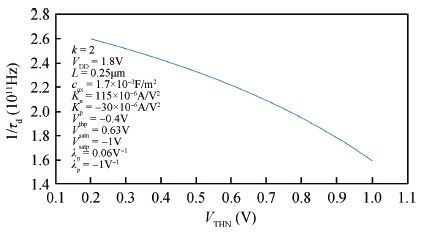

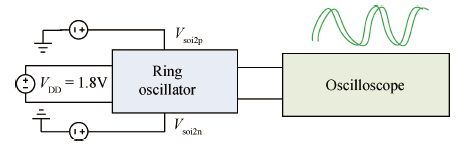

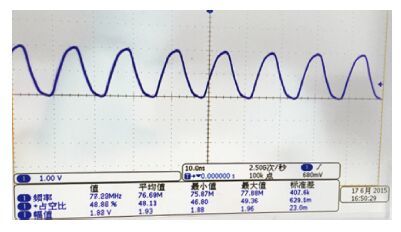

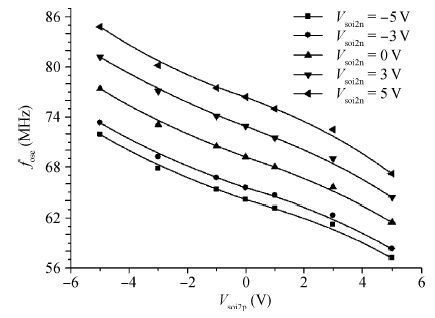

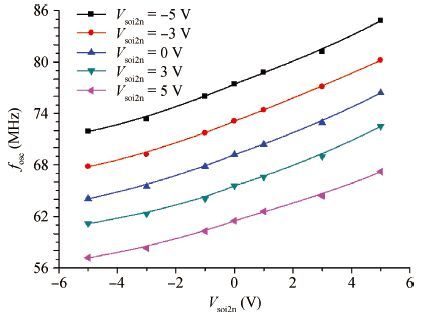

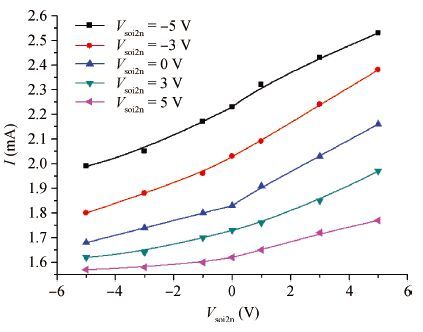

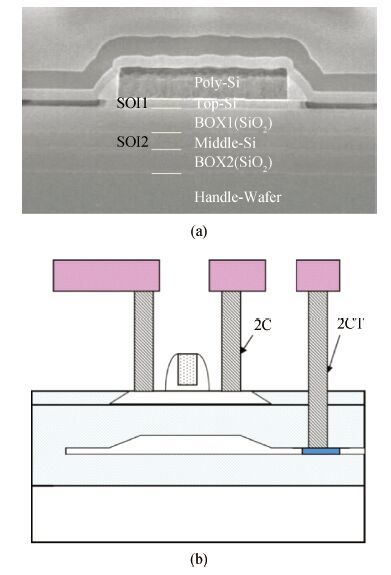

A double silicon on insulator (DSOI) structure was introduced based on fully depleted SOI (FDSOI) technology. The circuit performance could be adjusted dynamically through the separate back gate electrodes applied to N-channel and P-channel devices. Based on DSOI ring oscillator (OSC), this paper focused on the theoretical analysis and electrical test of how the OSC's frequency being influenced by the back gate electrodes (soi2n, soi2p). The testing results showed that the frequency and power consumption of OSC could change nearly linearly along with the back gate bias. According to the different requirements of the circuit designers, the circuit performance could be improved by positive soi2n and negative soi2p, and the power consumption could be reduced by negative soi2n and positive soi2p. The best compromise between performance and power consumption of the circuit could be achieved by appropriate back gate biasing.-

Keywords:

- DSOI,

- FDSOI,

- ring oscillator,

- back gate control,

- high performance,

- low power consumption

-

References

[1] Colinge J P. Silicon on insulator technology:materials to VLSI. Norwood, MA:Kluwer, 1991[2] Bu Jianhui, Li Shuzhen, Luo Jiajun, et al. The STI stress effect on deep submicron PDSOI MOSFETs. Journal of Semiconductors, 2014, 35(3):034008[3] Streel G D, Bol D. Impact of back gate biasing schemes on energy and robustness of ULV logic in 28 nm UTBB FDSOI technology. IEEE International Symposium on Low Power Electronics and Design (ISLPED), 2013:255[4] Bernard S, Belleville M, Valentian A, et al. Experimental analysis of flip-flops minimum operating voltage in 28 nm FDSOI and the impact of back bias and temperature. International Workshop on the Power and Timing Modeling, Optimization and Simulation (PATMOS), 2014:1[5] Chung G S, Kawahito S, Ashiki M, et al. Novel high-performance pressure sensors using double SOI structures. International Conference on the Solid-State Sensors and Actuators, 1991:676[6] Zhao Kai, Zhao Xing, Gao Jiantou, et al. DSOI FET-a novel TID tolerant SOI transistor. IEEE International Conference on the Solid-State and Integrated Circuit Technology (ICSICT), 2014:1[7] Arai Y. Progress on silicon-on-insulator monolithic pixel process. Proceedings of the 22nd International Workshop on Vertex Detectors (Vertex2013), Sep. 2013, 1:21[8] Zhang R T, Roy K. Low-power high-performance double-gate fully depleted SOI circuit design. IEEE Trans Electron Devices, 2002, 49(5):852[9] Rabaey J M, Chandrakasan A, Nikolic B. Digital integrated circuits-a design perspective. Beijing:Publishing House of Electronics Industry, 2012[10] Huang Ru, Zhang Guoyan, Li Yingxue, et al. SOI CMOS technology and its Application. Beijing:Science Press, 2005 -

Proportional views

DownLoad:

DownLoad: