| Citation: |

Xiangning Fan, Jian Tao, Kuan Bao, Zhigong Wang. A reconfigurable passive mixer for multimode multistandard receivers in 0.18 μm CMOS[J]. Journal of Semiconductors, 2016, 37(8): 085001. doi: 10.1088/1674-4926/37/8/085001

****

X N Fan, J Tao, K Bao, Z G Wang. A reconfigurable passive mixer for multimode multistandard receivers in 0.18 μm CMOS[J]. J. Semicond., 2016, 37(8): 085001. doi: 10.1088/1674-4926/37/8/085001.

|

A reconfigurable passive mixer for multimode multistandard receivers in 0.18 μm CMOS

DOI: 10.1088/1674-4926/37/8/085001

More Information

-

Abstract

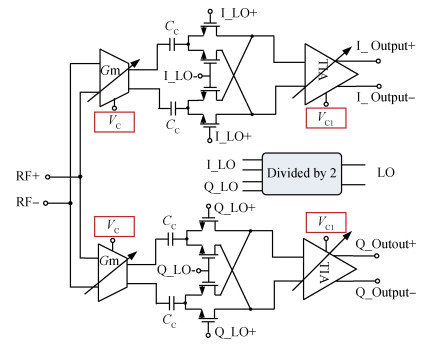

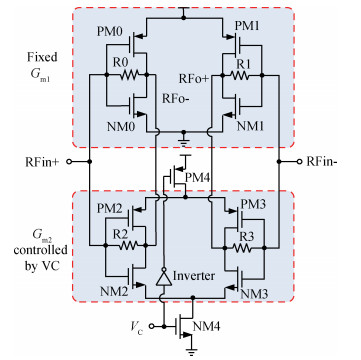

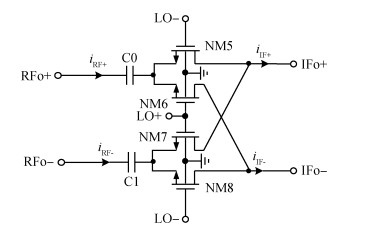

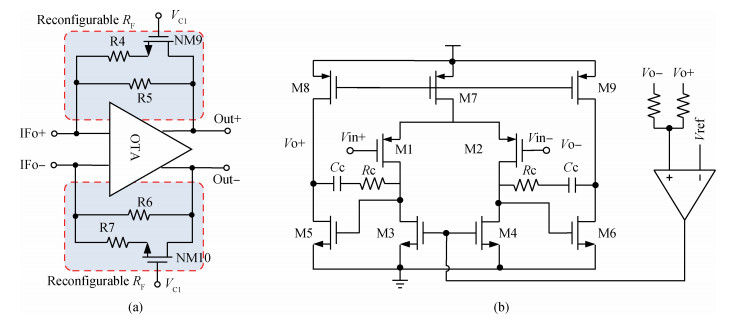

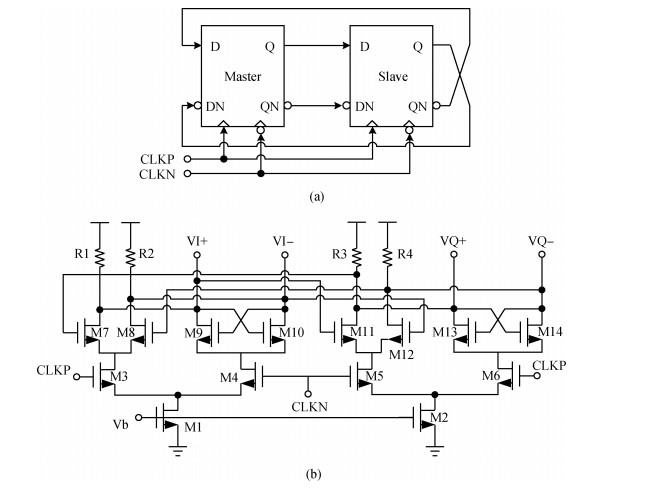

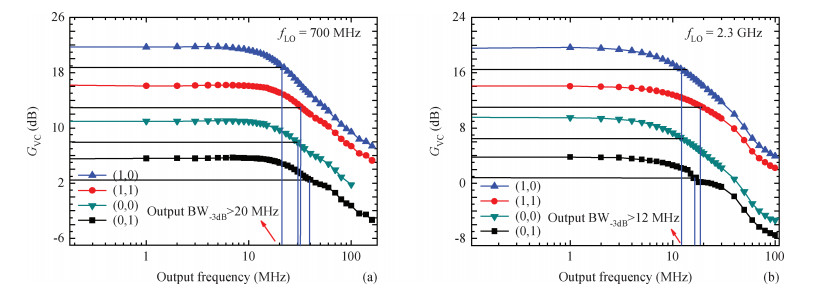

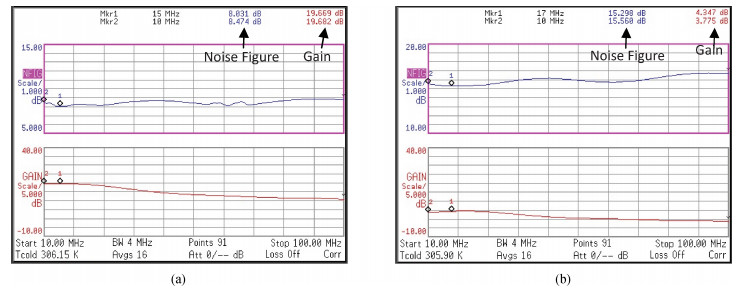

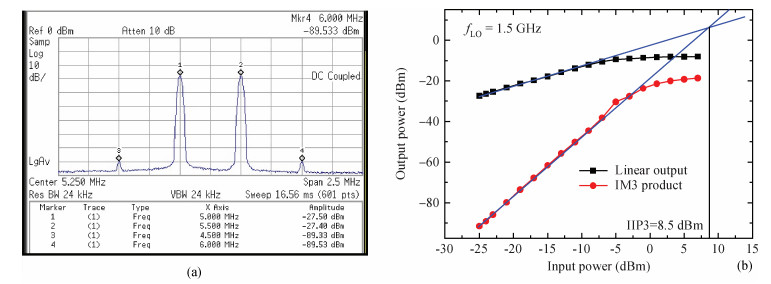

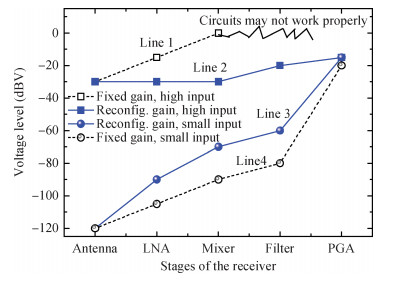

This paper presents a reconfigurable quadrature passive mixer for multimode multistandard receivers. By using controllable transconductor and transimpedance-amplifier stages, the voltage conversion gain of the mixer is reconfigured according to the requirement of the selected communication standard Other characteristics such as noises figure, linearity and power consumption are also reconfigured consequently. The design concept is verified by implementing a quadrature passive mixer in 0.18 μm CMOS technology. On wafer measurement results show that, with the input radio frequency ranges from 700 MHz to 2.3 GHz, the mixer achieves a controllable voltage conversion gain from 4 to 22 dB with a step size of 6 dB. The measured maximumⅡP3 is 8.5 dBm and the minimum noise figure is 8.0 dB. The consumed current for a single branch (I or Q) ranges from 3.1 to 5.6 mA from a 1.8 V supply voltage. The chip occupies an area of 0.71 mm2 including pads.-

Keywords:

- reconfigurable,

- passive mixer,

- multi-standard,

- current-commutating,

- receivers,

- CMOS

-

References

[1] Lin F, Mak P, Martins R. Wideband receivers: design challenges, tradeoffs and state-of-the-art. Circuits and Systems Magazine, 2015, 15(1): 12 doi: 10.1109/MCAS.2014.2385571[2] Murphy D, Mikhemar M, Mirzaei A, et al. Advances in the design of wideband receivers. IEEE Custom Integrated Circuits Conference (CICC), 2013: 1 http://cn.bing.com/academic/profile?id=1976640284&encoded=0&v=paper_preview&mkt=zh-cn[3] Abidi A. The path to SDR receiver. IEEE J Solid-State Circuits, 2007, 42(5): 954 doi: 10.1109/JSSC.2007.894307[4] Chen R, Hashemi H. A 0.5-to-3 GHz software-defined radio receiver using discrete-time RF signal processing. IEEE J Solid State Circuits, 2014, 49 (5): 1097 doi: 10.1109/JSSC.2014.2303791[5] El-Nozahi M, Sánchez-Sinencio E, Entesari K. Power-aware multiband multistandard CMOS receiver system-level budgeting. IEEE Trans Circuits Syst-Ⅱ, 2009, 56(7): 570 http://cn.bing.com/academic/profile?id=2104191916&encoded=0&v=paper_preview&mkt=zh-cn[6] Bao Kuan, Fan Xiangning, Li Wei, et al. A wideband current-commutating passive mixer for multi-standard receivers in a 0.18μm CMOS. Journal of Semiconductors, 2013, 34(1): 015003 doi: 10.1088/1674-4926/34/1/015003[7] Wu Chenjian, Li Zhiqun, Sun Ge. A low voltage low power up-conversion mixer for WSN application. Journal of Semiconductors, 2014, 35(4): 045006 doi: 10.1088/1674-4926/35/4/045006[8] Tang Xusheng, Wang Xiaoyu, Yang Jiang, et al. A high linearity dual-band mixer for IMT-A and UWB systems. Journal of Semiconductors, 2014, 35(11): 115006 doi: 10.1088/1674-4926/35/11/115006[9] Huang Y, Li W, Hu S, et al. A High-linearity WCDMA/GSM reconfigurable transceiver in 0.13μm CMOS. IEEE Trans Microw Theory Tech, 2013, 61(1): 204 doi: 10.1109/TMTT.2012.2222913[10] Wang X, Sturm J, Yan N, et al. 0.6-3 GHz wideband receiver RF front-end with a feedforward noise and distortion cancellation resistive-feedback LNA. IEEE Trans Microw Theory Tech, 2012, 60(2): 387 doi: 10.1109/TMTT.2011.2176138[11] Liempd B V, Borremans J, Martens E, et al. A 0.9 V 0.4-6 GHz harmonic recombination SDR receiver in 28 nm CMOS with HR3/HR5 andⅡP2 calibration. IEEE J Solid State Circuits, 2014, 49(8): 1815 doi: 10.1109/JSSC.2014.2321148[12] Brandolini M, Rossi P, Manstretta D, et al. Toward multistandard mobile terminals-fully integrated receivers requirements and architectures. IEEE Trans Microw Theory Tech, 2005, 53(3): 1026 doi: 10.1109/TMTT.2005.843505[13] Poobuaphen N, Chen W, Boos Z, et al. A 1.5-V, 0.7-2.5 GHz CMOS quadrature demodulator for multiband direct-conversion receiver. IEEE J Solid-State Circuits, 2007, 42(8): 1669 doi: 10.1109/JSSC.2007.900294[14] Najam Muhammad Amin, Wang Zhigong, Li Zhiqun. An I/Q mixer with an integrated differential quadrature all-pass filter for on-chip quadrature LO signal generation. Journal of Semiconductors, 2015, 36(5): 055001 doi: 10.1088/1674-4926/36/5/055001[15] Xu Jian, Zhou Zheng, Wu Yiqiang, et al. A high linearity current mode second IF CMOS mixer for a DRM/DAB receiver. Journal of Semiconductors, 2015, 36(5): 055002 doi: 10.1088/1674-4926/36/5/055002[16] Kim N, Aparin V, Larson L E. A resistively degenerated wideband CMOS passive mixer with low noise figure and highⅡP2. IEEE Trans Microw Theory Tech, 2010, 58(4): 820 doi: 10.1109/TMTT.2010.2042644[17] Manstretta D, Brandolini M, Svelto F. Second-order intermodulation mechanisms in CMOS downconverters. IEEE J Solid-State Circuits, 2003, 38(3): 394 doi: 10.1109/JSSC.2002.808310[18] Liu R, Guo G, Yan Y. High linearity current communicating passive mixer employing a simple resistor bias. Journal of Semiconductors, 2013, 34(3): 035005 doi: 10.1088/1674-4926/34/3/035005[19] Le V H, Nguyen H N, Lee I Y, et al. A passive mixer for a wideband TV tuner. IEEE Trans Circuits SystⅡ, 2011, 58(7): 398 http://cn.bing.com/academic/profile?id=2168835075&encoded=0&v=paper_preview&mkt=zh-cn -

Proportional views

DownLoad:

DownLoad: