| Citation: |

Lintao Liu, Yuhan Gao, Jun Deng. Design and implementation of a reconfigurable mixed-signal SoC based on field programmable analog arrays[J]. Journal of Semiconductors, 2017, 38(11): 115001. doi: 10.1088/1674-4926/38/11/115001

****

L T Liu, Y H Gao, J Deng. Design and implementation of a reconfigurable mixed-signal SoC based on field programmable analog arrays[J]. J. Semicond., 2017, 38(11): 115001. doi: 10.1088/1674-4926/38/11/115001.

|

Design and implementation of a reconfigurable mixed-signal SoC based on field programmable analog arrays

DOI: 10.1088/1674-4926/38/11/115001

More Information

-

Abstract

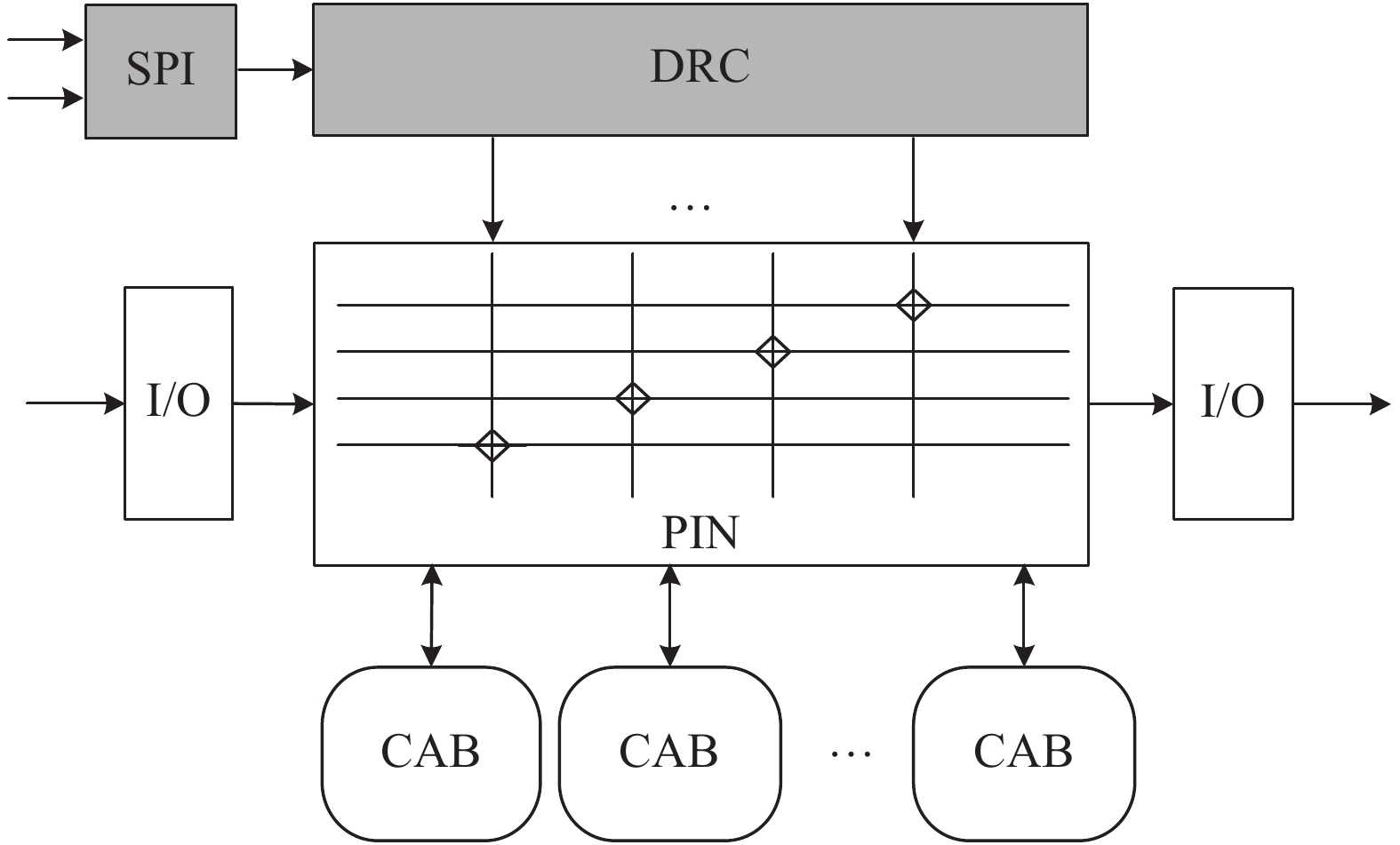

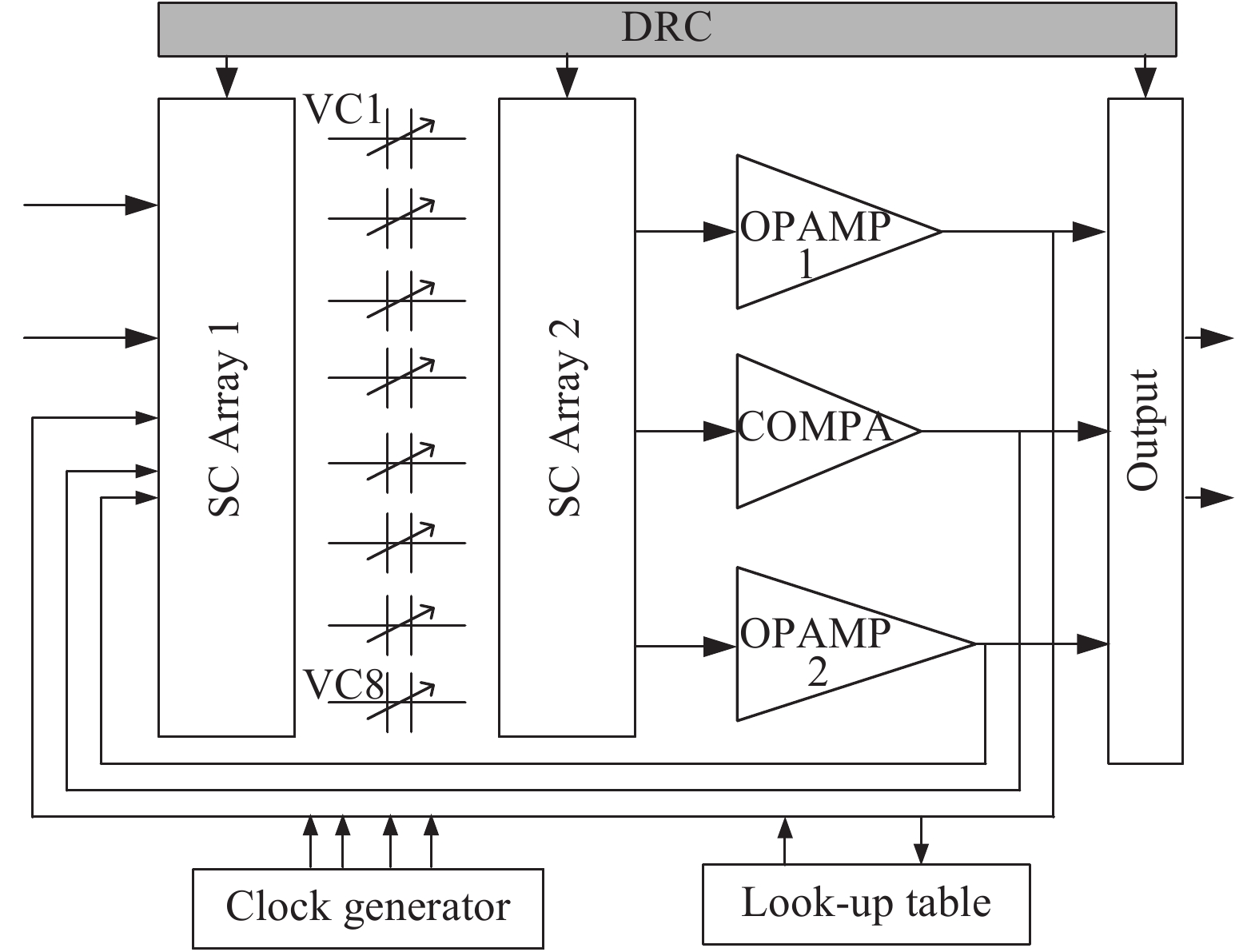

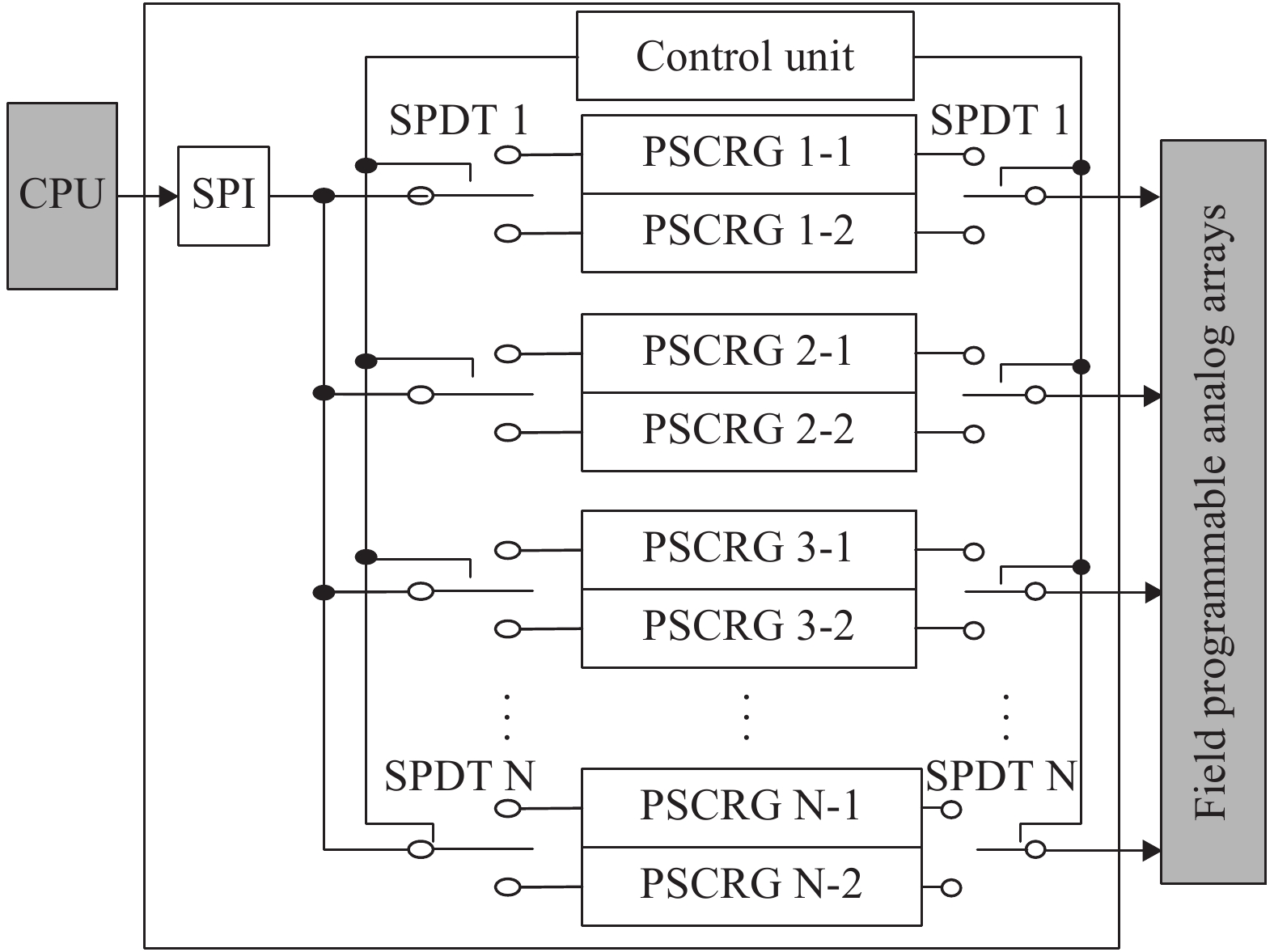

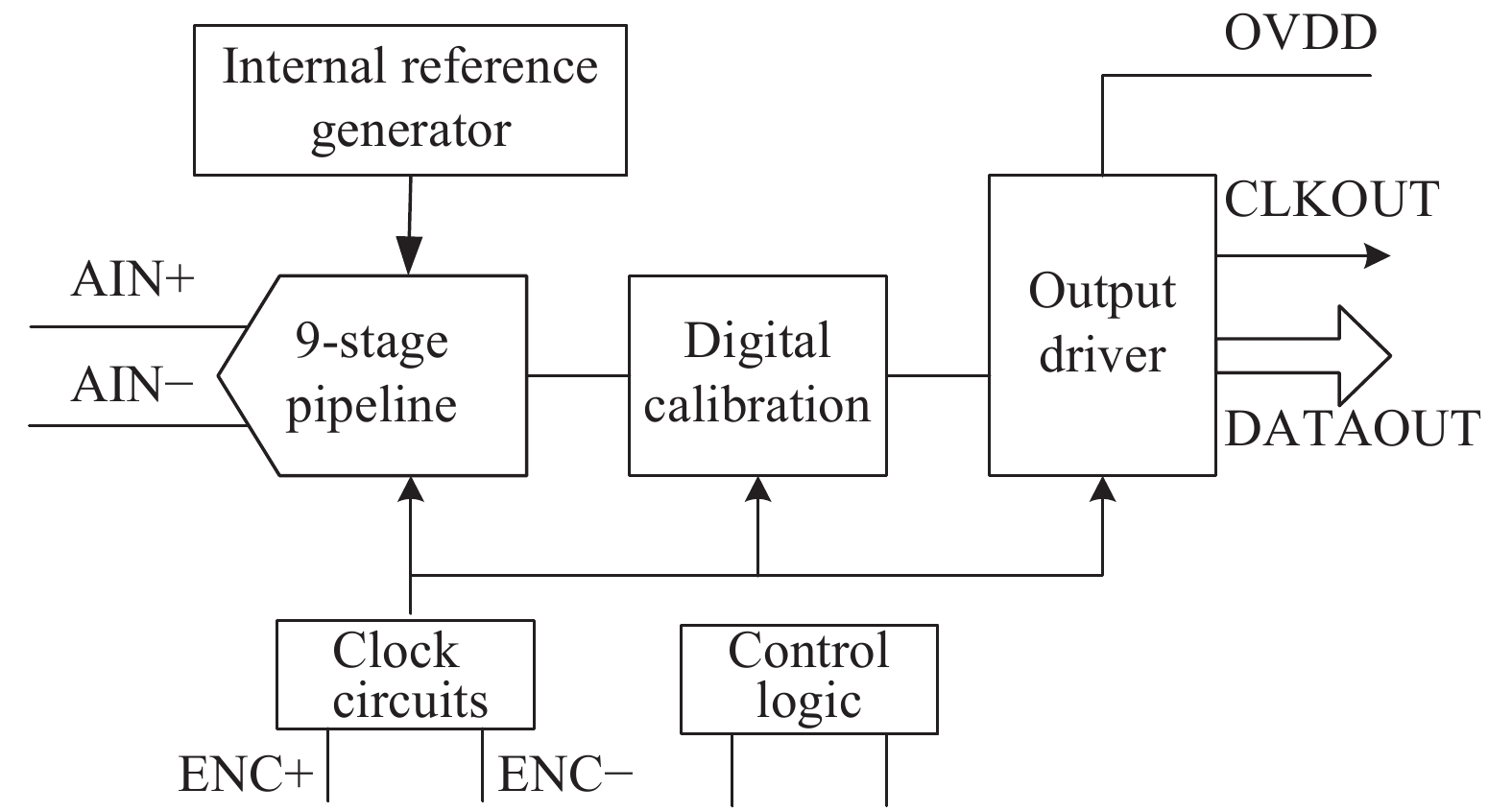

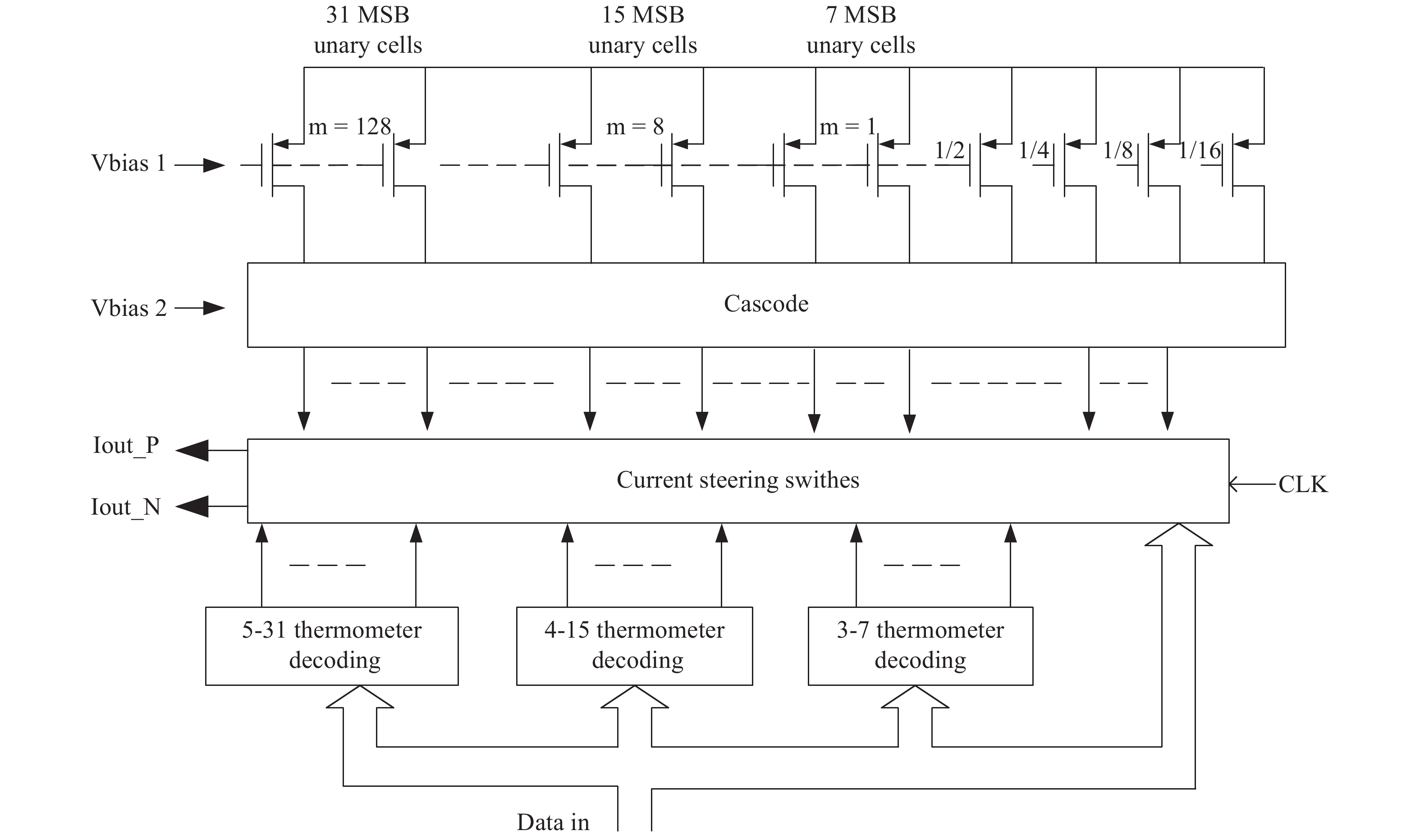

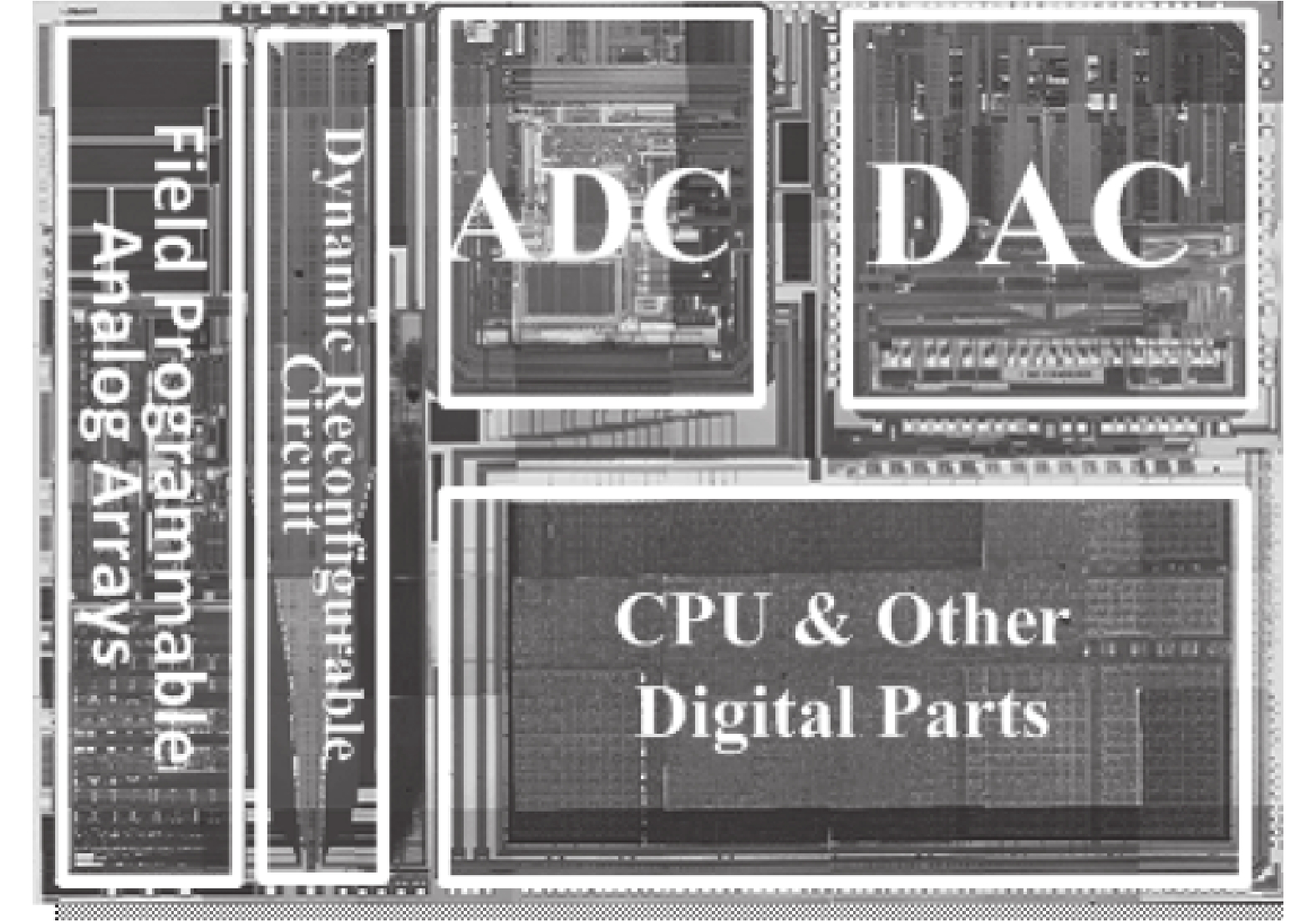

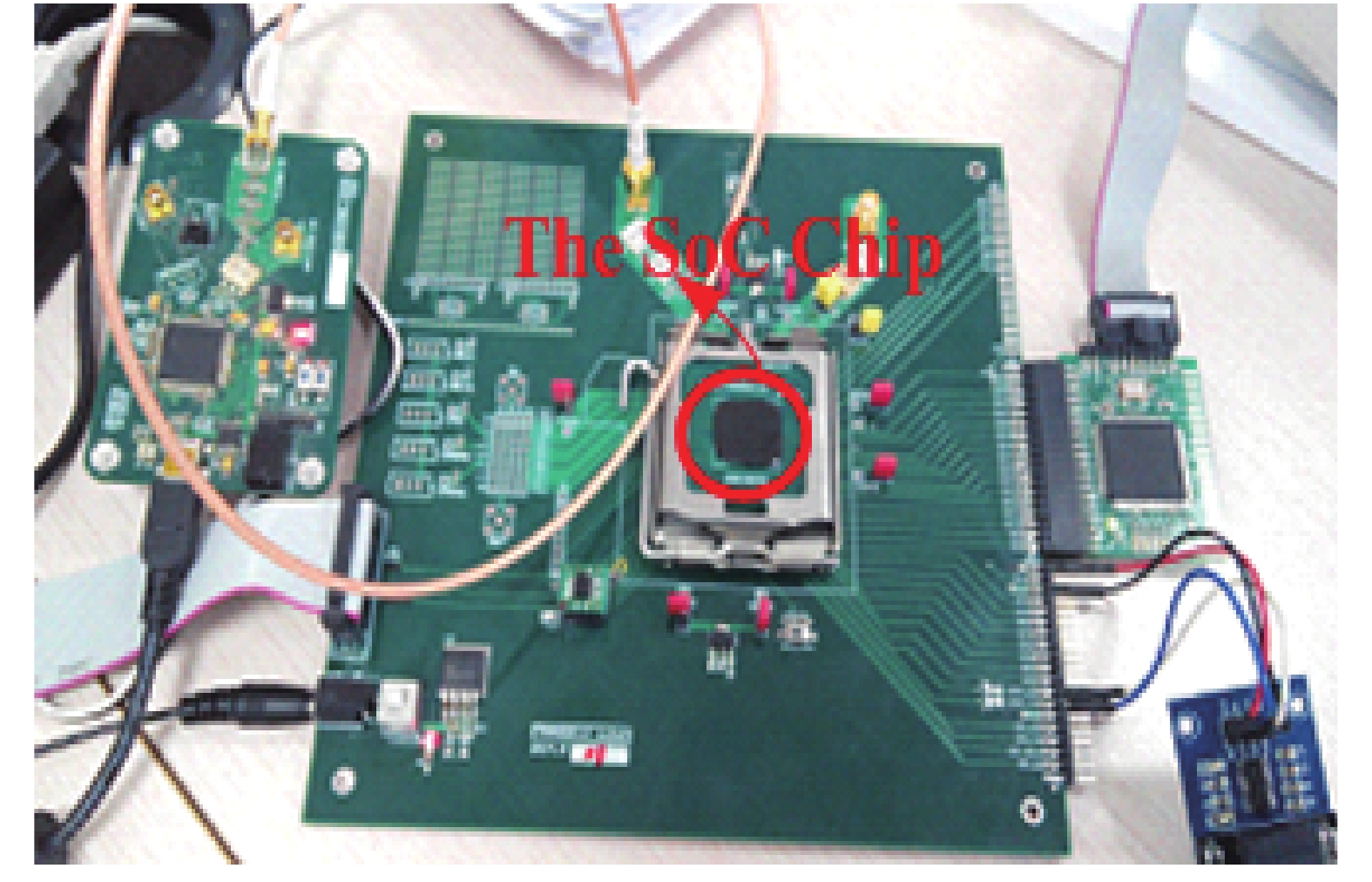

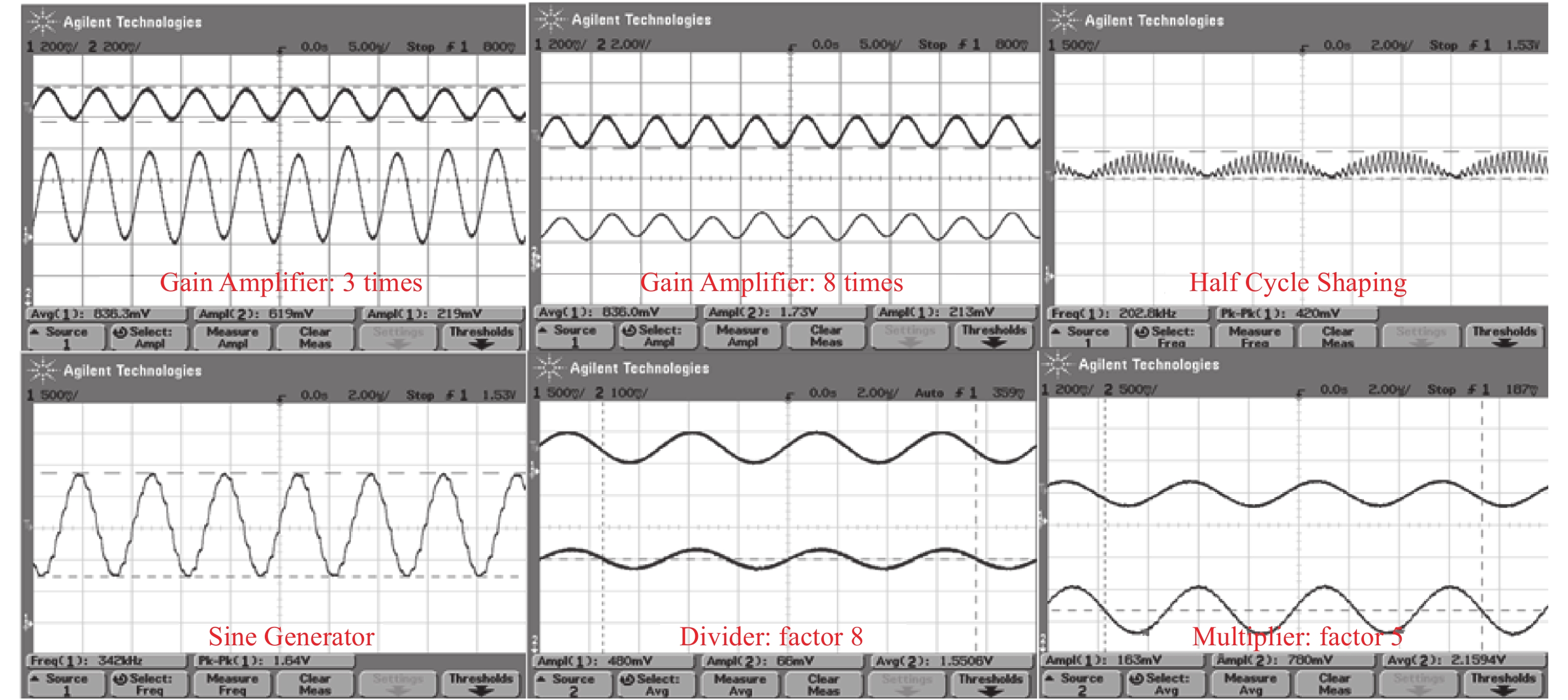

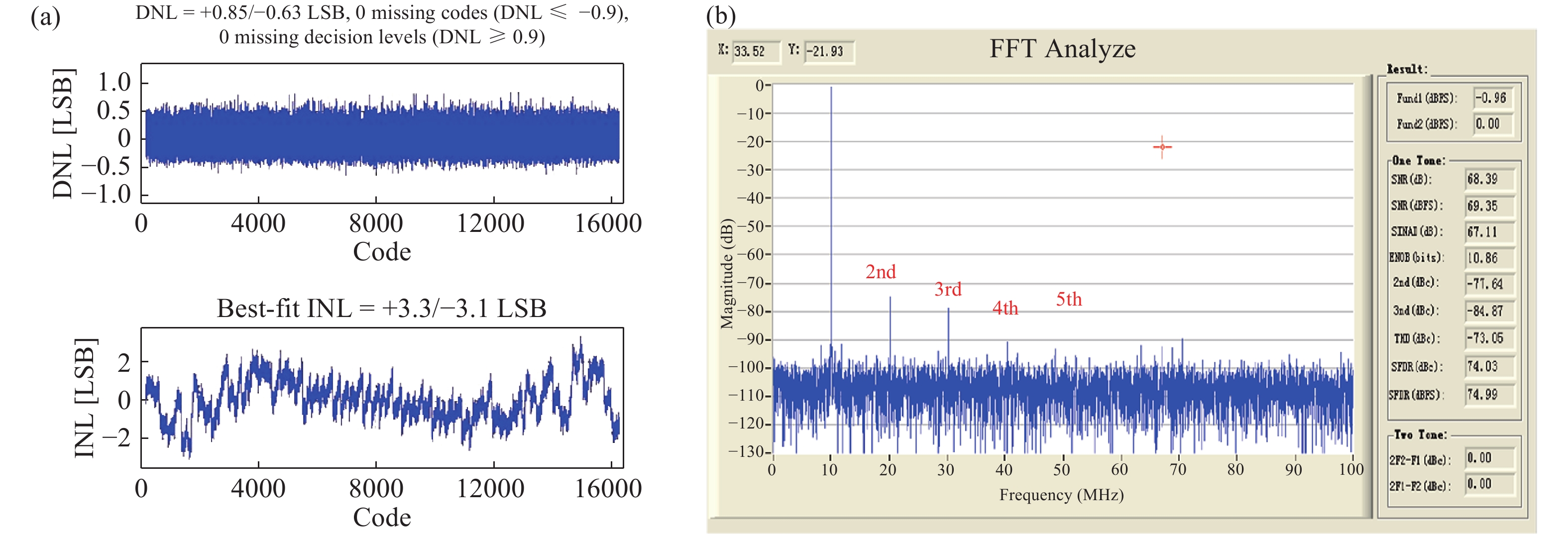

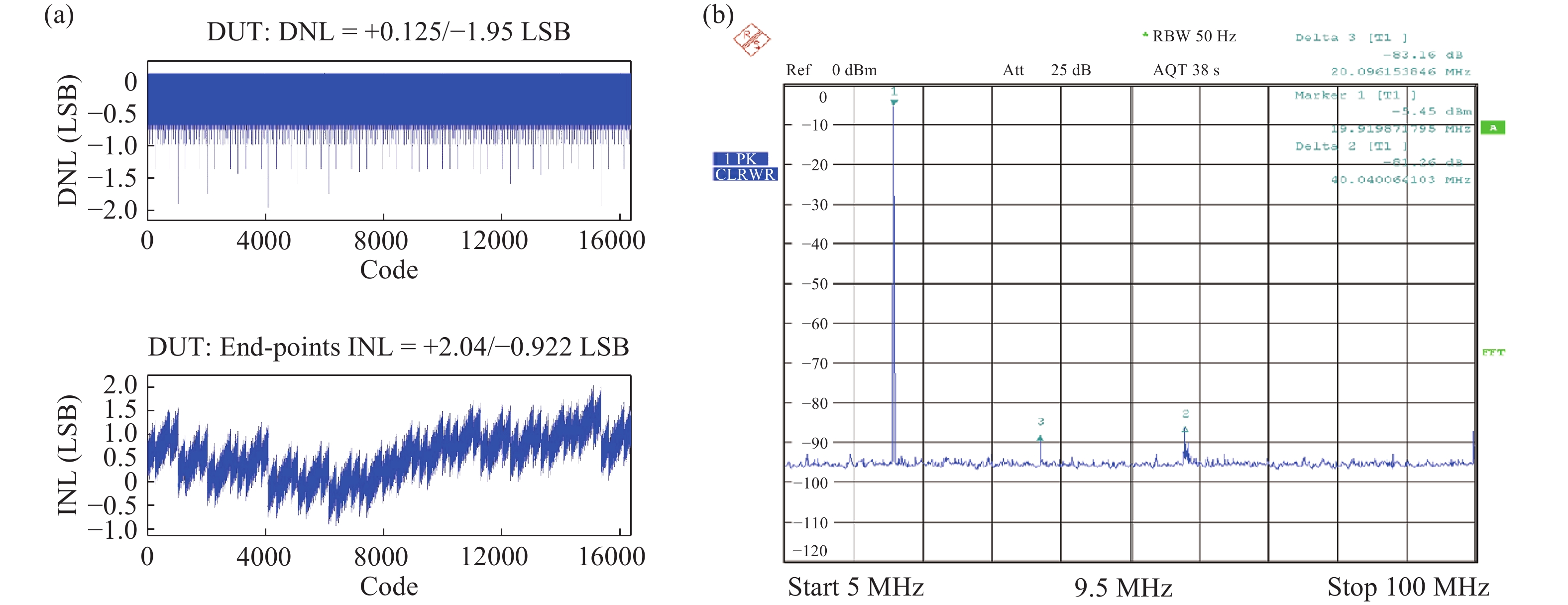

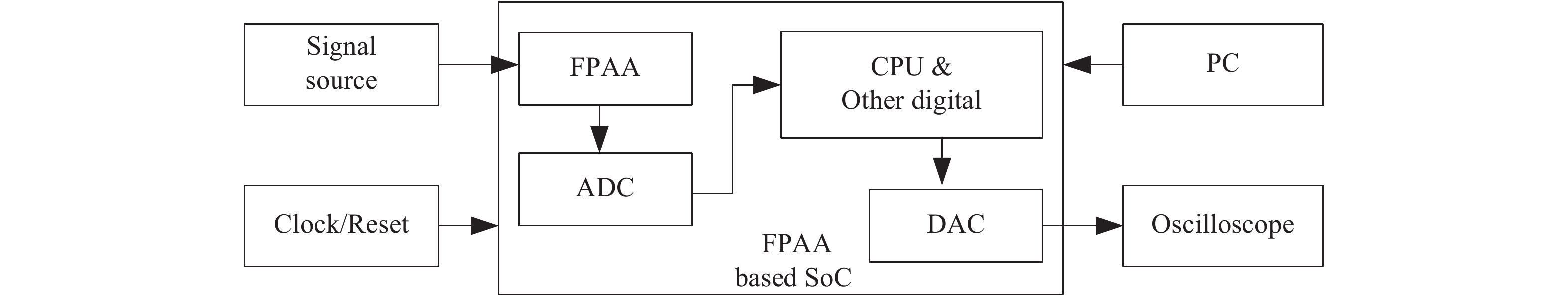

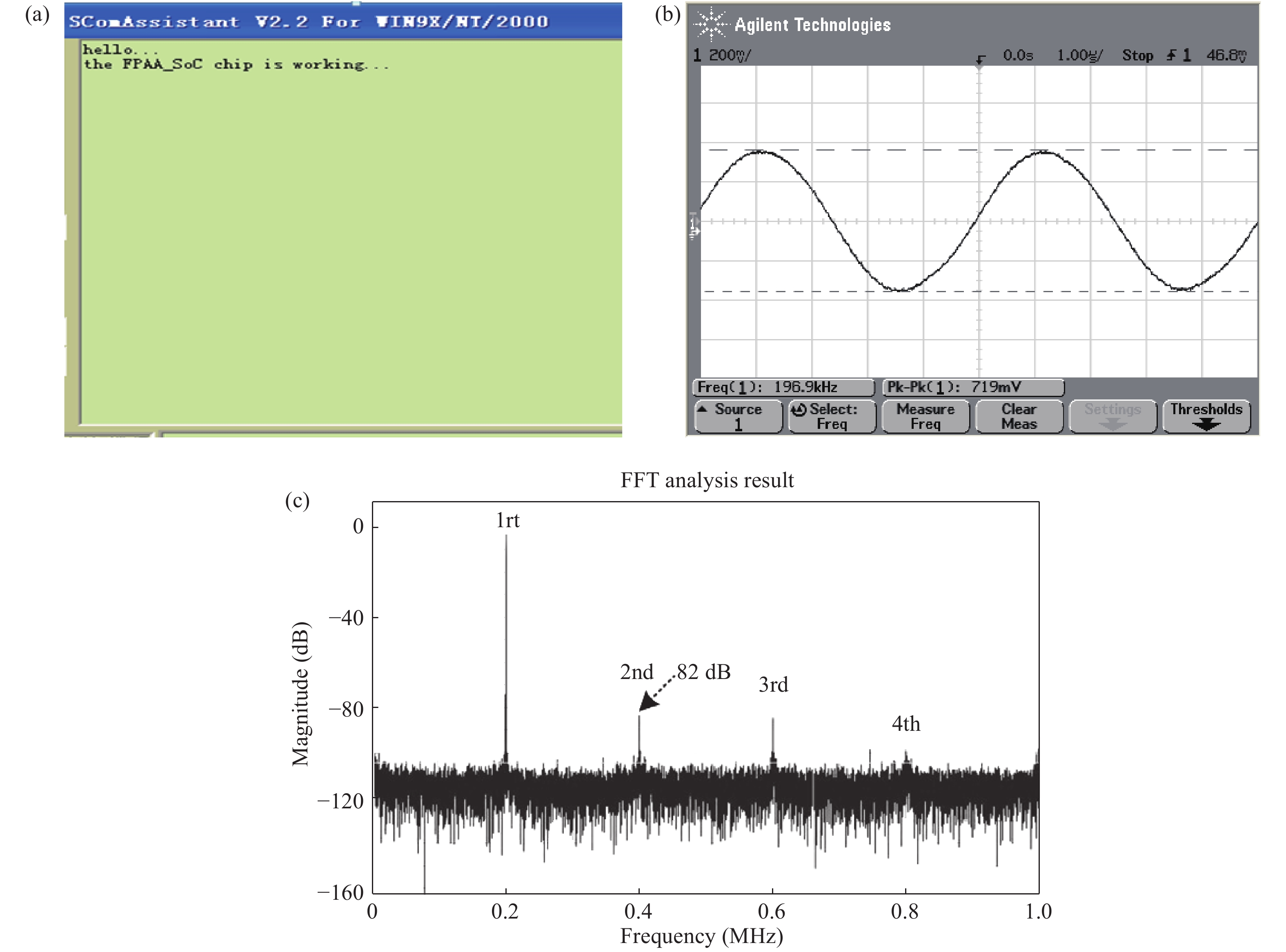

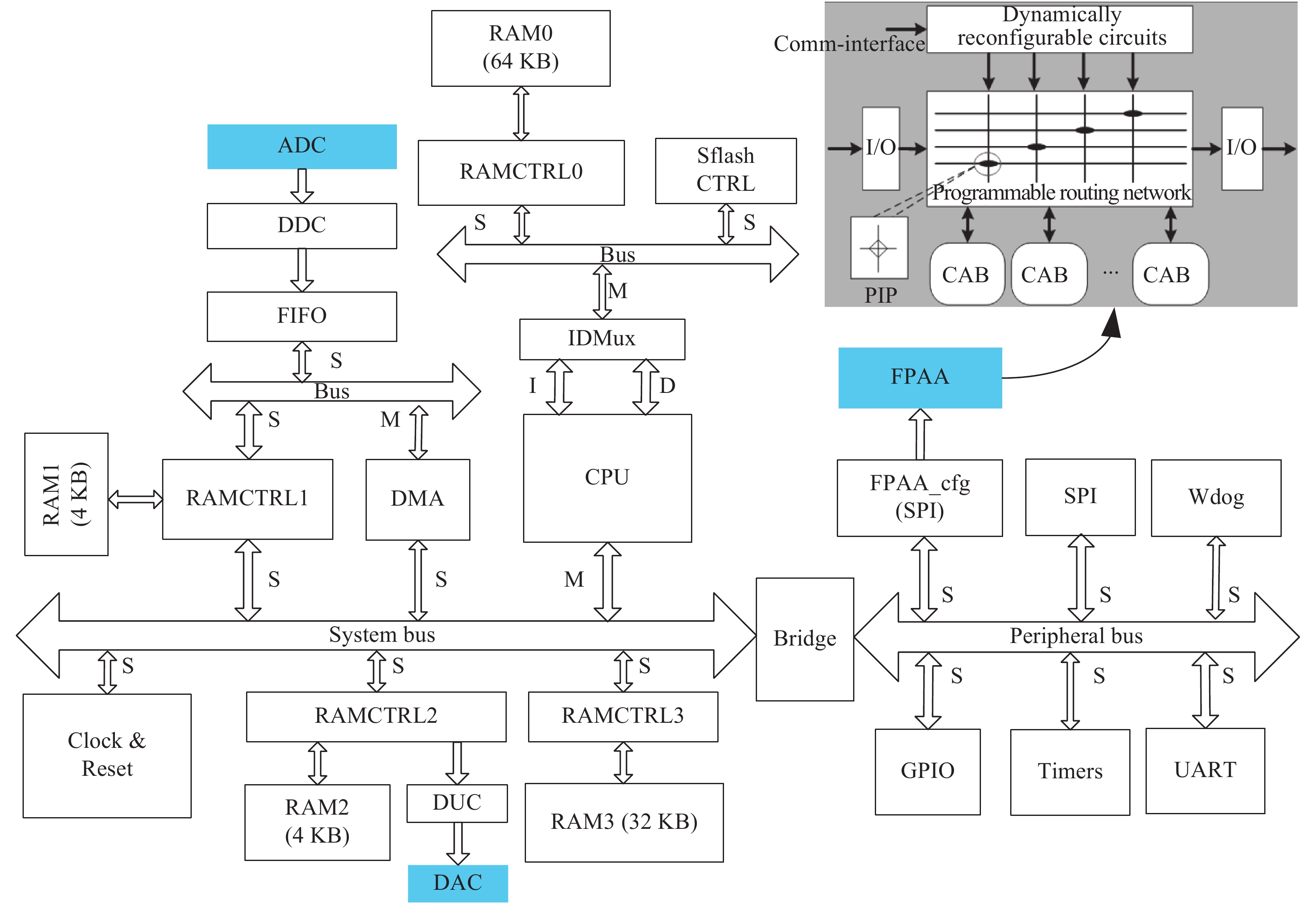

This work presents a reconfigurable mixed-signal system-on-chip (SoC), which integrates switched-capacitor-based field programmable analog arrays (FPAA), analog-to-digital converter (ADC), digital-to-analog converter, digital down converter , digital up converter, 32-bit reduced instruction-set computer central processing unit (CPU) and other digital IPs on a single chip with 0.18 μm CMOS technology. The FPAA intellectual property could be reconfigured as different function circuits, such as gain amplifier, divider, sine generator, and so on. This single-chip integrated mixed-signal system is a complete modern signal processing system, occupying a die area of 7 × 8 mm 2 and consuming 719 mW with a clock frequency of 150 MHz for CPU and 200 MHz for ADC/DAC. This SoC chip can help customers to shorten design cycles, save board area, reduce the system power consumption and depress the system integration risk, which would afford a big prospect of application for wireless communication.-

Keywords:

- reconfigurable,

- mixed-signal,

- SoC,

- FPAA

-

References

[1] George S, Kim S, Shah S, et al. A programmable and configurable mixed-mode FPAA SoC. IEEE Trans Very Large Scale Integr (VLSI) Syst, 2016, 24: 2253 doi: 10.1109/TVLSI.2015.2504119[2] Schlottmann C, Nease S, Shapero S, et al. A mixed-mode FPAA SoC for analog-enhanced signal processing. Proceedings of the IEEE 2012 Custom Integrated Circuits Conference, 2012[3] Hasler J, Kim S, Sahil S, et al. Transforming mixed-signal circuits class through SoC FPAA IC, PCB, and toolset. 2016 11th European Workshop on Microelectronics Education (EWME), 2016[4] Koneru S, Lee E K F, Chu C. A Flexible 2-D Switched-Capacitor FPAA Architecture and Its Mapping Algorithm. Proc CS, 1999, 1: 296 doi: 10.1109/MWSCAS.1999.867265[5] It’utuk H, Kang S M. A field-programmable analog array (FPAA) using switched-capacitor techniques. 1996 IEEE International Symposium on Circuits and Systems: Circuits and Systems Connecting the World, 1996 doi: 10.1109/ISCAS.1996.541896[6] Anderson D, Marcjan C, Bersch D, et al. A field programmable analog array and its application. Proceedings of CICC 97 - Custom Integrated Circuits Conference, 1997 doi: 10.1109/CICC.1997.606688[7] Collins M, Hasler J, George S. Analog systems education: an integrated toolset and FPAA SoC boards. 2015 IEEE International Conference on Microelectronics Systems Education (MSE), 2015 doi: 10.1109/MSE.2015.7160011[8] Deng J, Tan H Y, Liu L T, et al. Research of a mixed-signal programmable SoC based on FPAA. Pro ICMIAC, 2014 doi: 10.4028/wwww.scientific.net/AMM[9] Deng J, Huang X, Liu L T, et al. Design and implementation of a mixed SoC for IF digital software radio receiver. Proc ICACI, 2013 doi: 10.1109/ICACI.2013.6748513[10] Lee E, Gulak G. A CMOS field programmable analog array. IEEE J Solid-State Circuits, 1991, 26: 1860 doi: 10.1109/4.104162[11] Lee E, Gulak G. A Transconductor Based Field Programmable Analog Array. ISSCC Digest of Technical Papers, 1995: 198 doi: 10.1109/ISSCC.1995.535521[12] Pierzchala E, Perkowski M, Van Halen P, et al. Current-mode arnplifier/integrator for a field programmable analog array. ISSCC Digest of Technical Papers, 1995: 196 doi: 10.1109/ISSCC.1995.535520[13] Premont C, Grisel R, Abouchi N, et al. A current conveyor based field-programmable analog array. Analog Integrated Circuits and Signal Processing, 1998, 17: 105 doi: 10.1023/A:1008202016480[14] Embabi S, Quan X, Oki N, et al. A current-mode rased field-programmable analog array for signal processing applications. Analog Integrated Circuits and Signal Processing, 1998, 17: 125 doi: 10.1023/A:1008254100550[15] Li L, Xu M Y, Huang X F, et al. A 12 bit 500 MS/S SHA-less ADC in 0.18 μm CMOS. 2016 IEEE International Nanoelectronics Conference (INEC), 2016: 1 doi: 10.1109/INEC.2016.7589282[16] Murmann B, Boser B. A 12-bit 75-MS/s pipelined ADC using open-loop residue amplification. IEEE J Solid-State Circuits, 2003, 38(2): 2004 doi: 10.1109/JSSC.2003.819167[17] Brandolini M, Shin Y J, Raviprakash K, et al. A 5 GS/s 150 mW 10 b SHA-less pipelined/SAR hybrid ADC for direct-sampling systems in 28 nm CMOS. IEEE J Solid-State Circuits, 2015, 50: 2922 doi: 10.1109/JSSC.2015.2464684[18] Mercer D A. Low-power approaches to high-speed current-steering digital-to-analog converters in 0.18-m CMOS. IEEE J Solid-State Circuits, 2007, 42(8): 1688 doi: 10.1109/JSSC.2007.900279[19] Chen T, Gielen G G E. The analysis and improvement of a current-steering DACs dynamic SFDR—The cell-dependent delay differences. IEEE Trans Circuits Syst, 2006, 53(1): 3 doi: 10.1109/TCSI.2005.854409[20] Müller S, Hanay O, Negra R. Current-steering DAC linearisation by impedance transformation. 2016 IEEE Nordic Circuits and Systems Conference (NORCAS), 2016,: 1 doi: 10.1109/NORCHIP.2016.7792900[21] Liu M L, Zhu Z M Yang Y T. A high-SFDR 14-bit 500 MS/s current-steering D/A converter in 0.18 m CMOS. IEEE Trans Very Large Scale Integr (VLSI) Syst, 2015, 23: 3148 doi: 10.1109/TVLSI.2014.2386332[22] Chou F T, Hung C C. Glitch energy reduction and sfdr enhancement techniques for low-power binary-weighted current-steering DAC. IEEE Trans Very Large Scale Integr (VLSI) Syst, 2016, 24: 2407 doi: 10.1109/TVLSI.2015.2503727 -

Proportional views

DownLoad:

DownLoad: