| Citation: |

Guangyao Zhou, Shunli Ma, Ning Li, Fan Ye, Junyan Ren. A monolithic K-band phase-locked loop for microwave radar application[J]. Journal of Semiconductors, 2017, 38(2): 025002. doi: 10.1088/1674-4926/38/2/025002

****

G Y Zhou, S L Ma, N Li, F Ye, J Y Ren. A monolithic K-band phase-locked loop for microwave radar application[J]. J. Semicond., 2017, 38(2): 025002. doi: 10.1088/1674-4926/38/2/025002.

|

A monolithic K-band phase-locked loop for microwave radar application

DOI: 10.1088/1674-4926/38/2/025002

More Information

-

Abstract

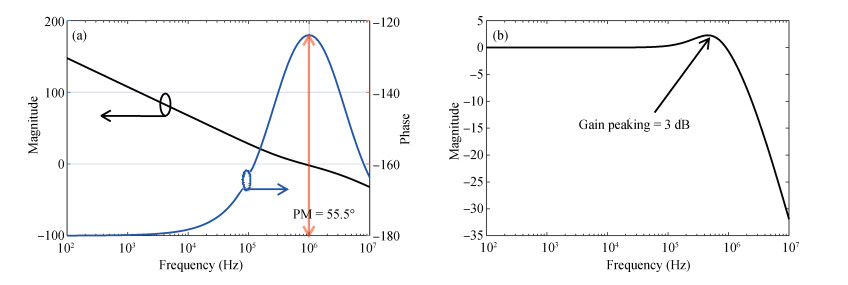

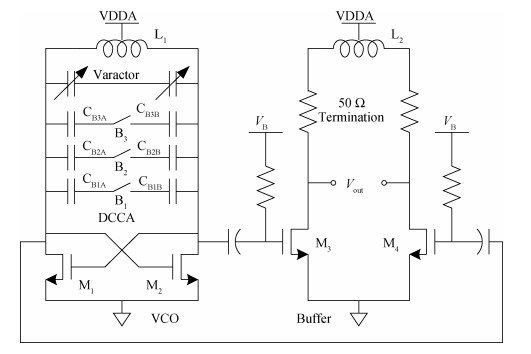

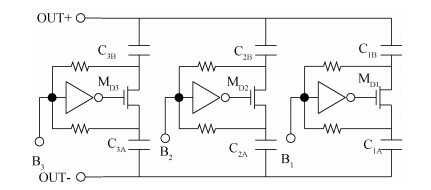

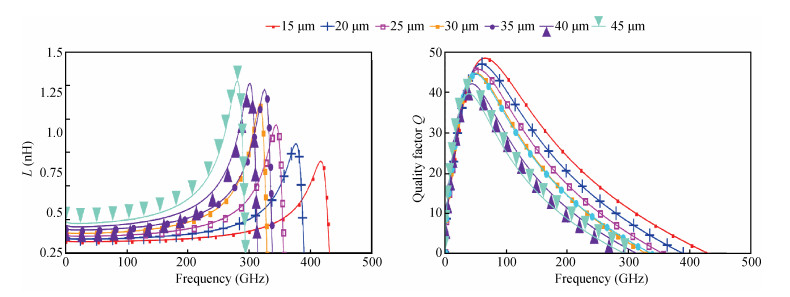

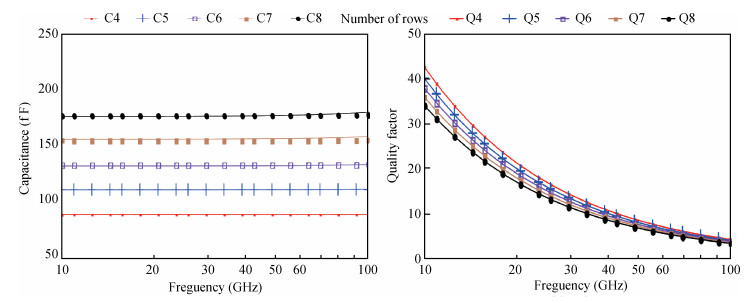

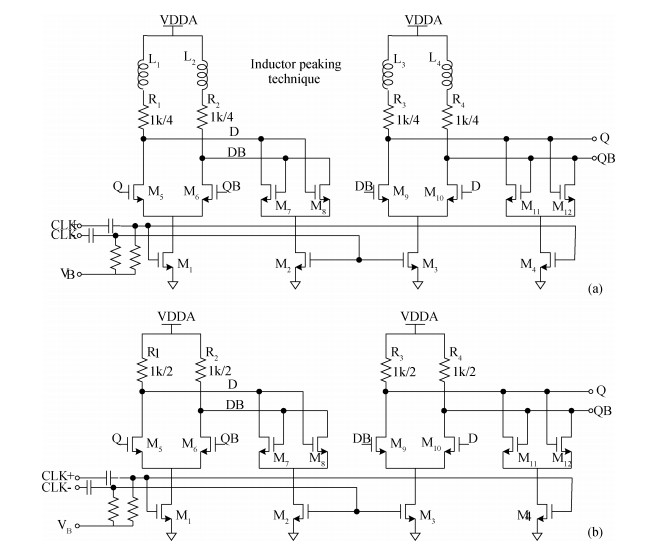

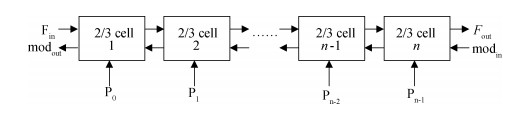

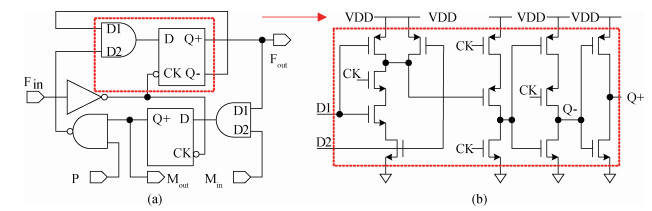

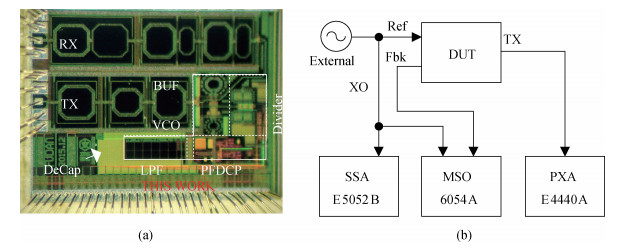

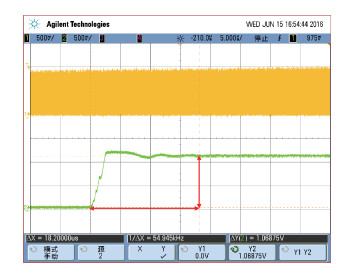

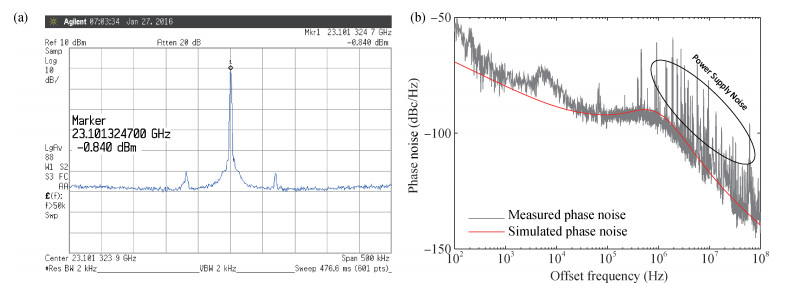

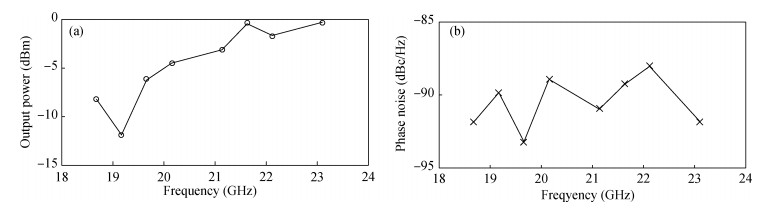

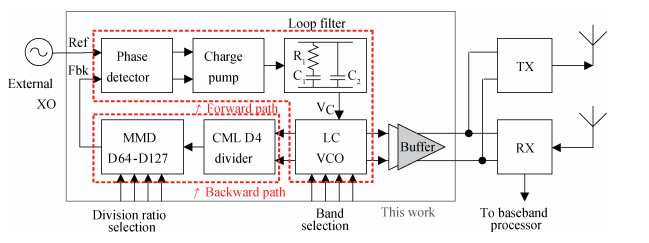

A monolithic K-band phase-locked loop (PLL) for microwave radar application is proposed and implemented in this paper. By eliminating the tail transistor and using optimized high-Q LC-tank, the proposed voltage-controlled oscillator (VCO) achieves a tuning range of 18.4 to 23.3 GHz and reduced phase noise. Two cascaded current-mode logic (CML) divide-by-two frequency prescalers are implemented to bridge the frequency gap, in which inductor peaking technique is used in the first stage to further boost allowable input frequency. Six-stage TSPC divider chain is used to provide programmable division ratio from 64 to 127, and a second-order passive loop filter with 825 kHz bandwidth is also integrated on-chip to minimize required external components. The proposed PLL needs only approximately 18.2 μs settling time, and achieves a wide tuning range from 18.4 to 23.3 GHz, with a typical output power of -0.84 dBm and phase noise of 91:92 dBc/Hz@1 MHz. The chip is implemented in TSMC 65 nm CMOS process, and occupies an area of 0.56 mm2 without pads under a 1.2 V single voltage supply.-

Keywords:

- CMOS technology,

- integrated circuits,

- phase-locked loop,

- microwave

-

References

[1] Cheng J H, Wu M H, Huang H T, et al. A K-band phase-locked loop in 0.18μm CMOS technology for vital sign detection radar. 2014 IEEE MTT-S International Microwave Workshop Series on RF and Wireless Technologies for Biomedical and Healthcare Applications (IMWS-Bio), 2014:1[2] Yeh Y L, Chang H Y. Design and analysis of a K-band low-phasenoise phase-locked loop with subharmonically injection-locked technique. IEEE Trans Ultrason, Ferroelectr, Freq Control, 2014, 61(12):1927 doi: 10.1109/TUFFC.2012.005040[3] Huang J F, Lai W C, Hsu C M. Chip design of a 24 GHz band low-power phase-locked loop using an injection frequency divider circuit and integrated system for biomedical application. 2014 International Conference on Information Science, Electronics and Electrical Engineering (ISEEE), 2014, 3:2075[4] Kashif M, Malik Z Y, Yasin M, et al. K-band PLL based frequency synthesizer. 20096th International Bhurban Conference on Applied Sciences and Technology (IBCAST), 2009:136[5] Yu X B, Han S Y, Jin Z M, et al. A class-C VCO based Σ-Δ fraction-N frequency synthesizer with AFC for 802.11ah applications. J Semicond, 2015, 36(9):095003 doi: 10.1088/1674-4926/36/9/095003[6] Li Z Q, Jiang Y W, Shu H Y, et al. A 5-GHz frequency synthesizer with AFC for low IF ZigBee transceiver applications. 2011 IEEE 9th International New Circuits and Systems Conference (NEWCAS), 2011:530[7] Gardner F M. Phase lock techniques. New Jersey:Wiley, 2005[8] Zhong B, Zhu Z M. A 0.1-1.5 GHz, low jitter, area efficient PLL in 55-nm CMOS process. J Semicond, 2016, 37(5):055004 doi: 10.1088/1674-4926/37/5/055004[9] Fei W, Yu H, Yeo K S, et al. A 60 GHz VCO with 25.8% tuning range by switching return-path in 65 nm CMOS. 2012 IEEE Asian Solid State Circuits Conference (A-SSCC), 2012:277[10] Ye Y, Tian T. A 65 nm CMOS high efficiency 50 GHz VCO with regard to the coupling effect of inductors. J Semicond, 2013, 34(7):75001 doi: 10.1088/1674-4926/34/7/075001[11] Vaucher C S, Ferencic I, Locher M, et al. A family of lowpower truly modular programmable dividers in standard 0.35-μm CMOS technology. IEEE J Solid-State Circuits, 2000, 35(7):1039 doi: 10.1109/4.848214[12] Rael J J, Abidi A A. Physical processes of phase noise in differential LC oscillators. Custom Integrated Circuits Conference, 2000:569 http://www.academia.edu/20339722/Physical_processes_of_phase_noise_in_differential_LC_oscillators[13] Ding Y P, Kennet K O. A 21-GHz 8-modulus prescaler and a 20-GHz phase-locked loop fabricated in 130-nm CMOS. IEEE J Solid-State Circuits, 2007, 42(6):1240 doi: 10.1109/JSSC.2007.897140[14] Zhou C Y, Zhang L, Yang D X, et al. A 24-GHz fully integrated phase-locked loop for 60-GHz beamforming. 2012 IEEE 11th International Conference on Solid-State and Integrated Circuit Technology (ICSICT), 2012:1[15] Kuang L X, Chi B Y, Chen L, et al. A fully-differential phaselocked loop frequency synthesizer for 60-GHz wireless communication. J Semicond, 2014, 35(12):125002 doi: 10.1088/1674-4926/35/12/125002[16] Osorio J F, Vaucher C S, Huff B, et al. A 21.7-to-27.8 GHz 2.6-degrees-rms 40 MW frequency synthesizer in 45 nm CMOS for mm-wave communication applications. 2011 IEEE International Solid-State Circuits Conference, San Francisco, CA, 2011:278 -

Proportional views

DownLoad:

DownLoad: