| Citation: |

Jihai Duan, Zhiyong Zhu, Jinli Deng, Weilin Xu. An 8 bit 1 MS/s SAR ADC with 7.72-ENOB[J]. Journal of Semiconductors, 2017, 38(8): 085005. doi: 10.1088/1674-4926/38/8/085005

****

J H Duan, Z Y Zhu, J L Deng, W L Xu. An 8 bit 1 MS/s SAR ADC with 7.72-ENOB[J]. J. Semicond., 2017, 38(8): 085005. doi: 10.1088/1674-4926/38/8/085005.

|

-

Abstract

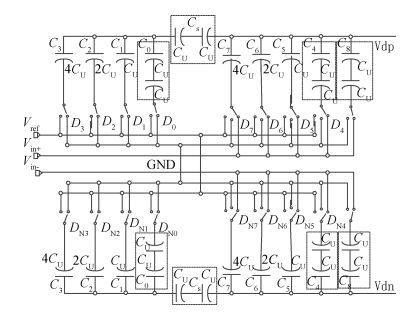

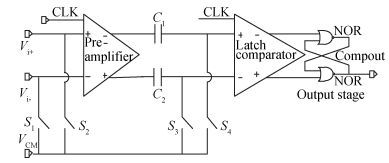

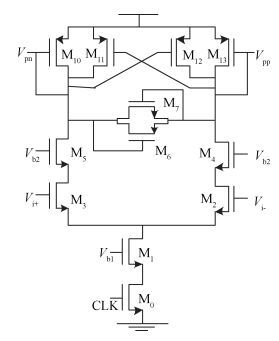

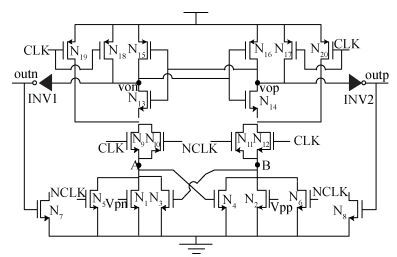

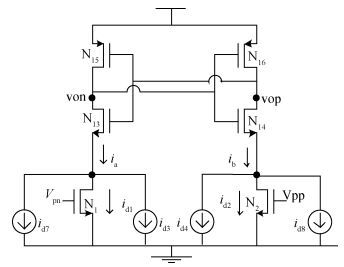

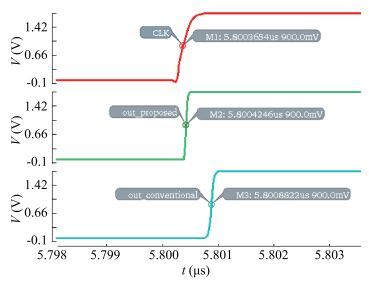

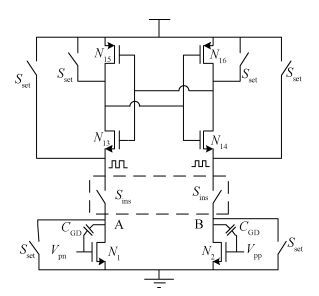

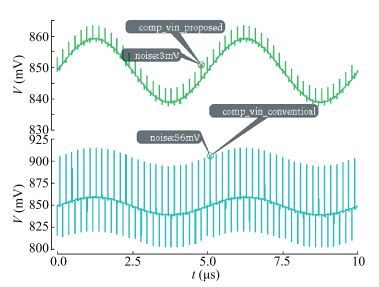

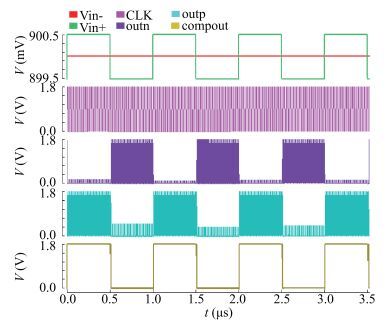

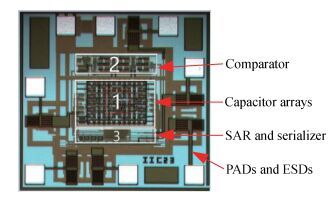

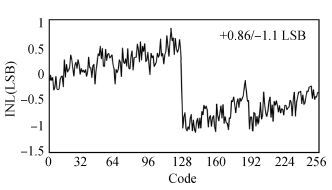

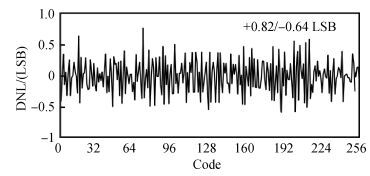

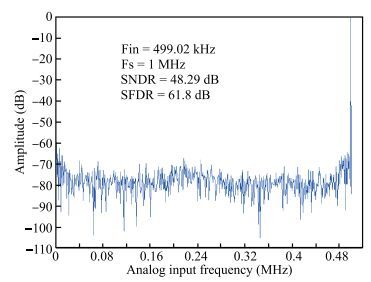

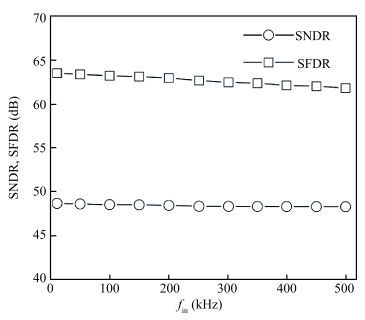

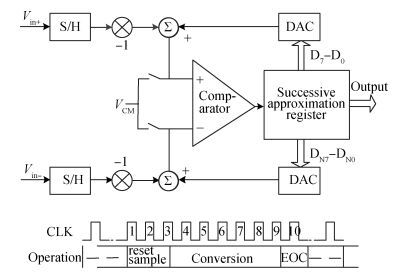

This paper presents a low power 8-bit 1 MS/s SAR ADC with 7.72-bit ENOB. Without an op-amp, an improved segmented capacitor DAC is proposed to reduce the capacitance and the chip area. A dynamic latch comparator with output offset voltage storage technology is used to improve the precision. Adding an extra positive feedback in the latch is to increase the speed. What is more, two pairs of CMOS switches are utilized to eliminate the kickback noise introduced by the latch. The proposed SAR ADC was fabricated in SMIC 0.18 μm CMOS technology. The measured results show that this design achieves an SFDR of 61.8 dB and an ENOB of 7.72 bits, and it consumes 67.5 μ W with the FOM of 312 fJ/conversion-step at 1 MS/s sample under 1.8 V power supply. -

References

[1] Ginsburg B P, Chandrakasan A P. Highly interleaved 5-bit, 250-MSample/s, 1.2-mW ADC with redundant channels in 65-nm CMOS. IEEE J Solid-State Circuits, 2008, 43(12):2641 doi: 10.1109/JSSC.2008.2006334[2] Cao T V, Aunet S, Ytterdal T. A 9-bit 50MS/s asynchronous SAR ADC in 28 nm CMOS. Norchip, 2012:1 http://ieeexplore.ieee.org/stamp/stamp.jsp?tp=&arnumber=6403105[3] Zhang H, Qin Y J, Yang S Y, et al. A 455 nW 220 fJ/conversion-step 12 bits 2 kS/s SAR ADC for portable biopotential acquisition systems. J Semicond, 2011, 32(1):79 doi: 10.1088/1674-4926/32/1/015001/pdf[4] Shen Y, Liu S, Zhu Z. A 12-bit 50MS/s zero-crossing-based two-stage pipelined SAR ADC in 0.18μm CMOS. Microelectron J, 2016, 57:26 doi: 10.1016/j.mejo.2016.09.002[5] Muratore D G, Bonizzoni E, Maloberti F. A split transconductor high-speed SAR ADC. IEEE International Symposium on Circuits and Systems, 2015:2433 http://ims.unipv.it/~franco/ConferenceProc/365.pdf[6] Liu W, Wei T, Guo P, et al. Design of a novel 12-bit 1MS/s charge redistribution SAR ADC for CZT detectors. IEEE Conference on Industrial Electronics and Applications, 2014:867 http://www.deepdyve.com/lp/institute-of-electrical-and-electronics-engineers/design-of-a-novel-12-bit-1ms-s-charge-redistribution-sar-adc-for-czt-7aU2m0IJND[7] Hu W, Liu Y T, Nguyen T, et al. An 8-bit single-ended ultra-low-power SAR ADC with a novel DAC switching method and a counter-based digital control circuitry. IEEE Trans Circuits Syst I, 2013, 60(7):1726 doi: 10.1109/TCSI.2012.2230587[8] Van d P G, Decoutere S, Donnay S. A 0.16 pJ/conversion-step 2.5 mW 1.25 GS/s 4 b ADC in a 90 nm digital CMOS process. IEEE International Solid-State Circuits Conference (ISSCC), 2006:2310[9] Das I, Sahoo M, Roy P, et al. A 45μW 13 pJ/conv-step 7.4-ENOB 40 kS/s SAR ADC for digital microfluidic biochip applications. International Symposium on VlSI Design and Test, 2014:1 http://ieeexplore.ieee.org/xpl/articleDetails.jsp?reload=true&arnumber=6881068[10] Shrivastava P, Bhat K G, Laxminidhi T, et al. A 500 kS/s 8-bit charge recycle based 2-bit per step SAR-ADC. Third International Conference on Emerging Applications of Information Technology, 2012:462 http://ieeexplore.ieee.org/xpl/articleDetails.jsp?reload=true&arnumber=6408018&contentType=Conference+Publications[11] Nazzal T B, Mahmoud S A, Shaker M O. A 200-nW 7.6-ENOB 10-KS/s SAR ADC in 90-nm CMOS for Portable Biomedical Applications. Microelectronics J, 2016, 56:81 doi: 10.1016/j.mejo.2016.08.004[12] Mahmoud S A. An 8-bit, 10 kS/s, 1. 87μW successive approximation analog to digital converter in 0. 25μm CMOS technology for ECG detection systems. Circuits Systems & Signal Processing, 2015[13] Liu L Y, Li D M, Chen L D, et al. A low power 8-bit successive approximation register A/D for a wireless body sensor node. J Semicond, 2010, 31(6):93 http://iopscience.iop.org/1674-4926/31/6/065004/pdf/1674-4926_31_6_065004.pdf -

Proportional views

DownLoad:

DownLoad: