| Citation: |

Neeraj Jain, Balwinder Raj. Analysis and performance exploration of high performance (HfO2) SOI FinFETs over the conventional (Si3N4) SOI FinFET towards analog/RF design[J]. Journal of Semiconductors, 2018, 39(12): 124002. doi: 10.1088/1674-4926/39/12/124002

****

N Jain, B Raj, Analysis and performance exploration of high performance (HfO2) SOI FinFETs over the conventional (Si3N4) SOI FinFET towards analog/RF design[J]. J. Semicond., 2018, 39(12): 124002. doi: 10.1088/1674-4926/39/12/124002.

|

Analysis and performance exploration of high performance (HfO2) SOI FinFETs over the conventional (Si3N4) SOI FinFET towards analog/RF design

DOI: 10.1088/1674-4926/39/12/124002

More Information

-

Abstract

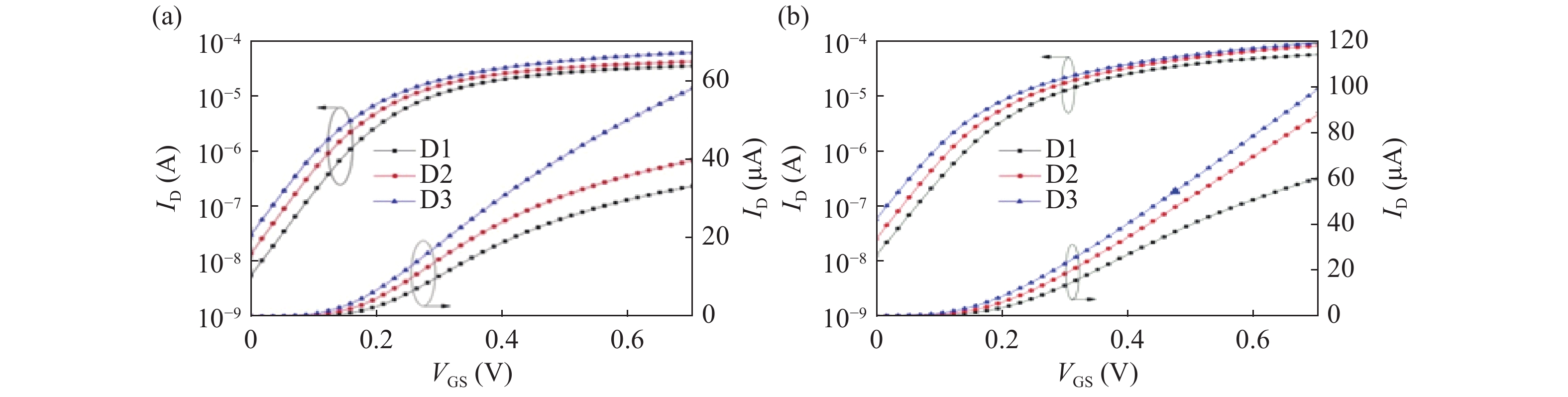

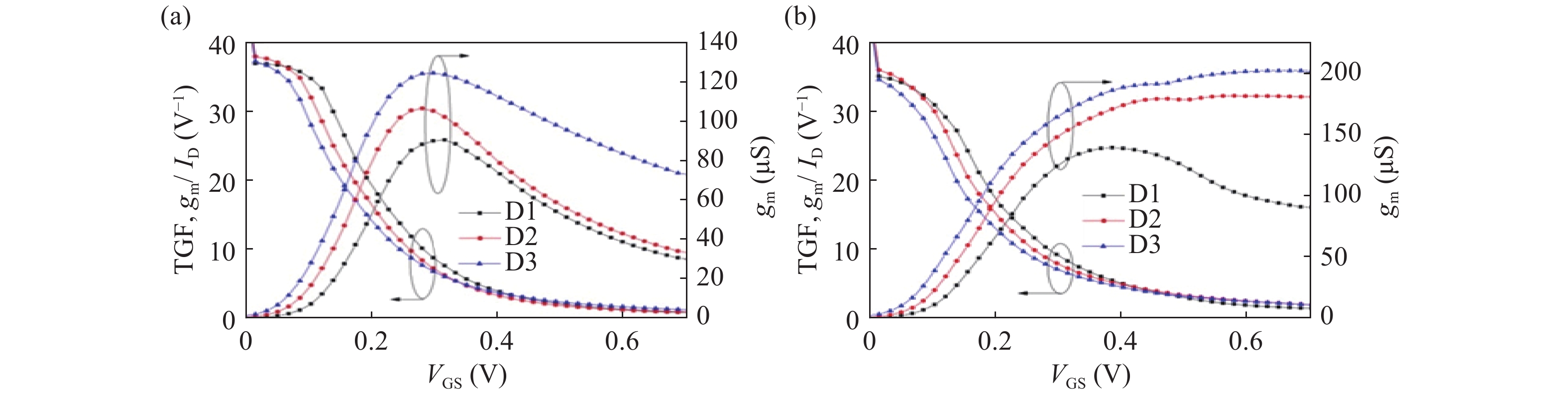

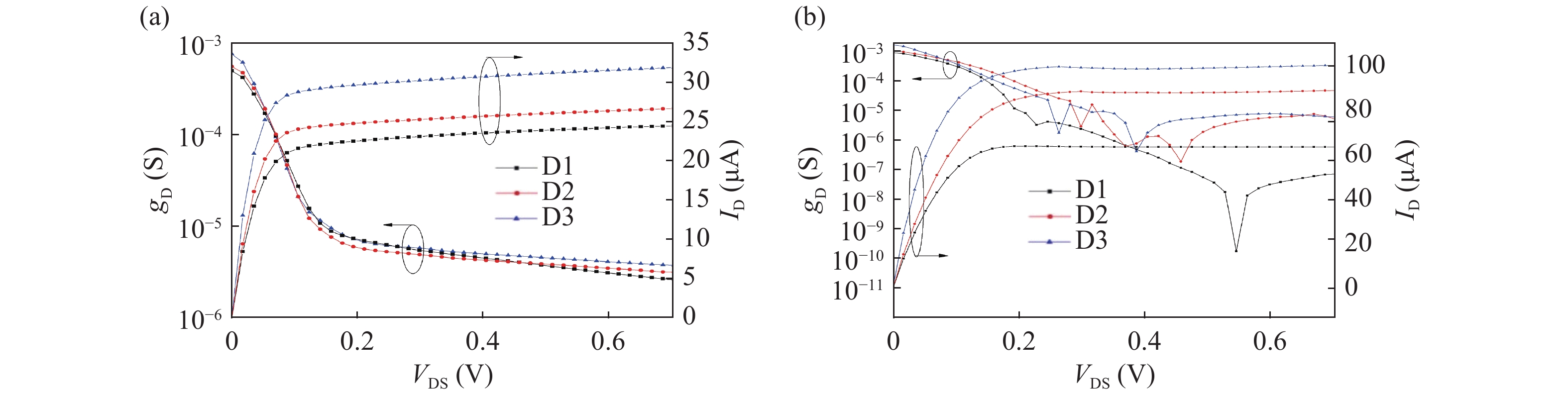

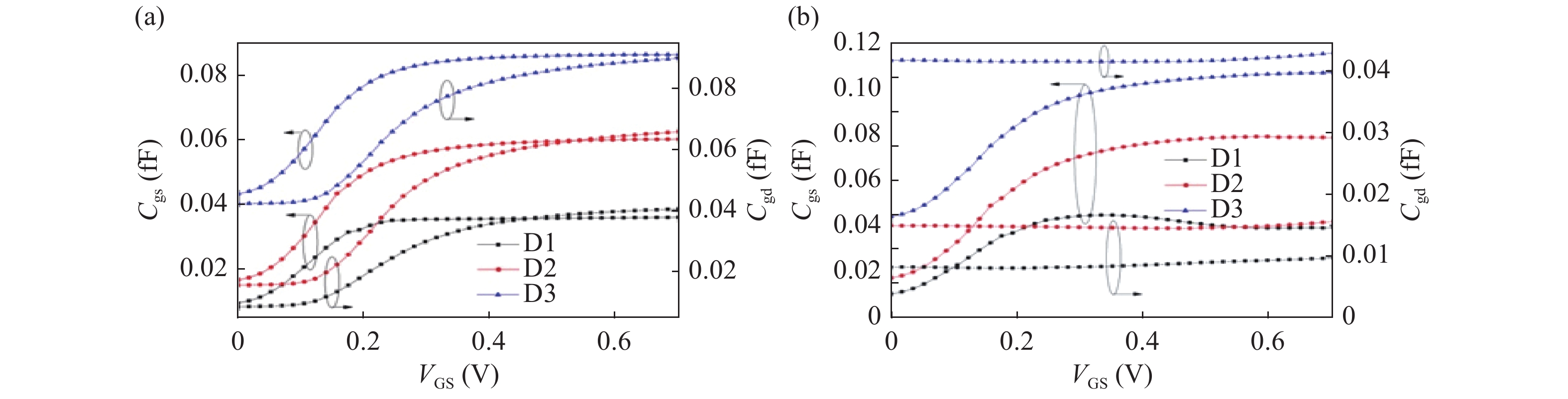

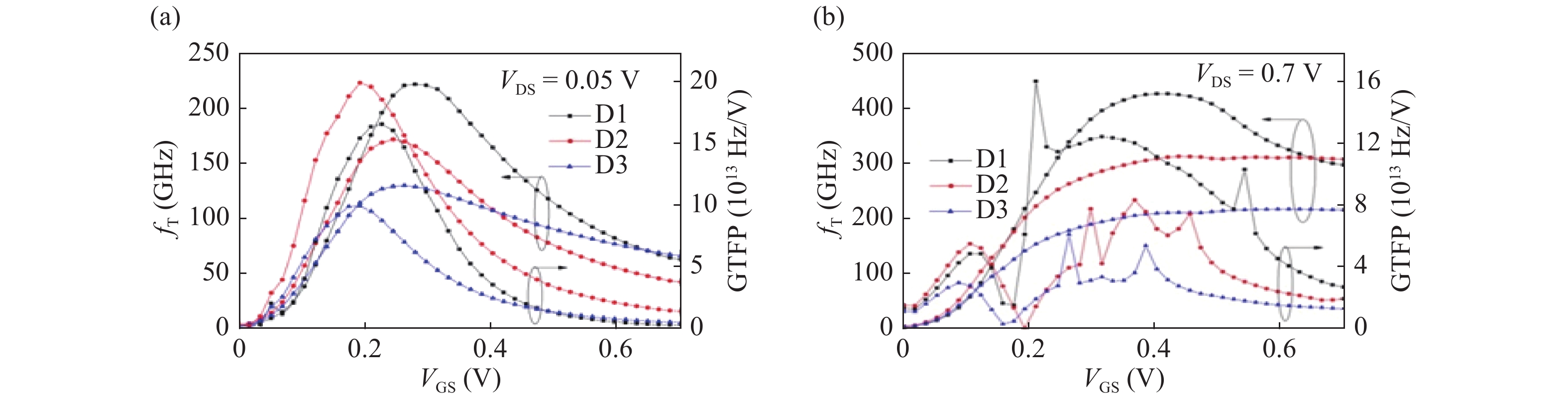

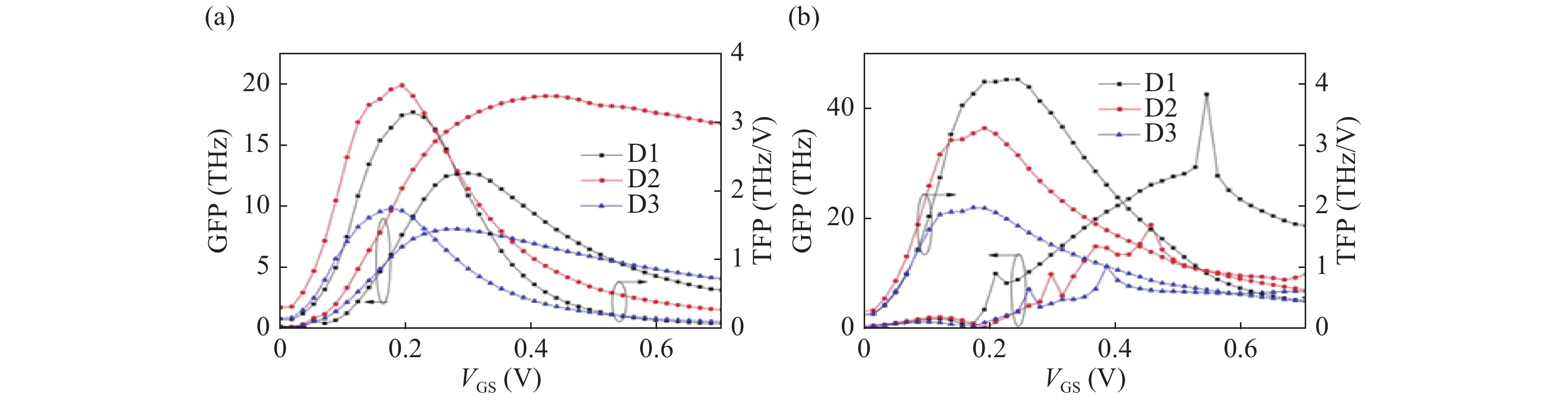

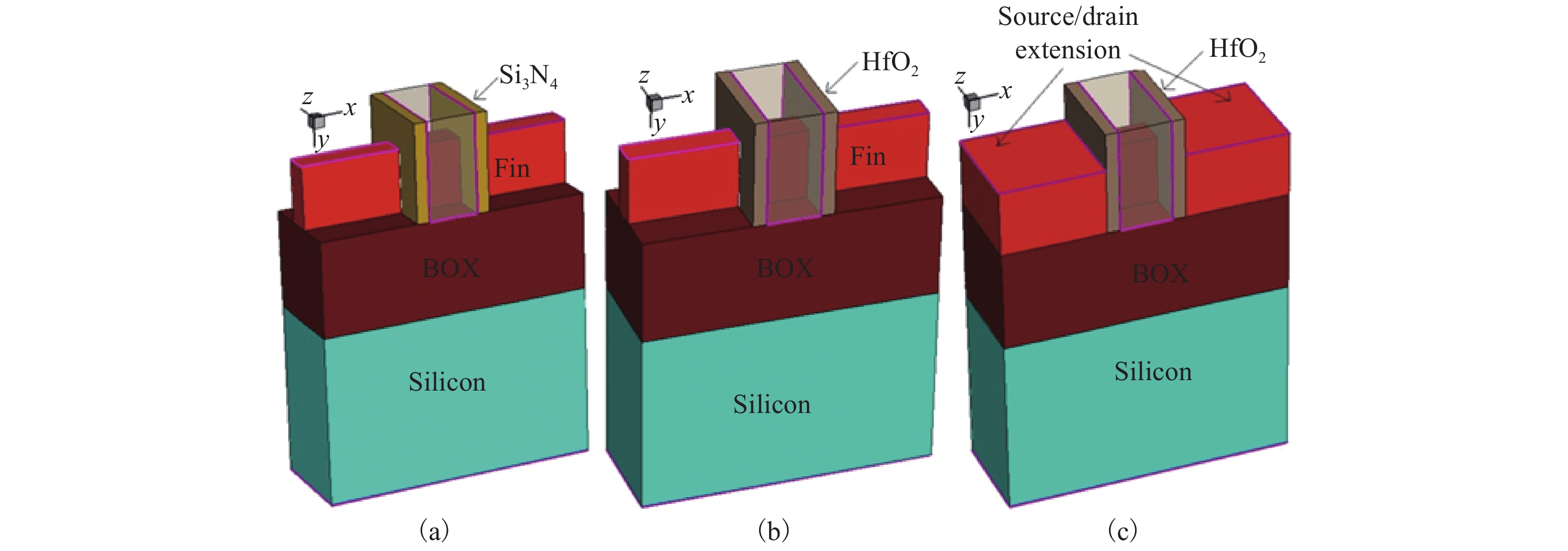

Nowadays FinFET devices have replaced the MOS devices almost in all complex integrated circuits of electronic gadgets like computer peripherals, tablets, and smartphones in portable electronics. The scaling of FinFET is ongoing and the analog/RF performance is most affected by increased SCEs (short channel effects) in sub 22 nm technology nodes. This paper explores the analog/RF performance study and analysis of high performance device-D2 (conventional HfO2 spacer SOI FinFET) and device-D3 (source/drain extended HfO2 spacer SOI FinFET) over the device-D1 (conventional Si3N4 spacer SOI FinFET) at 20 nm technology node through the 3-D (dimensional) simulation process. The major performance parameters like Ion (ON current), Ioff (OFF current), gm (transconductance), gd (output conductance), AV (intrinsic gain), SS (sub-threshold slope), TGF = gm/Id (trans-conductance generation factor), VEA (early voltage), GTFP (gain trans-conductance frequency product), TFP (tans-conductance frequency product), GFP (gain frequency product), and fT (cut-off frequency) are studied for evaluating the analog/RF performance of different flavored SOI FinFET structures. For analog performance evaluation, device-D3 and D2 give better results in terms of gm, ID (drain current) and SS parameters, and for RF performance evaluation device-D1 is better in terms of fT, GTFP, TFP, and GFP parameters both at low and high values of VDS = 0.05 V and VDS = 0.7 V respectively.-

Keywords:

- SOI FinFET,

- SCEs,

- intrinsic gain,

- trans-conductance,

- cut-off frequency

-

References

[1] Moore G E. Cramming more components onto integrated circuits. Proc IEEE, 1998, 86(1): 82 doi: 10.1109/JPROC.1998.658762[2] Veeraraghavan S, Fossum J G. Short-channel effects in SOI MOSFET’s. IEEE Trans Electron Devices, 1989, 36(3): 522 doi: 10.1109/16.19963[3] Liu Y, Ishii K, Masahara M, et al. Cross-sectional channel shape dependence of short-channel effects in fin-type double-gate metal oxide semiconductor field-effect transistors. Jpn J Appl Phys, 2004, 43(4S): 2151[4] Colinge J P. Multiple-gate SOI MOSFETs. Solid State Electron, 2004, 48(6): 897 doi: 10.1016/j.sse.2003.12.020[5] Colinge J P, Chandrakasan A. FinFETs and other multi-gate transistors. Springer, 2008[6] Bhattacharya D, Jha N K. FinFETs: from devices to architectures. Adv Electron, 2014[7] ITRS. International technology roadmap for semiconductors, 2013; Executive Summary Itrs 80[8] Fahad H M, Hu C, Hussain M M. Simulation study of a 3-D device integrating FinFET and UTBFET. IEEE Trans Electron Devices, 2015, 62(1): 83 doi: 10.1109/TED.2014.2372695[9] Hisamoto D, Lee W C, Kedzierski J, et al. FinFET-A self-aligned double-gate MOSFET scalable to 20 nm. IEEE Trans Electron Devices, 2000, 47(12): 2320 doi: 10.1109/16.887014[10] Nowak E J, Aller I, Ludwig T, et al. Turning silicon on its edge double gate CMOS/FinFET technology. Circuits Devices Mag IEEE, 2004, 20(1): 20 doi: 10.1109/MCD.2004.1263404[11] Pal P K, Kaushik B K , Dasgupta S. Investigation of symmetric dual-k spacer trigate FinFETs from delay perspective. IEEE Trans Electron Devices, 2014, 61(11): 3579 doi: 10.1109/TED.2014.2351616[12] Pal P K, Kaushik B K, Dasgupta S. High-performance and robust SRAM cell based on asymmetric dual-k spacer FinFETs. IEEE Trans Electron Devices, 2013, 60(10): 3371 doi: 10.1109/TED.2013.2278201[13] Park J T, Colinge J P, Diaz C H. Pi-gate SOI MOSFET. IEEE Electron Device Lett, 2001, 22(8): 405 doi: 10.1109/55.936358[14] Singh N, Lim F Y, Fang W W, et al. Ultra-narrow silicon nanowire gate-all-around CMOS devices: Impact of diameter, channel-orientation and low temperature on device performance. Technical Digest - International Electron Devices Meeting, 2006[15] Raj B, Saxena A K, Dasgupta S. Analytical modeling for the estimation of leakage current and subthreshold swing factor of nanoscale double gate FinFET device. Microelectron Int, 2009, 26(1): 53 doi: 10.1108/13565360910923188[16] Sharma V K, Pattanaik M, Raj B. INDEP approach for leakage reduction in nanoscale CMOS circuits. Int J Electron, 2015, 102(2): 200 doi: 10.1080/00207217.2014.896042[17] Raj B. Quantum mechanical potential modeling of FinFET toward quantum FinFET. Springer, 2013[18] Raj B, Saxena A K, Dasgupta S. A compact drain current and threshold voltage quantum mechanical analytical modeling for FinFETs. J Nanoelectron Optoelectron, 2008, 3(2): 163 doi: 10.1166/jno.2008.209[19] ITRS. ERD Working Group. International Technology Roadmap for Semiconductors, Edition - Emerging Research Devices Challenges, 2011[20] Magnone P, Mercha A, Subramanian V, et al. Matching performance of FinFET devices with fin widths down to 10 nm. IEEE Electron Device Lett, 2009, 30(12): 1374 doi: 10.1109/LED.2009.2034117[21] http://www.synopsys.com. Sentaurus TCAD User’s Manual[22] Mohapatra S K, Pradhan K P, Singh D, et al. The role of geometry parameters and fin aspect ratio of sub-20 nm SOI-FinFET: an analysis towards analog and RF circuit design. IEEE Trans Nanotechnol, 2015, 14(3): 546 doi: 10.1109/TNANO.2015.2415555[23] Pradhan K P, Mohapatra S K, Sahu P K, et al. Impact of high-k gate dielectric on analog and RF performance of nanoscale DG-MOSFET. Microelectron J, 2014, 45(2): 144 doi: 10.1016/j.mejo.2013.11.016[24] Ho B, Sun X, Shin C, et al. Design optimization of multigate bulk MOSFETs. IEEE Trans Electron Devices, 2013, 60(1): 28 doi: 10.1109/TED.2012.2224870[25] De Andrade M G C, Martino J A, Aoulaiche M, et al. Behavior of triple-gate bulk FinFETs with and without DTMOS operation. Solid-State Electron, 2012, 71: 63 doi: 10.1016/j.sse.2011.10.022[26] Pradhan K P, Sahu P K , Mohapatra S K. Analysis of symmetric high-k spacer (SHS) trigate wavy FinFET: a novel device. India Conference (INDICON), 2 Annual IEEE (IEEE),2015: 1[27] Canali C, Majni G, Minder R, et al. Electron and hole drift velocity measurements in silicon and their empirical relation to electric field and temperature. IEEE Trans Electron Devices, 1975, 22(11): 1045 doi: 10.1109/T-ED.1975.18267[28] Lombardi C, Manzini S, Saporito A, et al. A physically based mobility model for numerical simulation of nonplanar devices. IEEE Trans Comput Des Integr Circuits Syst, 1988, 7(11): 1164 doi: 10.1109/43.9186[29] Shockley W, Read W T. Statistics of the recombination of holes and electrons. Phys Rev, 1952, 87(46): 835[30] Hall R N. Electron–hole recombination in germanium. Phys Rev, 1952, 87(2): 387[31] Sze S M, Ng K K. Physics of semiconductor devices. NJ: John Wiley Sons, 2007[32] Sarkar A, Das A K, De S, et al. Effect of gate engineering in double-gate MOSFETs for analog/RF applications. Microelectron J, 2012, 43(11): 873 doi: 10.1016/j.mejo.2012.06.002 -

Proportional views

DownLoad:

DownLoad: