| Citation: |

Wei Deng, Haikun Jia, Baoyong Chi. Silicon-based FMCW signal generators: A review[J]. Journal of Semiconductors, 2020, 41(11): 111401. doi: 10.1088/1674-4926/41/11/111401

****

W Deng, H K Jia, B Y Chi, Silicon-based FMCW signal generators: A review[J]. J. Semicond., 2020, 41(11): 111401. doi: 10.1088/1674-4926/41/11/111401.

|

-

Abstract

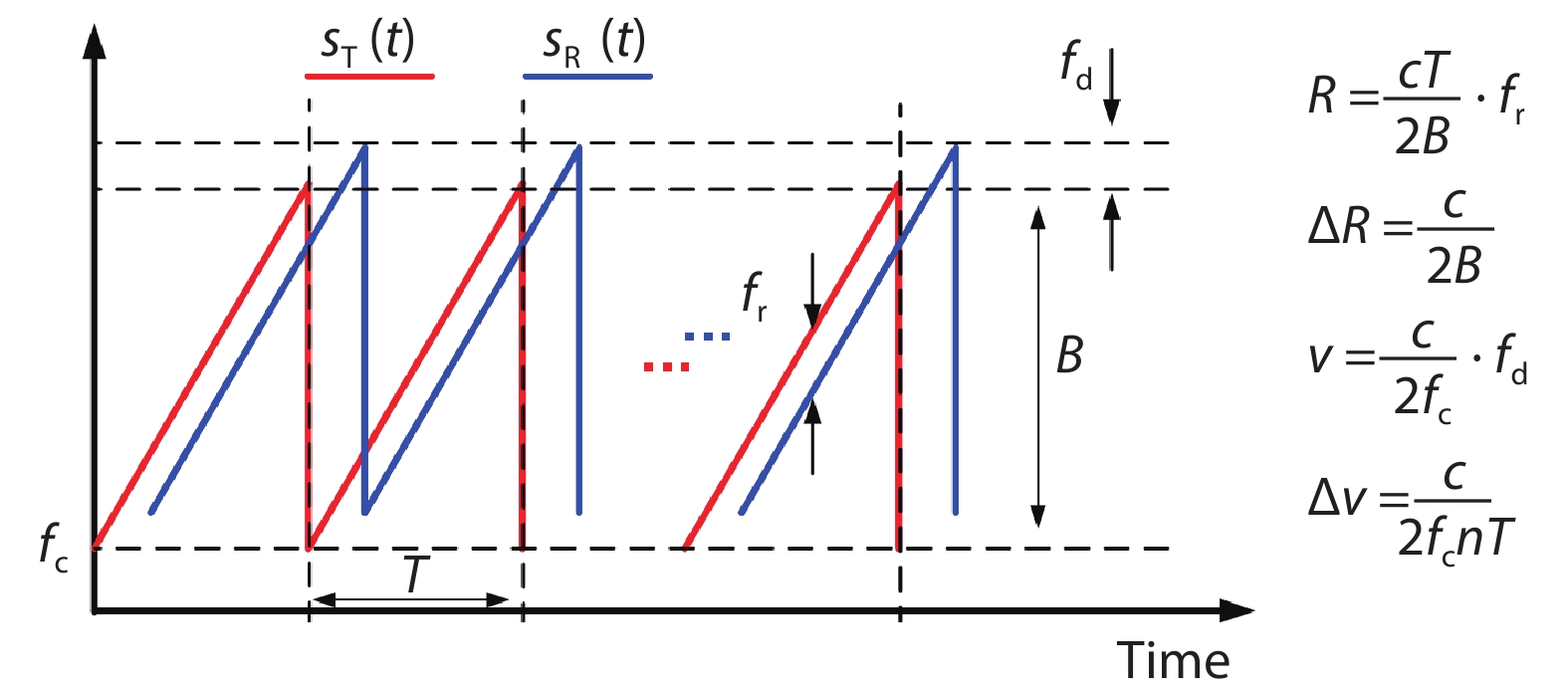

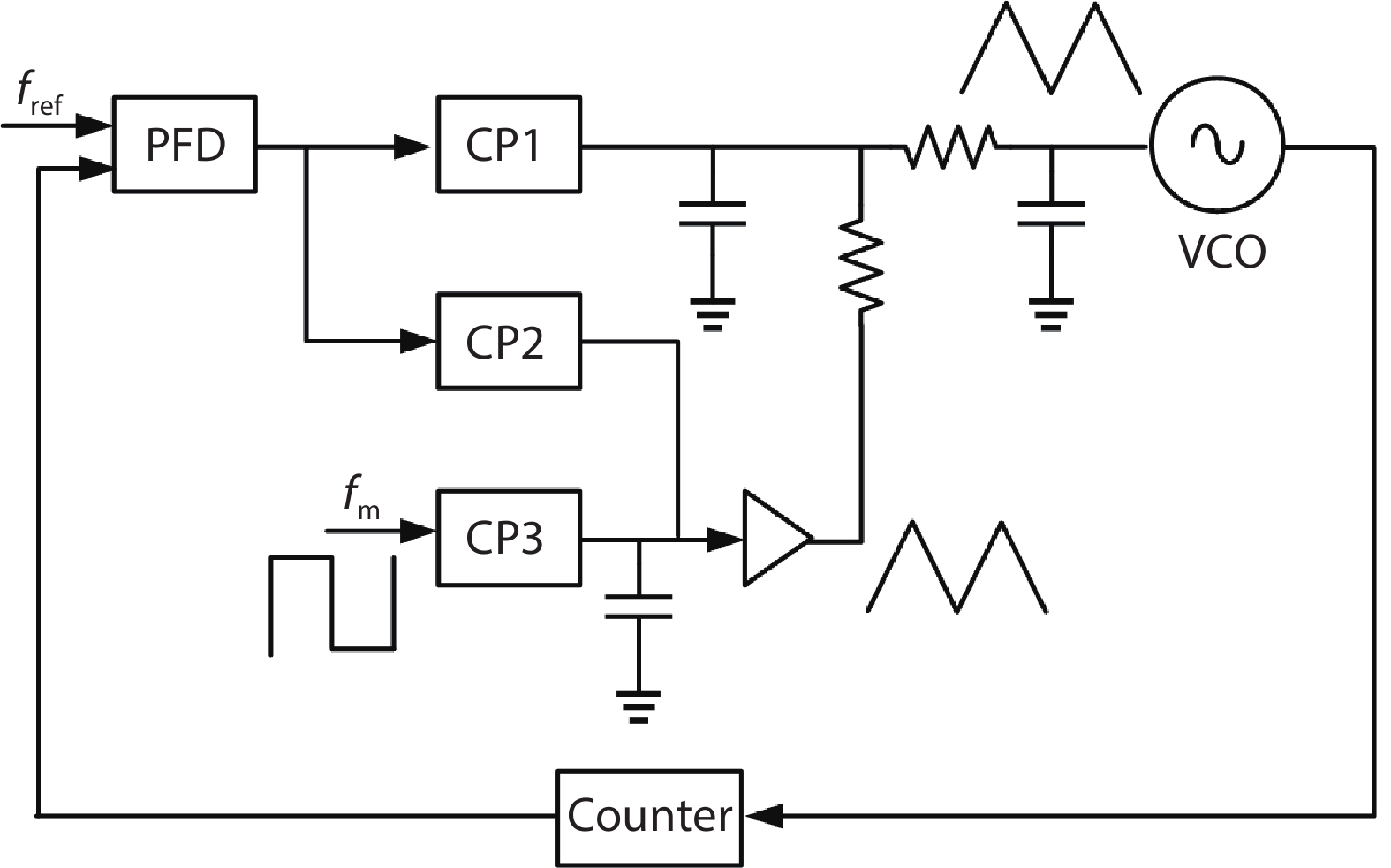

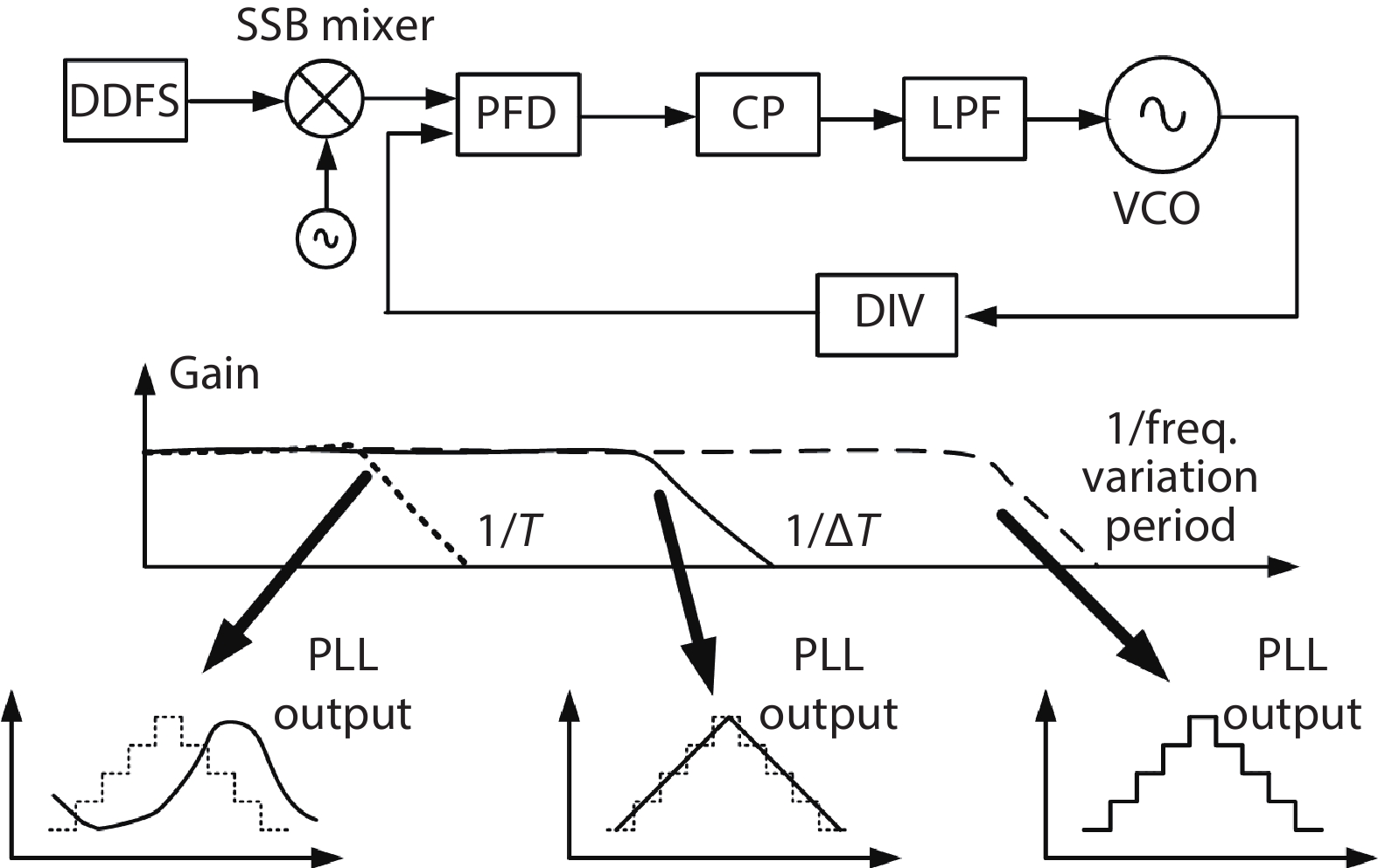

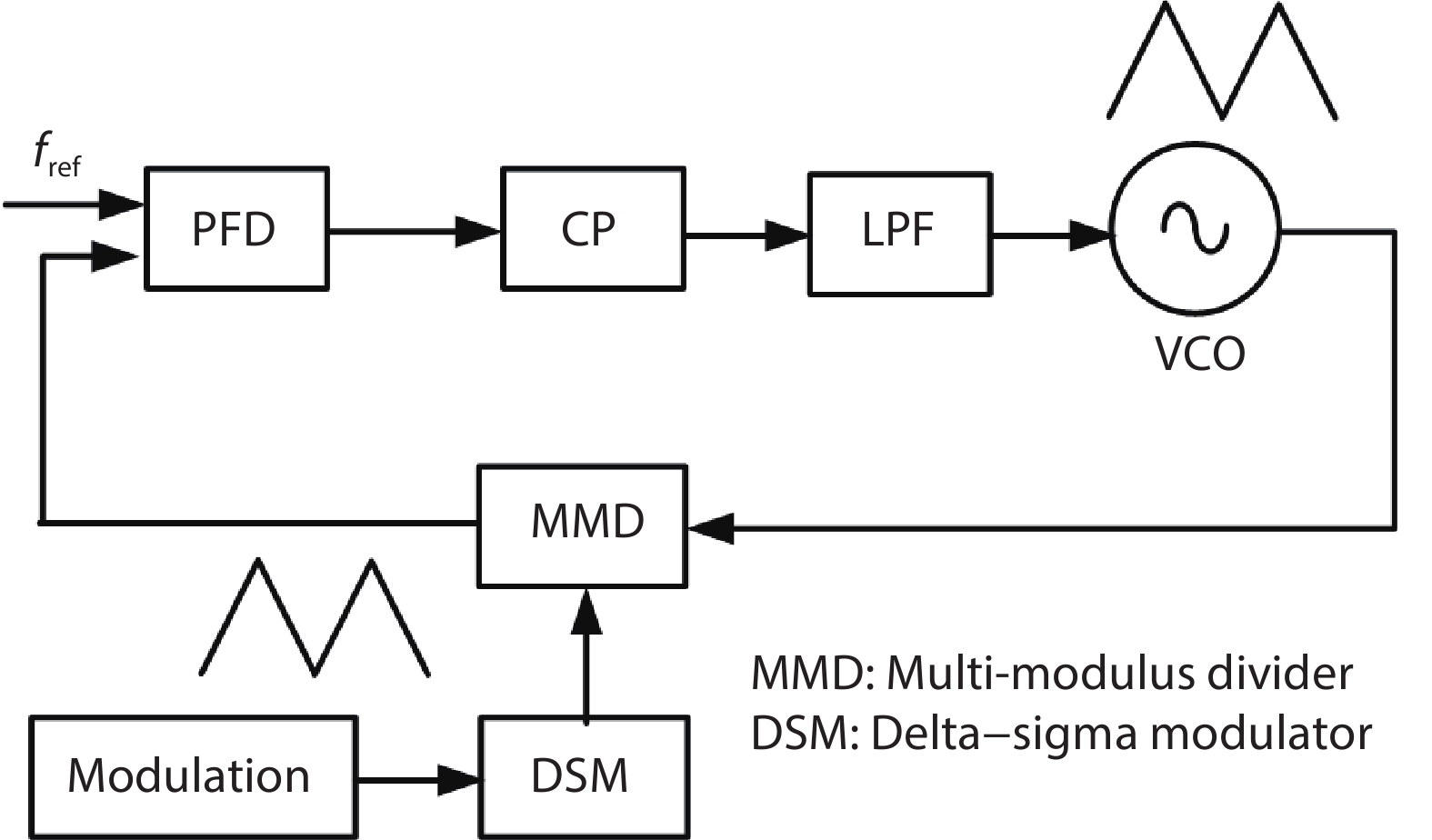

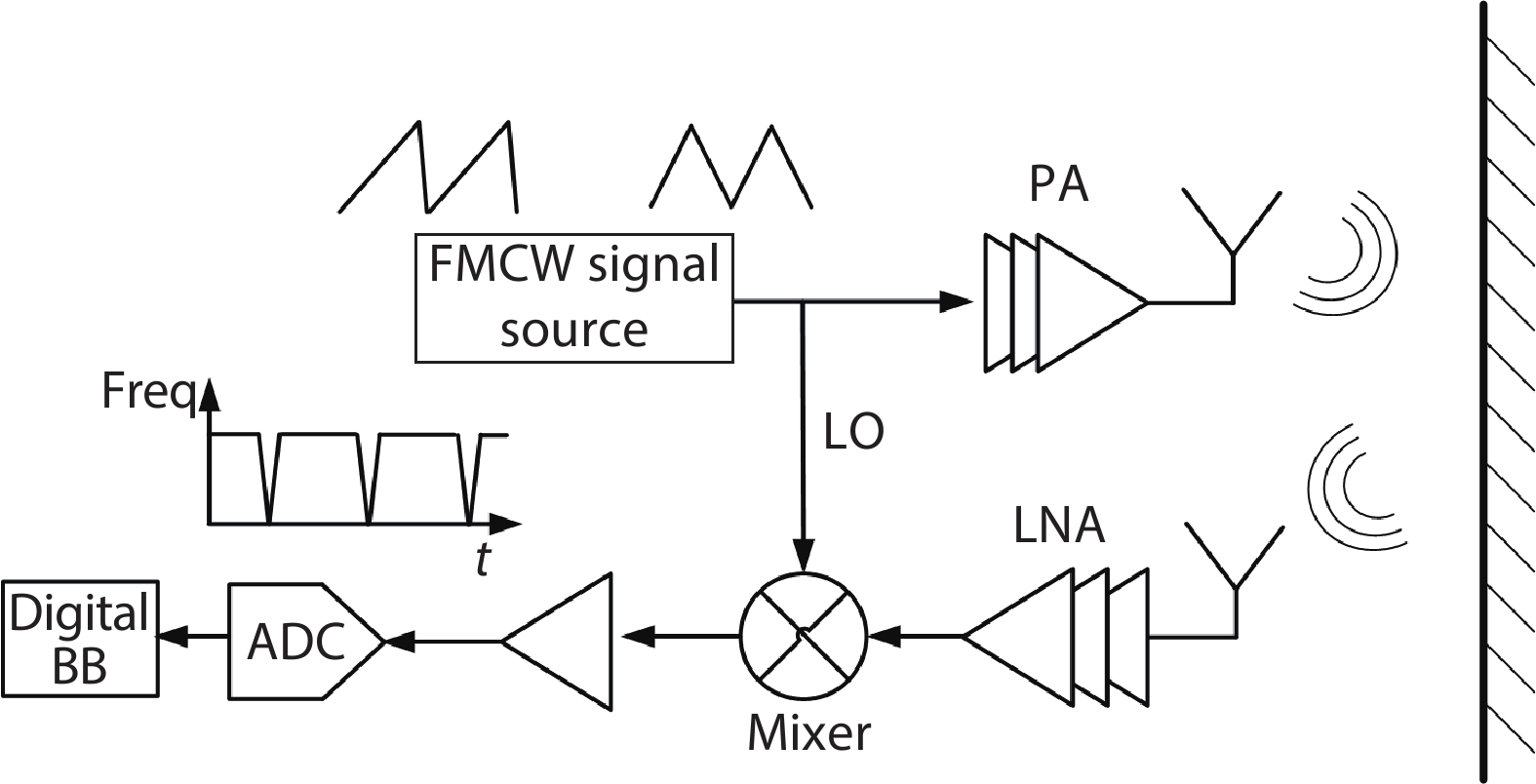

FMCW radars with high resolution necessities the generation of highly linear, low phase noise, and low spur chirp signals with large bandwidth and a short modulation period. This paper reviews recent research progress on silicon-based FMCW signal generators, identifies advances in architecture, fundamental design, performance analysis, and applications of the FMCW synthesizer.-

Keywords:

- slicon,

- FMCW,

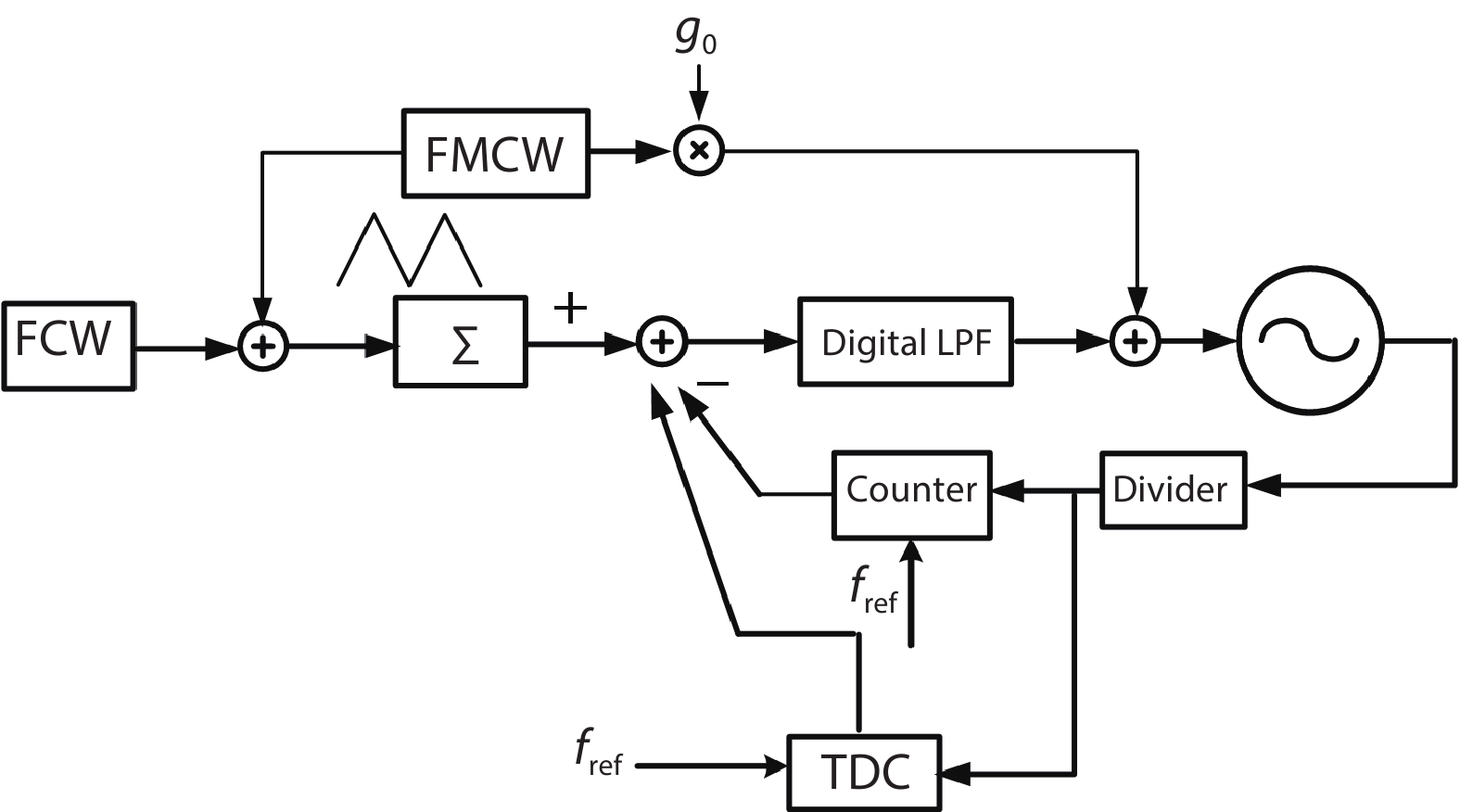

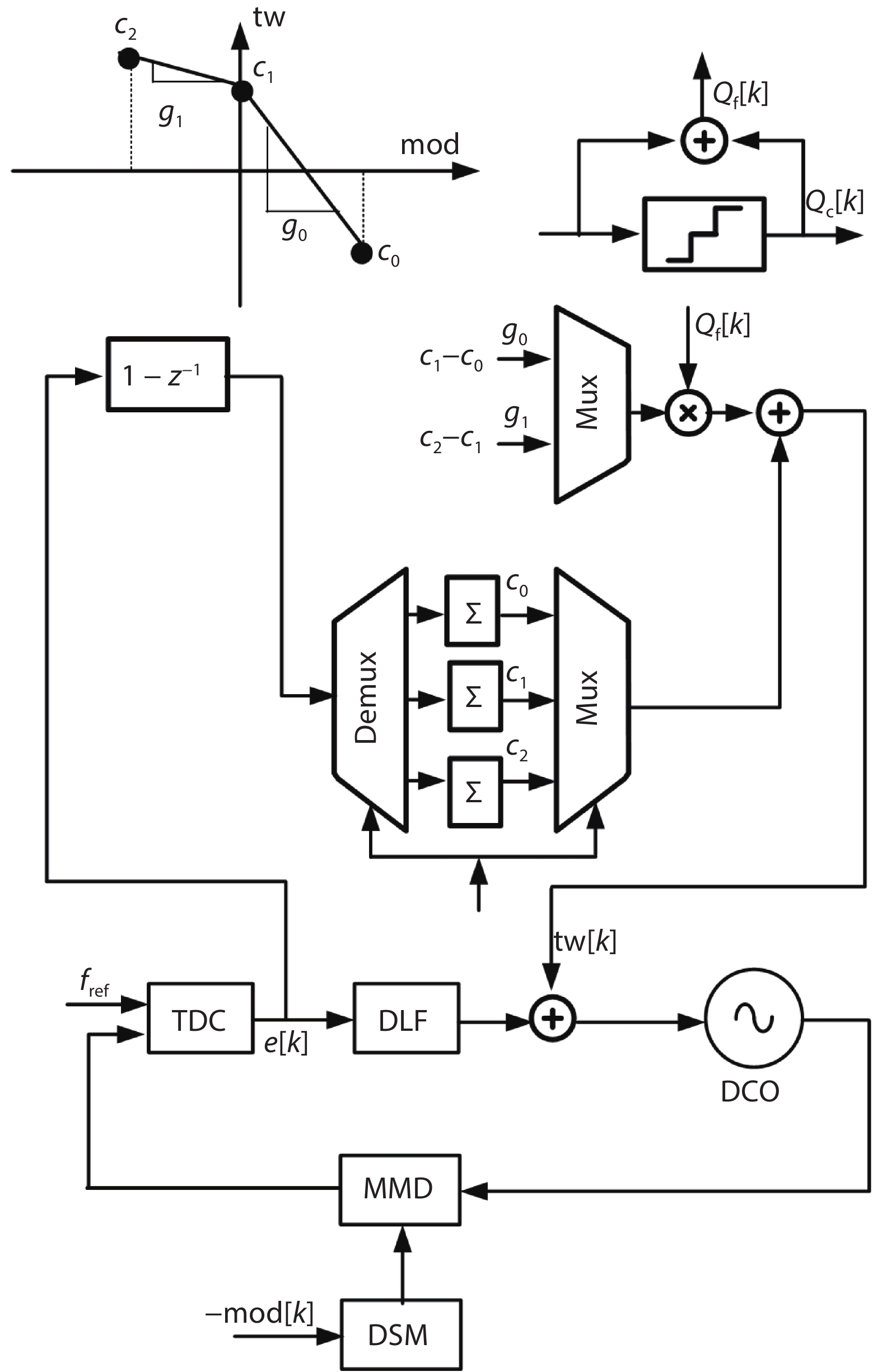

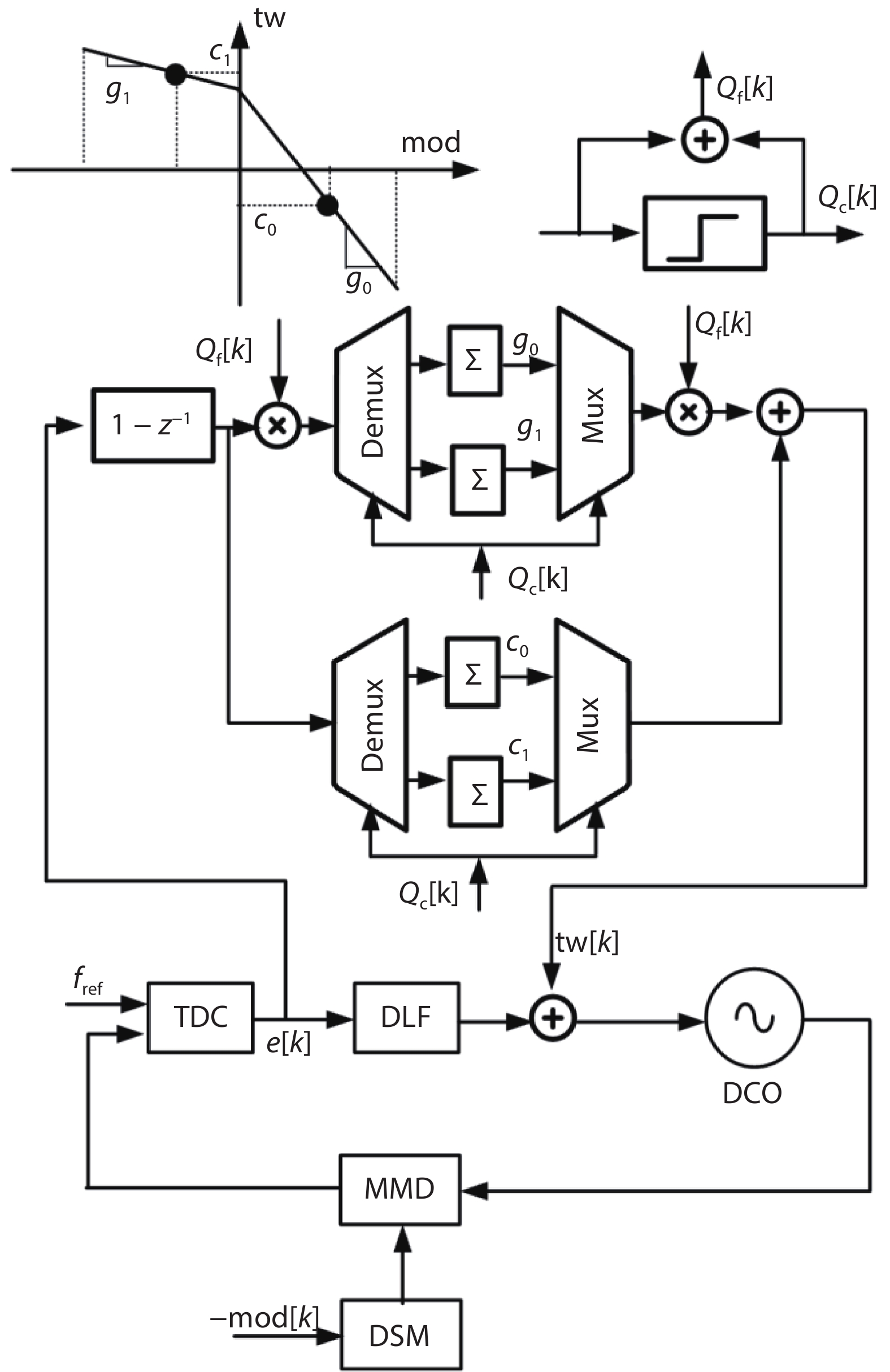

- PLLs,

- radars,

- wireless,

- two-point modulation,

- fast chirp,

- digital pre-distortion

-

References

[1] Park J, Ryu H, Ha K W, et al. 76–81-GHz CMOS transmitter with a phase-locked-loop-based multichirp modulator for automotive radar. IEEE Trans Microw Theory Tech, 2015, 63, 1399 doi: 10.1109/TMTT.2015.2406071[2] Ginsburg B P, Subburaj K, Samala S, et al. A multimode 76-to-81GHz automotive radar transceiver with autonomous monitoring. 2018 IEEE International Solid-State Circuits Conference (ISSCC), 2018, 158[3] Chan W L, Long J R. A 60-GHz band 2 × 2 phased-array transmitter in 65-nm CMOS. IEEE J Solid-State Circuits, 2010, 45, 2682 doi: 10.1109/JSSC.2010.2077170[4] Song J H, Cui C L, Kim S K, et al. A low-phase-noise 77-GHz FMCW radar transmitter with a 12.8-GHz PLL and a ×6 frequency multiplier. IEEE Microw Wirel Compon Lett, 2016, 26, 540 doi: 10.1109/LMWC.2016.2574829[5] Feger R, Pfeffer C, Stelzer A. A frequency-division MIMO FMCW radar system based on delta–sigma modulated transmitters. IEEE Trans Microw Theory Tech, 2014, 62, 3572 doi: 10.1109/TMTT.2014.2364220[6] Fujibayashi T, Takeda Y, Wang W H, et al. A 76- to 81-GHz multi-channel radar transceiver. IEEE J Solid-State Circuits, 2017, 52, 2226 doi: 10.1109/JSSC.2017.2700359[7] Jia H K, Kuang L X, Zhu W, et al. A 77 GHz frequency doubling two-path phased-array FMCW transceiver for automotive radar. IEEE J Solid-State Circuits, 2016, 51, 2299 doi: 10.1109/JSSC.2016.2580599[8] Hung C M, Lin A T, Peng B C, et al. Toward automotive surround-view radars. 2019 IEEE International Solid-State Circuits Conference (ISSCC), 2019, 162[9] Wang Y, Tang K, Zhang Y, et al. A Ku-band 260 mW FMCW synthetic aperture radar TRX with 1.48 GHz BW in 65nm CMOS for micro-UAVs. IEEE ISSCC Dig Tech Papers, 2016, 240[10] Deng W, Wu R, Chen Z J, et al. A 35-GHz TX and RX front end with high TX output power for Ka-band FMCW phased-array radar transceivers in CMOS technology. IEEE Trans VLSI Syst, 2020, 28, 2089 doi: 10.1109/TVLSI.2020.3008423[11] Ma T K, Deng W, Chen Z P, et al. A CMOS 76–81-GHz 2-TX 3-RX FMCW radar transceiver based on mixed-mode PLL chirp generator. IEEE J Solid-State Circuits, 2020, 55, 233 doi: 10.1109/JSSC.2019.2950184[12] Chang H H, Hua I H, Liu S I. A spread-spectrum clock generator with triangular modulation. IEEE J Solid-State Circuits, 2003, 38, 673 doi: 10.1109/JSSC.2003.809521[13] Hsieh Y B, Kao Y H. A fully integrated spread-spectrum clock generator by using direct VCO modulation. IEEE Trans Circuits Syst I, 2008, 55, 1845 doi: 10.1109/TCSI.2008.918194[14] Li H S, Cheng Y C, Puar D. Dual-loop spread-spectrum clock generator. IEEE Int Solid-State Circuits Conf Dig Tech Papers, 1999, 184[15] Huang H Y, Ho S F, Huang L W. A 64-MHz – 1920-MHz programmable spread-spectrum clock generator. Proc IEEE Int Symp Circuit Syst, 2005, 3363[16] Mitomo T, Ono N, Hoshino H, et al. A 77 GHz 90 nm CMOS transceiver for FMCW radar applications. IEEE J Solid-State Circuits, 2010, 45, 928 doi: 10.1109/JSSC.2010.2040234[17] Kim Y, Reck T J, Alonso-Delpino M, et al. A Ku-band CMOS FMCW radar transceiver for snowpack remote sensing. IEEE Trans Microw Theory Tech, 2018, 66, 2480 doi: 10.1109/TMTT.2018.2799866[18] Lee J, Li Y A, Hung M H, et al. A fully-integrated 77-GHz FMCW radar transceiver in 65-nm CMOS technology. IEEE J Solid-State Circuits, 2010, 45, 2746 doi: 10.1109/JSSC.2010.2075250[19] Kokubo M, Kawamoto T, Oshima T, et al. Spread-spectrum clock generator for serial ATA using fractional PLL controlled by delta-sigma modulator with level shifter. 2005 IEEE Int Dig Tech Pap Solid-State Circuits Conf, 2005, 160[20] Lee H R, Kim O, Ahn G, et al. A low-jitter 5000 ppm spread spectrum clock generator for multi-channel SATA transceiver in 0.18 μm CMOS. 2005 IEEE International Digest of Technical Papers, Solid-State Circuits Conference, 2005, 162[21] Shen Z K, Jiang H Y, Li H Y, et al. A 12-GHz calibration-free all-digital PLL for FMCW signal generation with 78 MHz/μs chirp slope and high chirp linearity. IEEE Trans Circuits Syst I, 2020, 1 doi: 10.1109/TCSI.2020.3004363[22] Ng H J, Kucharski M, Ahmad W, et al. Multi-purpose fully differential 61- and 122-GHz radar transceivers for scalable MIMO sensor platforms. IEEE J Solid-State Circuits, 2017, 52, 2242 doi: 10.1109/JSSC.2017.2704602[23] Hasenaecker G, van Delden M, Jaeschke T, et al. A SiGe fractional-N frequency synthesizer for mm-wave wideband FMCW radar transceivers. IEEE Trans Microw Theory Tech, 2016, 64, 847 doi: 10.1109/TMTT.2016.2520469[24] Pohl N, Jaeschke T, Aufinger K. An ultra-wideband 80 GHz FMCW radar system using a SiGe bipolar transceiver chip stabilized by a fractional-N PLL synthesizer. IEEE Trans Microw Theory Tech, 2012, 60, 757 doi: 10.1109/TMTT.2011.2180398[25] Luo T N, Wu C H E, Chen Y J E. A 77-GHz CMOS FMCW frequency synthesizer with reconfigurable chirps. IEEE Trans Microw Theory Tech, 2013, 61, 2641 doi: 10.1109/TMTT.2013.2264685[26] Sakurai H, Kobayashi Y, Mitomo T, et al. A 1.5 GHz-modulation-range 10 ms-modulation-period 180 kHzrms-frequency-error 26 MHz-reference mixed-mode FMCW synthesizer for mm-wave radar application. 2011 IEEE International Solid-State Circuits Conference, 2011, 292[27] Wu J X, Deng W, Chen Z P, et al. A 77-GHz mixed-mode FMCW generator based on a vernier TDC with dual rising-edge fractional-phase detector. IEEE Trans Circuits Syst I, 2020, 67, 60 doi: 10.1109/TCSI.2019.2946277[28] Cherniak D, Grimaldi L, Bertulessi L, et al. A 23-GHz low-phase-noise digital bang–bang PLL for fast triangular and sawtooth chirp modulation. IEEE J Solid-State Circuits, 2018, 53, 3565 doi: 10.1109/JSSC.2018.2869097[29] Shi Q X, Bunsen K, Markulic N, et al. A self-calibrated 16-GHz subsampling-PLL-based fast-chirp FMCW modulator with 1.5-GHz bandwidth. IEEE J Solid-State Circuits, 2019, 54, 3503 doi: 10.1109/JSSC.2019.2941113[30] Cherniak D, Samori C, Nonis R, et al. PLL-based wideband frequency modulator: Two-point injection versus pre-emphasis technique. IEEE Trans Circuits Syst I, 2018, 65, 914 doi: 10.1109/TCSI.2017.2763581[31] Renukaswamy P T, Markulic N, Park S, et al. A 12 mW 10 GHz FMCW PLL based on an integrating DAC with 90 kHz rms frequency error for 23 MHz/μs slope and 1.2 GHz chirp bandwidth. 2020 IEEE International Solid-State Circuits Conference (ISSCC), 2020, 278[32] Gao X, Klumperink E A M, Bohsali M, et al. A low noise sub-sampling PLL in which divider noise is eliminated and PD/CP noise is not multiplied by N2. IEEE J Solid-State Circuits, 2009, 44, 3253 doi: 10.1109/JSSC.2009.2032723[33] Narayanan A T, Katsuragi M, Kimura K, et al. A fractional-N sub-sampling PLL using a pipelined phase-interpolator with an FoM of –250 dB. IEEE J Solid-State Circuits, 2016, 51, 1630 doi: 10.1109/JSSC.2016.2539344[34] Wu W H, Staszewski R B, Long J R. A 56.4-to-63.4 GHz multi-rate all-digital fractional-N PLL for FMCW radar applications in 65 nm CMOS. IEEE J Solid-State Circuits, 2014, 49, 1081 doi: 10.1109/JSSC.2014.2301764[35] Yeo H, Ryu S, Lee Y, et al. A 940 MHz-bandwidth 28.8μs-period 8.9 GHz chirp frequency synthesizer PLL in 65nm CMOS for X-band FMCW radar applications. 2016 IEEE International Solid-State Circuits Conference (ISSCC), 2016, 238[36] Lin J F, Song Z, Qi N, et al. A 77-GHz mixed-mode FMCW signal generator based on bang-bang phase detector. IEEE J Solid-State Circuits, 2018, 53, 2850 doi: 10.1109/JSSC.2018.2856248[37] Levantino S, Marzin G, Samori C. An adaptive pre-distortion technique to mitigate the DTC nonlinearity in digital PLLs. IEEE J Solid-State Circuits, 2014, 49, 1762 doi: 10.1109/JSSC.2014.2314436[38] Markulic N, Raczkowski K, Martens E, et al. A DTC-based subsampling PLL capable of self-calibrated fractional synthesis and two-point modulation. IEEE J Solid-State Circuits, 2016, 51, 3078 doi: 10.1109/JSSC.2016.2596766[39] Yao C W, Ni R H, Lau C, et al. A 14-nm 0.14-psrms fractional-N digital PLL with a 0.2-ps resolution ADC-assisted coarse/fine-conversion chopping TDC and TDC nonlinearity calibration. IEEE J Solid-State Circuits, 2017, 52, 3446 doi: 10.1109/JSSC.2017.2742518[40] Marzin G, Levantino S, Samori C, et al. A 20 Mb/s phase modulator based on a 3.6 GHz digital PLL with −36 dB EVM at 5 mW power. IEEE J Solid-State Circuits, 2012, 47, 2974 doi: 10.1109/JSSC.2012.2217854[41] Vovnoboy J, Levinger R, Mazor N, et al. A dual-loop synthesizer with fast frequency modulation ability for 77/79 GHz FMCW automotive radar applications. IEEE J Solid-State Circuits, 2018, 53, 1328 doi: 10.1109/JSSC.2017.2784758 -

Proportional views

DownLoad:

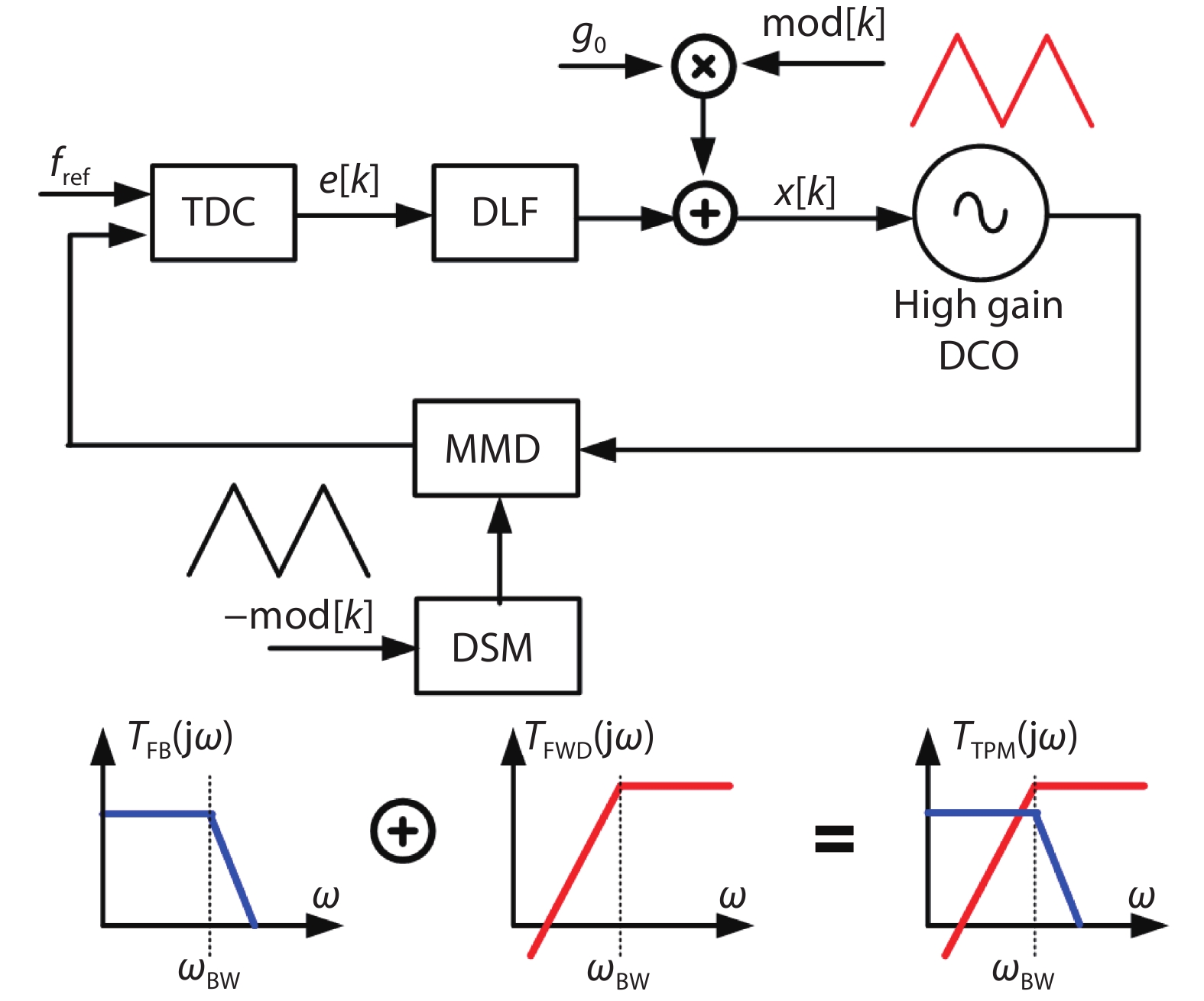

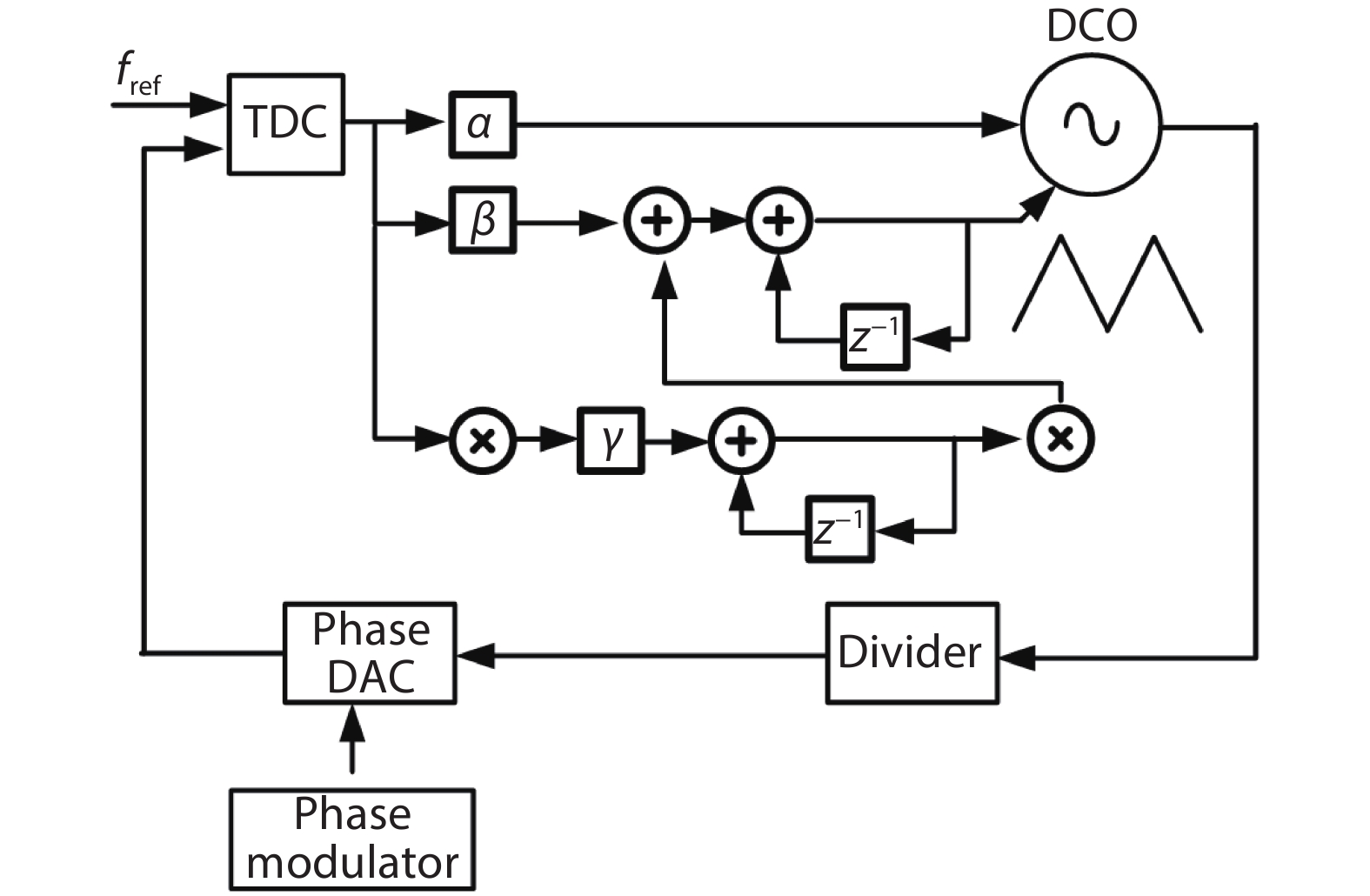

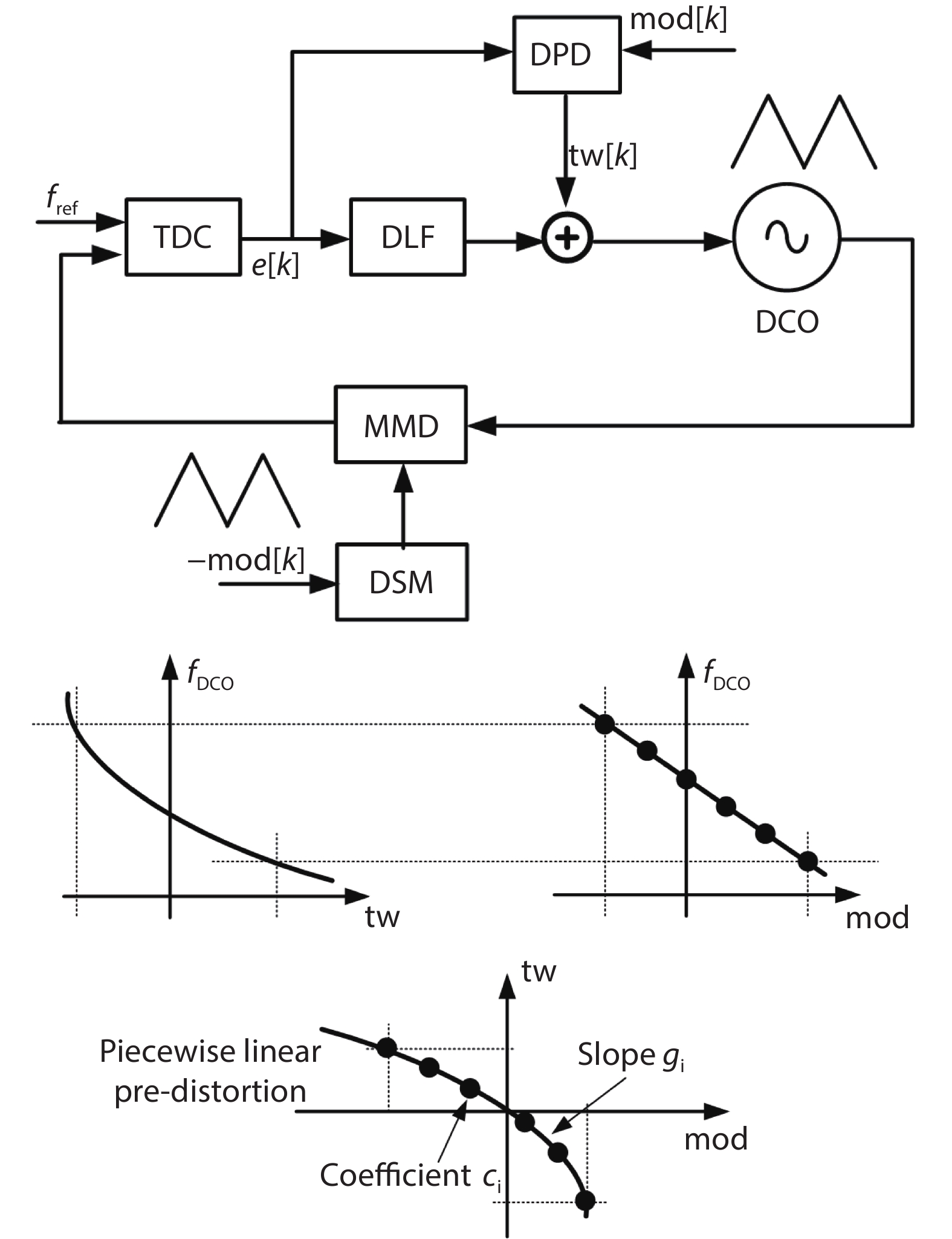

DownLoad: