| Citation: |

Zhao Zhang. CMOS analog and mixed-signal phase-locked loops: An overview[J]. Journal of Semiconductors, 2020, 41(11): 111402. doi: 10.1088/1674-4926/41/11/111402

****

Z Zhang, CMOS analog and mixed-signal phase-locked loops: An overview[J]. J. Semicond., 2020, 41(11): 111402. doi: 10.1088/1674-4926/41/11/111402.

|

CMOS analog and mixed-signal phase-locked loops: An overview

DOI: 10.1088/1674-4926/41/11/111402

More Information

-

Abstract

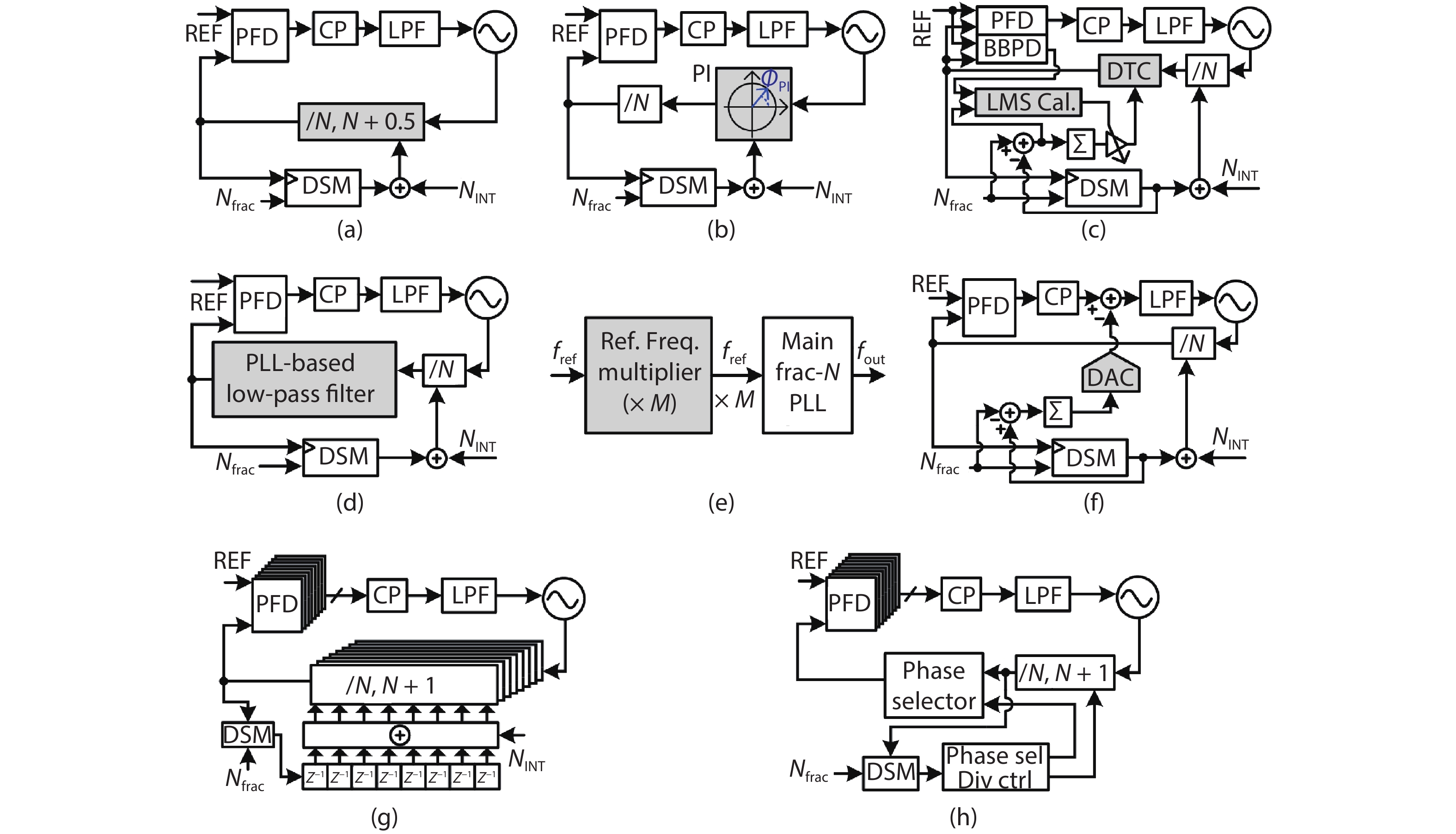

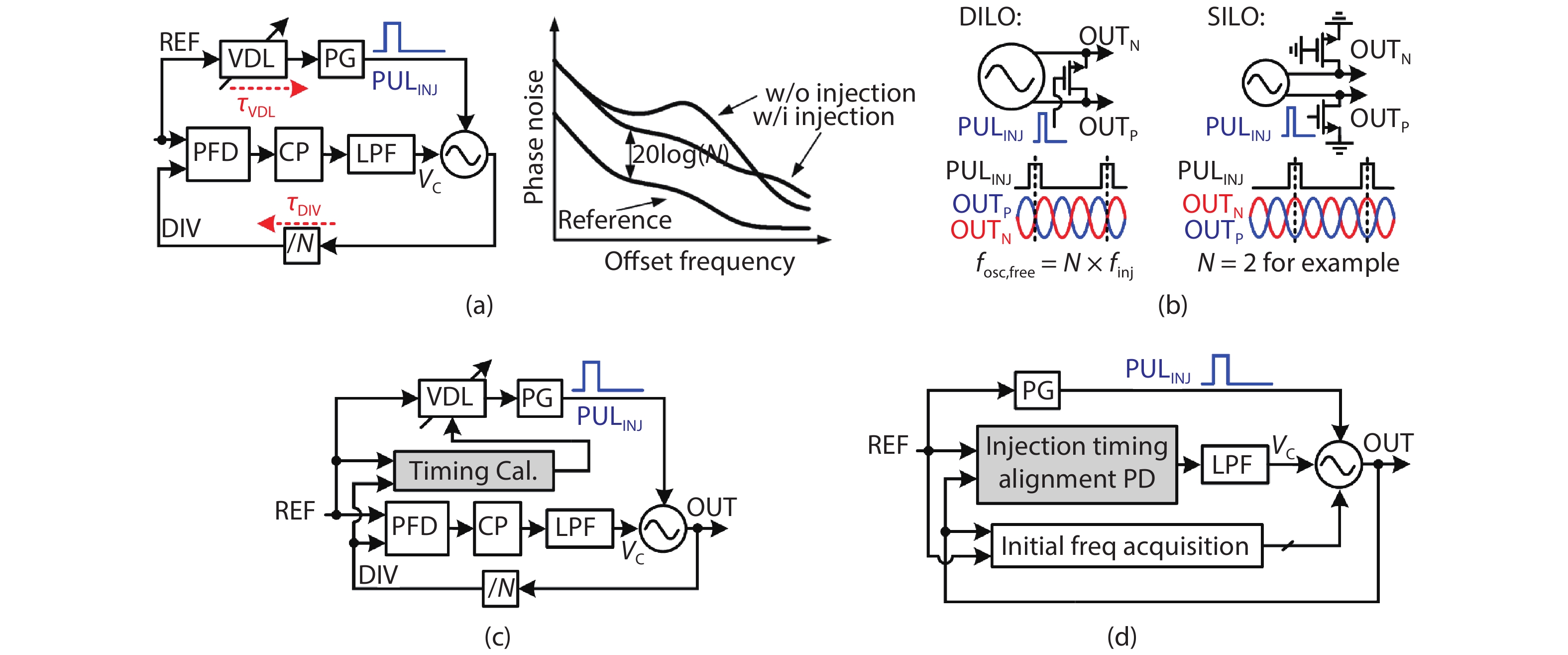

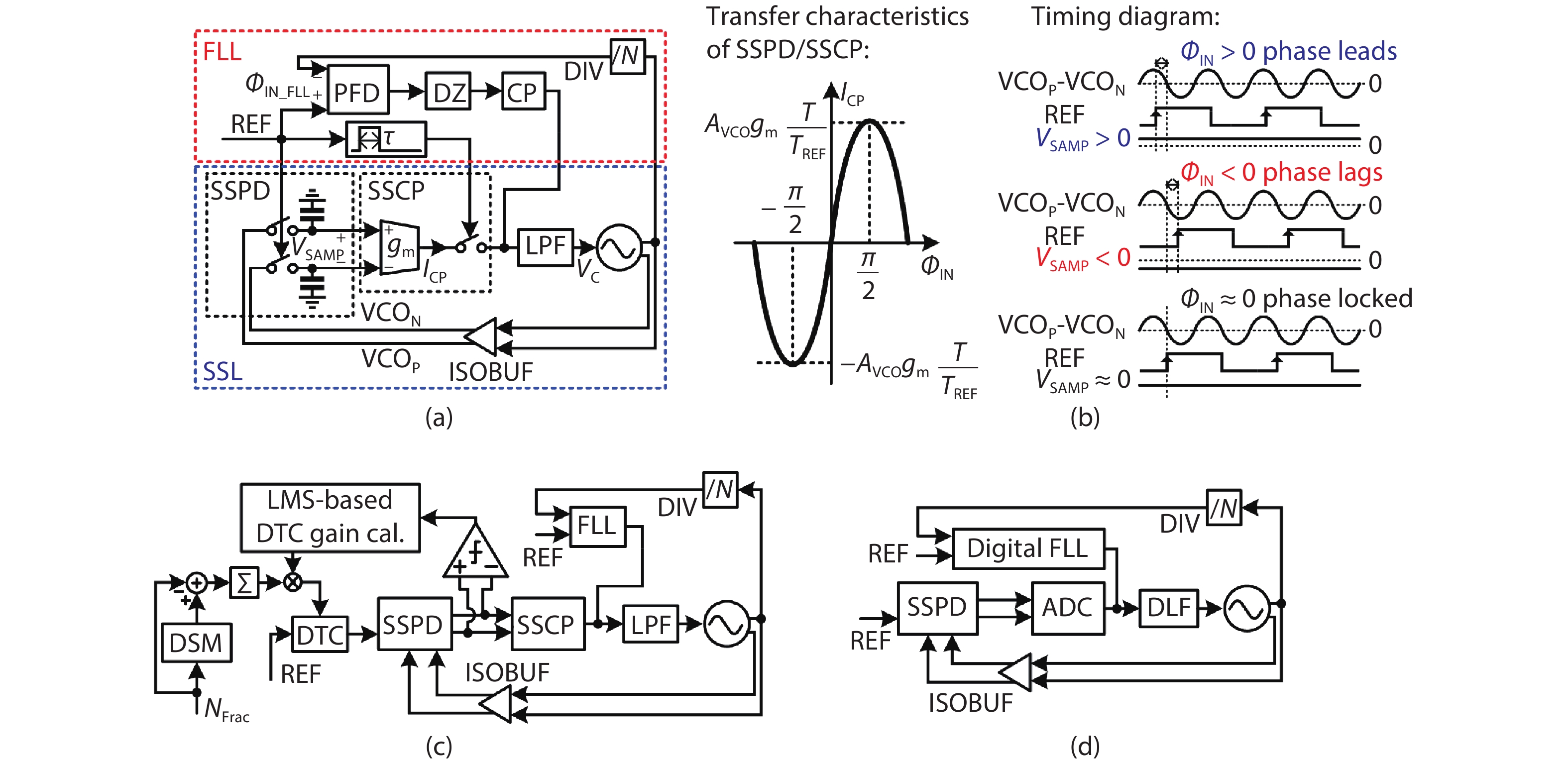

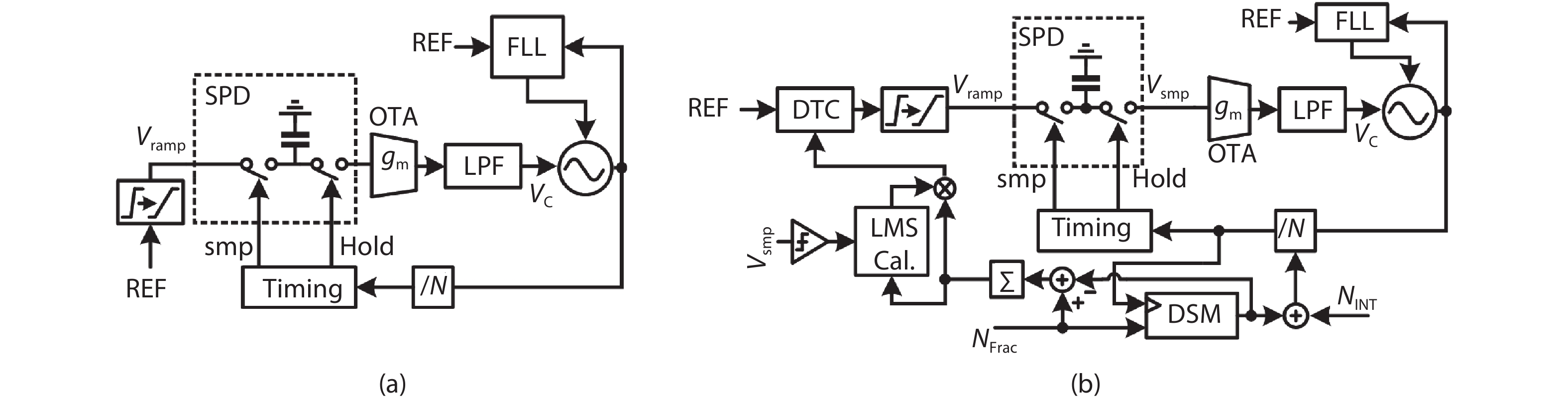

CMOS analog and mixed-signal phase-locked loops (PLL) are widely used in varies of the system-on-chips (SoC) as the clock generator or frequency synthesizer. This paper presents an overview of the AMS-PLL, including: 1) a brief introduction of the basics of the charge-pump based PLL, which is the most widely used AMS-PLL architecture due to its simplicity and robustness; 2) a summary of the design issues of the basic CPPLL architecture; 3) a systematic introduction of the techniques for the performance enhancement of the CPPLL; 4) a brief overview of ultra-low-jitter AMS-PLL architectures which can achieve lower jitter (< 100 fs) with lower power consumption compared with the CPPLL, including the injection-locked PLL (ILPLL), sub-sampling (SSPLL) and sampling PLL (SPLL); 5) a discussion about the consideration of the AMS-PLL architecture selection, which could help designers meet their performance requirements. -

References

[1] Liu H L, Shirane A, Okada K, et al. A 265-μW fractional-N digital PLL with seamless automatic switching sub-sampling/sampling feedback path and duty-cycled frequency-locked loop in 65-nm CMOS. IEEE J Solid-State Circuits, 2019, 54, 3478 doi: 10.1109/JSSC.2019.2936967[2] Fan Y P, Xiang B, Zhang D, et al. Digital leakage compensation for a low-power and low-jitter 0.5-to-5GHz PLL in 10nm FinFET CMOS technology. 2019 IEEE International Solid-State Circuits Conference (ISSCC), 2019, 320[3] Lazavi B. RF microelectronics. 2nd ed. Los Angeles: Pearson, 2012[4] Riley T A D, Copeland M A, Kwasniewski T A. Delta-sigma modulation in fractional-N frequency synthesis. IEEE J Solid-State Circuits, 1993, 28, 553 doi: 10.1109/4.229400[5] Shu K, Sinencio S. PLL frequency synthesizer. CMOS PLL Synthesizers: Analysis and design. New York: Springer-Verlag, 2006, 31[6] Perrott M H, Trott M D, Sodini C G. A modeling approach for Σ-Δ fractional-N frequency synthesizers allowing straightforward noise analysis. IEEE J Solid-State Circuits, 2002, 37, 1028 doi: 10.1109/JSSC.2002.800925[7] Ho C R, Chen M S W. Smoothing the way for digital phase-locked loops: Clock generation in the future with digital signal processing for mitigating spur and interference. IEEE Microw, 2019, 20, 80 doi: 10.1109/MMM.2019.2898022[8] Hedayati H, Khalil W, Bakkaloglu B. A 1 MHz bandwidth, 6 GHz 0.18 μm CMOS type-I ΔΣ fractional-N synthesizer for WiMAX applications. IEEE J Solid-State Circuits, 2009, 44, 3244 doi: 10.1109/JSSC.2009.2032713[9] Lin T H, Ti C L, Liu Y H. Dynamic current-matching charge pump and gated-offset linearization technique for delta-sigma fractional-N PLLs. IEEE Trans Circuits Syst I, 2009, 56, 877 doi: 10.1109/TCSI.2009.2016180[10] Sadeghi V S, Miar Naimi H, Kennedy M P. The role of charge pump mismatch in the generation of integer boundary spurs in fractional-N frequency synthesizers: Why worse can be better. IEEE Trans Circuits Syst II, 2013, 60, 862 doi: 10.1109/TCSII.2013.2285968[11] Temporiti E, Albasini G, Bietti I, et al. A 700-kHz bandwidth ΔΣ fractional synthesizer with spurs compensation and linearization techniques for WCDMA applications. IEEE J Solid-State Circuits, 2004, 39, 1446 doi: 10.1109/JSSC.2004.831598[12] Arora H, Klemmer N, Morizio J C, et al. Enhanced phase noise modeling of fractional-N frequency synthesizers. IEEE Trans Circuits Syst I, 2005, 52, 379 doi: 10.1109/TCSI.2004.841594[13] Khalil W, Hedayati H, Bakkaloglu B, et al. Analysis and modeling of noise folding and spurious emission in wideband fractional-N synthesizers. 2008 IEEE Radio Freq Integr Circuits Symp, 2008, 291[14] Lee J S, Keel M S, Lim S I, et al. Charge pump with perfect current matching characteristics in phase-locked loops. Electron Lett, 2000, 36, 1907 doi: 10.1049/el:20001358[15] Hwang I C, Baek D. A 0.93-mA spur-enhanced frequency synthesizer for L1/L5 dual-band GPS/Galileo RF receiver. IEEE Microw Wirel Compon Lett, 2010, 20, 355 doi: 10.1109/LMWC.2010.2047533[16] Mazzanti A, Vahidfar M B, Sosio M, et al. A low phase-noise multi-phase LO generator for wideband demodulators based on reconfigurable sub-harmonic mixers. IEEE J Solid-State Circuits, 2010, 45, 2104 doi: 10.1109/JSSC.2010.2060258[17] Chen W H, Loke W F, Jung B. A 0.5-V, 440-μW frequency synthesizer for implantable medical devices. IEEE J Solid-State Circuits, 2012, 47, 1896 doi: 10.1109/JSSC.2012.2196315[18] Lou W F, Feng P, Wang H Y, et al. Low power fast settling multi-standard current reusing CMOS fractional-N frequency synthesizer. J Semicond, 2012, 33, 045004 doi: 10.1088/1674-4926/33/4/045004[19] Choi Y C, Seong Y J, Yoo Y J, et al. Multi-standard hybrid PLL with low phase-noise characteristics for GSM/EDGE and LTE applications. IEEE Trans Microw Theory Tech, 2015, 63, 3254 doi: 10.1109/TMTT.2015.2469251[20] Lai C M, Tan K W, Chen Y J, et al. A UWB impulse-radio timed-array radar with time-shifted direct-sampling architecture in 0.18-$\mu{\rm m}$ CMOS. IEEE Trans Circuits Syst I, 2014, 61, 2074 doi: 10.1109/TCSI.2013.2295896[21] Larsson P. A 2-1600-MHz CMOS clock recovery PLL with low-Vdd capability. IEEE J Solid-State Circuits, 1999, 34, 1951 doi: 10.1109/4.808920[22] Shi X T, Imfeld K, Tanner S, et al. A low-jitter and low-power CMOS PLL for clock multiplication. 2006 Proc 32nd Eur Solid-State Circuits Conf, 2006, 174[23] Lahiri A, Gupta N, Kumar A, et al. A 600 μA 32 kHz input 960 MHz output CP-PLL with 530 ps integrated jitter in 28 nm FD-SOI process. IEEE J Solid-State Circuits, 2015, 50, 1680 doi: 10.1109/JSSC.2015.2412680[24] Jung W, Choi H, Jeong C, et al. A 1.2mW 0.02mm2 2GHz current-controlled PLL based on a self-biased voltage-to-current converter. 2007 IEEE International Solid-State Circuits Conference, 2007, 310[25] Cheng S, Tong H, Silva-Martinez J, et al. Design and analysis of an ultrahigh-speed glitch-free fully differential charge pump with minimum output current variation and accurate matching. IEEE Trans Circuits Syst II, 2006, 53, 843 doi: 10.1109/TCSII.2006.879100[26] Yang Y C, Lu S S. A single-VCO fractional-N frequency synthesizer for digital TV tuners. IEEE Trans Ind Electron, 2010, 57, 3207 doi: 10.1109/TIE.2009.2038394[27] Abdulaziz M, Forsberg T, Tormanen M, et al. A 10-mW mm-wave phase-locked loop with improved lock time in 28-nm FD-SOI CMOS. IEEE Trans Microw Theory Tech, 2019, 67, 1588 doi: 10.1109/TMTT.2019.2896566[28] Liang C F, Chen S H, Liu S I. A digital calibration technique for charge pumps in phase-locked systems. IEEE J Solid-State Circuits, 2008, 43, 390 doi: 10.1109/JSSC.2007.914283[29] Chiu W H, Chang T S, Lin T H. A charge pump current mismatch calibration technique for ΔΣ fractional-N PLLs in 0.18-μm CMOS. IEEE Asian Solid-State Circuit Conference, 2009, 73[30] Chen Y W, Yu Y H, Chen Y J E. A 0.18-μm CMOS dual-band frequency synthesizer with spur reduction calibration. IEEE Microw Wirel Compon Lett, 2013, 23, 551 doi: 10.1109/LMWC.2013.2279113[31] Liu S B, Sun D P, Ding R X, et al. A multiplexing DAPD technique for fast-locking and charge pumps calibration in PLLs. IEEE Microw Wirel Compon Lett, 2019, 29, 535 doi: 10.1109/LMWC.2019.2923891[32] Zhang Z, Liu L Y, Wu N J, et al. Source-switched charge pump with reverse leakage compensation technique for spur reduction of wideband PLL. Electron Lett, 2016, 52, 1211 doi: 10.1049/el.2016.1036[33] Shen K Y, Syed Farooq S F, Fan Y P, et al. A flexible, low-power analog PLL for SoC and processors in 14nm CMOS. IEEE Trans Circuits Syst I, 2018, 65, 2109 doi: 10.1109/TCSI.2017.2784319[34] Xiang B, Fan Y P, Ayers J, et al. A 0.5V-to-0.9V 0.2GHz-to-5GHz ultra-low-power digitally-assisted analog ring PLL with less than 200ns lock time in 22nm FinFET CMOS technology. 2020 IEEE Custom Integrated Circuits Conference (CICC), 2020, 1[35] Shekhar S, Gangopadhyay D, Woo E C, et al. A 2.4-GHz extended-range type-I ΔΣ fractional-N synthesizer with 1.8-MHz loop bandwidth and −110-dBc/Hz phase noise. IEEE Trans Circuits Syst II, 2011, 58, 472 doi: 10.1109/TCSII.2011.2158752[36] Lu L, Chen J H, Yuan L, et al. An 18-mW 1.175–2-GHz frequency synthesizer with constant bandwidth for DVB-T tuners. IEEE Trans Microw Theory Tech, 2009, 57, 928 doi: 10.1109/TMTT.2009.2014449[37] Lou W F, Liu X D, Feng P, et al. An integrated 0.38–6 GHz, 9–12 GHz fully differential fractional-N frequency synthesizer for multi-standard reconfigurable MIMO communication application. Analog Integr Circ Sig Process, 2014, 78, 807 doi: 10.1007/s10470-013-0246-0[38] Zhang Z, Yang J C, Liu L Y, et al. 0.1–5 GHz wideband ΔΣ fractional-N frequency synthesiser for software-defined radio application. IET Circuits Devices Syst, 2019, 13, 1071 doi: 10.1049/iet-cds.2018.5271[39] Zhang Z, Liu L Y, Feng P, et al. A 2.4–3.6-GHz wideband subharmonically injection-locked PLL with adaptive injection timing alignment technique. IEEE Trans VLSI Syst, 2017, 25, 929 doi: 10.1109/TVLSI.2016.2619362[40] Elsayed M M, Abdul-Latif M, Sanchez-Sinencio E. A spur-frequency-boosting PLL with a –74 dBc reference-spur suppression in 90 nm digital CMOS. IEEE J Solid-State Circuits, 2013, 48, 2104 doi: 10.1109/JSSC.2013.2266865[41] Lee T C, Lee W L. A spur suppression technique for phase-locked frequency synthesizers. 2006 IEEE International Solid State Circuits Conference, 2006, 2432[42] Çatlı B, Nazemi A, Ali T, et al. A sub-200 fs RMS jitter capacitor multiplier loop filter-based PLL in 28 nm CMOS for high-speed serial communication applications. Proceedings of the IEEE 2013 Custom Integrated Circuits Conference, 2013, 1[43] Lahiri A, Gupta N. A 0.0175mm2 600μW 32kHz input 307MHz output PLL with 190psrms jitter in 28nm FD-SOI. 42nd Eur Solid-State Circuits Conf, 2016, 339[44] Sadhu B, Ferriss M A, Natarajan A S, et al. A linearized, low-phase-noise VCO-based 25-GHz PLL with autonomic biasing. IEEE J Solid-State Circuits, 2013, 48, 1138 doi: 10.1109/JSSC.2013.2252513[45] Ferriss M, Plouchart J O, Natarajan A, et al. An integral path self-calibration scheme for a dual-loop PLL. IEEE J Solid-State Circuits, 2013, 48, 996 doi: 10.1109/JSSC.2013.2239114[46] Zhang Z, Zhu G, Yue C P. A 0.25-0.4V, sub-0.11mW/GHz, 0.15-1.6GHz PLL using an offset dual-path loop architecture with dynamic charge pumps. 2019 Symp VLSI Circuits, 2019, C158[47] Sun Y F, Zhang Z, Xu N, et al. A 1.75 mW 1.1 GHz semi-digital fractional-N PLL with TDC-less hybrid loop control. IEEE Microw Wirel Compon Lett, 2012, 22, 654 doi: 10.1109/LMWC.2012.2228178[48] Ferriss M, Rylyakov A, Tierno J A, et al. A 28 GHz Hybrid PLL in 32 nm SOI CMOS. IEEE J Solid-State Circuits, 2014, 49, 1027 doi: 10.1109/JSSC.2014.2299273[49] Ferriss M, Sadhu B, Rylyakov A, et al. A 13.1-to-28GHz fractional-N PLL in 32nm SOI CMOS with a ΔΣ noise-cancellation scheme. IEEE International Solid-State Circuit Conference, 2015, 192[50] Yin W J, Inti R, Elshazly A, et al. A 0.7-to-3.5 GHz 0.6-to-2.8 mW highly digital phase-locked loop with bandwidth tracking. IEEE J Solid-State Circuits, 2011, 46, 1870 doi: 10.1109/JSSC.2011.2157259[51] Kim D, Cho S. A hybrid PLL using low-power GRO-TDC for reduced in-band phase noise. IEEE Trans Circuits Syst II, 2019, 66, 232 doi: 10.1109/TCSII.2018.2848218[52] Zhu J H, Nandwana R K, Shu G H, et al. A 0.0021 mm2 1.82 mW 2.2 GHz PLL using time-based integral control in 65 nm CMOS. IEEE J Solid-State Circuits, 2017, 52, 8 doi: 10.1109/JSSC.2016.2598768[53] Chuang J, Krishnaswamy H. A 0.0049mm2 2.3GHz sub-sampling ring-oscillator PLL with time-based loop filter achieving −236.2dB jitter-FOM. 2017 IEEE International Solid-State Circuits Conference (ISSCC), 2017, 328[54] Homayoun A, Razavi B. Analysis of phase noise in phase/frequency detectors. IEEE Trans Circuits Syst I, 2013, 60, 529 doi: 10.1109/TCSI.2012.2215792[55] Vlachogiannakis G, Basetas C, Tsirimokou G, et al. A self-calibrated fractional-N PLL for WiFi 6 / 802.11ax in 28nm FDSOI CMOS. IEEE 45th Eur Solid State Circuits Conf ESSCIRC, 2019, 105[56] Jin J, Liu X M, Mo T T, et al. Quantization noise suppression in fractional-N PLLs utilizing glitch-free phase switching multi-modulus frequency divider. IEEE Trans Circuits Syst I, 2012, 59, 926 doi: 10.1109/TCSI.2012.2189042[57] Levantino S, Marzin G, Samori C, et al. A wideband fractional-N PLL with suppressed charge-pump noise and automatic loop filter calibration. IEEE J Solid-State Circuits, 2013, 48, 2419 doi: 10.1109/JSSC.2013.2273836[58] Kong L, Razavi B. A 2.4 GHz 4 mW integer-N inductorless RF synthesizer. IEEE J Solid-State Circuits, 2016, 51, 626 doi: 10.1109/JSSC.2015.2511157[59] Levantino S, Romano L, Pellerano S, et al. Phase noise in digital frequency dividers. IEEE J Solid-State Circuits, 2004, 39, 775 doi: 10.1109/JSSC.2004.826338[60] Tasca D, Zanuso M, Levantino S, et al. Low-power divider retiming in a 3–4 GHz fractional-N PLL. IEEE Trans Circuits Syst II, 2011, 58, 200 doi: 10.1109/TCSII.2011.2124510[61] Shen K Y J, Farooq S F S, Fan Y P, et al. A 0.17-to-3.5mW 0.15-to-5GHz SoC PLL with 15dB built-in supply noise rejection and self-bandwidth control in 14nm CMOS. 2016 IEEE International Solid-State Circuits Conference (ISSCC), 2016, 330[62] Zhang Z, Yang J C, Liu L Y, et al. A 0.9–2.25-GHz sub-0.2-mW/GHz compact low-voltage low-power hybrid digital PLL with loop bandwidth-tracking technique. IEEE Trans VLSI Syst, 2018, 26, 933 doi: 10.1109/TVLSI.2018.2797280[63] Lee J, Park S, Cho S. A 470-μW 5-GHz digitally controlled injection-locked multi-modulus frequency divider with an in-phase dual-input injection scheme. IEEE Trans VLSI Syst, 2011, 19, 61 doi: 10.1109/TVLSI.2009.2030575[64] Wu L, Luong H C. Analysis and design of a 0.6 V 2.2 mW 58.5-to-72.9 GHz divide-by-4 injection-locked frequency divider with harmonic boosting. IEEE Trans Circuits Syst I, 2013, 60, 2001 doi: 10.1109/TCSI.2013.2256240[65] Jang S L, Lai W C, Lin G Y, et al. Injection-locked frequency divider with a resistively distributed resonator for wide-locking-range performance. IEEE Trans Microw Theory Tech, 2019, 67, 505 doi: 10.1109/TMTT.2018.2876826[66] Yeh Y L, Chang H Y. Design and analysis of a W-band divide-by-three injection-locked frequency divider using second harmonic enhancement technique. IEEE Trans Microw Theory Tech, 2012, 60, 1617 doi: 10.1109/TMTT.2012.2189244[67] Ghilioni A, Mazzanti A, Svelto F. Analysis and design of mm-wave frequency dividers based on dynamic latches with load modulation. IEEE J Solid-State Circuits, 2013, 48, 1842 doi: 10.1109/JSSC.2013.2258793[68] Hussein A I, Paramesh J. Design and self-calibration techniques for inductor-less millimeter-wave frequency dividers. IEEE J Solid-State Circuits, 2017, 52, 1521 doi: 10.1109/JSSC.2017.2681801[69] Chen Y, Yang Z S, Zhao X T, et al. A 6.5 × 7 μm2 0.98-to-1.5 mW nonself-oscillation-mode frequency divider-by-2 achieving a single-band untuned locking range of 166.6% (4–44 GHz). IEEE Solid-State Circuits Lett, 2019, 2, 37 doi: 10.1109/LSSC.2019.2920226[70] Krishna M V, Jain A, Quadir N A, et al. A 1V 2mW 17GHz multi-modulus frequency divider based on TSPC logic using 65nm CMOS. 40th Eur Solid State Circuits Conf ESSCIRC, 2014, 431[71] Park D, Lee W, Jeon S, et al. A 2.5-GHz 860μW charge-recycling fractional-N frequency synthesizer in 130nm CMOS. 2008 IEEE Symp VLSI Circuits, 2008, 88[72] Chang C H, Yang C Y, Lee Y, et al. A 3.4mW 2.3-to-2.7GHz frequency synthesizer in 0.18-µm CMOS. 2013 Proceedings of the ESSCIRC (ESSCIRC), 2013, 53[73] Moon J W, Kim S G, Kwon D H, et al. A 0.4-V, 500-MHz, ultra-low-power phase-locked loop for near-threshold voltage operation. Proceedings of the IEEE 2014 Custom Integrated Circuits Conference, 2014, 1[74] Moon J W, Choi K C, Choi W Y. A 0.4-V, 90~350-MHz PLL with an active loop-filter charge pump. IEEE Trans Circuits Syst II, 2014, 61, 319 doi: 10.1109/TCSII.2014.2312800[75] Cheng K H, Tsai Y C, Lo Y L, et al. A 0.5-V 0.4–2.24-GHz inductorless phase-locked loop in a system-on-chip. IEEE Trans Circuits Syst I, 2011, 58, 849 doi: 10.1109/TCSI.2010.2089559[76] Lo Y L, Yang W B, Chao T S, et al. Designing an ultralow-voltage phase-locked loop using a bulk-driven technique. IEEE Trans Circuits Syst II, 2009, 56, 339 doi: 10.1109/TCSII.2009.2019160[77] Ikeda S, Kamimura T, Lee S, et al. A sub-1mW 5.5-GHz PLL with digitally-calibrated ILFD and linearized varactor for low supply voltage operation. 2013 IEEE Radio Freq Integr Circuits Symp RFIC, 2013, 439[78] Hsieh H H, Lu C T, Lu L H. A 0.5-V 1.9-GHz low-power phase-locked loop in 0.18-μm CMOS. 2007 IEEE Symp VLSI Circuits, 2007, 164[79] Ikeda S, Lee S Y, Ito H, et al. A 0.5 V 5.96-GHz PLL with amplitude-regulated current-reuse VCO. IEEE Microw Wirel Compon Lett, 2017, 27, 302 doi: 10.1109/LMWC.2017.2662001[80] Gangasani G R, Kinget P R. A 0.5 V, 9-GHz sub-integer frequency synthesizer using multi-phase injection-locked prescaler for phase-switching-based programmable division with automatic injection-lock calibration in 45-nm CMOS. IEEE Trans Circuits Syst II, 2019, 66, 803 doi: 10.1109/TCSII.2019.2910075[81] Hegazi E, Abidi A A. Varactor characteristics, oscillator tuning curves, and AM-FM conversion. IEEE J Solid-State Circuits, 2003, 38, 1033 doi: 10.1109/JSSC.2003.811968[82] Lin T H, Kaiser W J. A 900-MHz 2.5-mA CMOS frequency synthesizer with an automatic SC tuning loop. IEEE J Solid-State Circuits, 2001, 36, 424 doi: 10.1109/4.910481[83] Aktas A, Ismail M. CMOS PLL calibration techniques. IEEE Circuits Devices Mag, 2004, 20, 6 doi: 10.1109/MCD.2004.1343243[84] Lin T H, Lai Y J. An agile VCO frequency calibration technique for a 10-GHz CMOS PLL. IEEE J Solid-State Circuits, 2007, 42, 340 doi: 10.1109/JSSC.2006.889360[85] Lee J, Kim K, Lee J, et al. A 480-MHz to 1-GHz sub-picosecond clock generator with a fast and accurate automatic frequency calibration in 0.13-µm CMOS. 2007 IEEE Asian Solid-State Circuits Conf, 2007, 67[86] Huang D P, Li W, Zhou J, et al. A frequency synthesizer with optimally coupled QVCO and harmonic-rejection SSBmixer for multi-standard wireless receiver. IEEE J Solid-State Circuits, 2011, 46, 1307 doi: 10.1109/JSSC.2011.2124970[87] Shin J, Shin H. A fast and high-precision VCO frequency calibration technique for wideband ΔΣ fractional-N frequency synthesizers. IEEE Trans Circuits Syst I, 2010, 57, 1573 doi: 10.1109/TCSI.2009.2036057[88] Shin J, Shin H. A 1.9–3.8 GHz ΔΣ fractional-N PLL frequency synthesizer with fast auto-calibration of loop bandwidth and VCO frequency. IEEE J Solid-State Circuits, 2012, 47, 665 doi: 10.1109/JSSC.2011.2179733[89] Lu L, Gong Z C, Liao Y C, et al. A 975-to-1960MHz fast-locking fractional-N synthesizer with adaptive bandwidth control and 4/4.5 prescaler for digital TV tuners. 2009 IEEE International Solid-State Circuits Conference, 2009, 396[90] Zhang Z, Yang J C, Liu L Y, et al. A fast auto-frequency calibration technique for wideband PLL with wide reference frequency range. 2018 IEEE Asian Solid-State Circuits Conf (A-SSCC), 2018, 227[91] Hu A, Liu D S, Zhang K F, et al. A 0.045- to 2.5- GHz frequency synthesizer with TDC-based AFC and phase switching multi-modulus divider. 2019 IEEE 62nd Int Midwest Symp Circuits Syst MWSCAS, 2019, 722[92] Li C Y, Lee C L, Hu M H, et al. A fast locking-in and low jitter PLLWith a process-immune locking-in monitor. IEEE Trans Very Large Scale Integr VLSI Syst, 2014, 22, 2216 doi: 10.1109/TVLSI.2013.2285977[93] Zhao B, Lian Y, Yang H Z. A low-power fast-settling bond-wire frequency synthesizer with a dynamic-bandwidth scheme. IEEE Trans Circuits Syst I, 2013, 60, 1188 doi: 10.1109/TCSI.2013.2249177[94] Kuang X F, Wu N J. A fast-settling PLL frequency synthesizer with direct frequency presetting. 2006 IEEE International Solid State Circuits Conference, 2006, 741[95] Yan X Z, Kuang X F, Wu N J. A smart frequency presetting technique for fast lock-in LC-PLL frequency synthesizer. 2009 IEEE Int Symp Circuits Syst, 2009, 1525[96] Liu X D, Feng P, Liu L Y, et al. Low power low phase noise phase locked loop frequency synthesizer with fast locking mode for 2.4 GHz applications. Jpn J Appl Phys, 2014, 53, 04EE18 doi: 10.7567/JJAP.53.04EE18[97] Chiu W H, Huang Y H, Lin T H. A dynamic phase error compensation technique for fast-locking phase-locked loops. IEEE J Solid-State Circuits, 2010, 45, 1137 doi: 10.1109/JSSC.2010.2046235[98] Siriburanon T, Liu H L, Nakata K, et al. A 28-GHz fractional-N frequency synthesizer with reference and frequency doublers for 5G cellular. 41st Eur Solid-State Circuits Conf ESSCIRC, 2015, 76[99] Hsueh Y L, Cho L C, Shen C H, et al. A 0.29mm2 frequency synthesizer in 40nm CMOS with 0.19psrms jitter and –100dBc reference spur for 802.11ac. 2014 IEEE International Solid-State Circuits (ISSCC), 2014, 472[100] Zhang G. Linearised charge pump independent of current mismatch through timing rearrangement. Electron Lett, 2010, 46, 33 doi: 10.1049/el.2010.2555[101] Tang Z W, Wan X X, Wang M G, et al. A 50-to-930MHz quadrature-output fractional-N frequency synthesizer with 770-to-1860MHz single-inductor LC-VCO and without noise folding effect for multistandard DTV tuners. 2013 IEEE International Solid-State Circuits Conference, 2013, 358[102] Jee D W, Suh Y, Kim B, et al. A FIR-embedded phase interpolator based noise filtering for wide-bandwidth fractional-N PLL. IEEE J Solid-State Circuits, 2013, 48, 2795 doi: 10.1109/JSSC.2013.2282620[103] Kao T K, Liang C F, Chiu H H, et al. A wideband fractional-N ring PLL with fractional-spur suppression using spectrally shaped segmentation. 2013 IEEE International Solid-State Circuits Conference, 2013, 416[104] Heng C H, Song B S. A 1.8-GHz CMOS fractional-N frequency synthesizer with randomized multiphase VCO. IEEE J Solid-State Circuits, 2003, 38, 848 doi: 10.1109/JSSC.2003.811872[105] Hung C C, Liu S I. A noise filtering technique for fractional-N frequency synthesizers. IEEE Trans Circuits Syst II, 2011, 58, 139 doi: 10.1109/TCSII.2011.2110390[106] Park P, Park D, Cho S. A 2.4 GHz fractional-N frequency synthesizer with high-OSR ΔΣ modulator and nested PLL. IEEE J Solid-State Circuits, 2012, 47, 2433 doi: 10.1109/JSSC.2012.2209809[107] Song F, Zhao Y, Wu B, et al. A fractional-N synthesizer with 110fsrms jitter and a reference quadrupler for wideband 802.11ax. 2019 IEEE International Solid- State Circuits Conference (ISSCC), 2019, 264[108] Park D, Cho S. A 14.2 mW 2.55-to-3 GHz cascaded PLL with reference injection and 800 MHz delta-sigma modulator in 0.13 μm CMOS. IEEE J Solid-State Circuits, 2012, 47, 2989 doi: 10.1109/JSSC.2012.2217856[109] Nandwana R K, Anand T, Saxena S, et al. A calibration-free fractional-N ring PLL using hybrid phase/current-mode phase interpolation method. IEEE J Solid-State Circuits, 2015, 50, 882 doi: 10.1109/JSSC.2014.2385756[110] Gupta M, Song B S. A 1.8-GHz spur-cancelled fractional-N frequency synthesizer with LMS-based DAC gain calibration. IEEE J Solid-State Circuits, 2006, 41, 2842 doi: 10.1109/JSSC.2006.884829[111] Swaminathan A, Wang K J, Galton I. A wide-bandwidth 2.4 GHz ISM band fractional-N PLL with adaptive phase noise cancellation. IEEE J Solid-State Circuits, 2007, 42, 2639 doi: 10.1109/JSSC.2007.908763[112] Zhang Y, Mueller J H, Mohr B, et al. A wideband fractional-N synthesizer with low effort adaptive phase noise cancellation for low-power short-range standards. 2015 IEEE Radio Freq Integr Circuits Symp RFIC, 2015, 71[113] Meninger S E, Perrott M H. A 1-MHz bandwidth 3.6-GHz 0.18-μm CMOS fractional-N synthesizer utilizing a hybrid PFD/DAC structure for reduced broadband phase noise. IEEE J Solid-State Circuits, 2006, 41, 966 doi: 10.1109/JSSC.2006.870894[114] Jian H Y, Xu Z W, Wu Y C, et al. A fractional-N PLL for multiband (0.8–6 GHz) communications using binary-weighted D/A differentiator and offset-frequency Δ-Σ modulator. IEEE J Solid-State Circuits, 2010, 45, 768 doi: 10.1109/JSSC.2010.2040232[115] Liang C F, Wang P Y. A wideband fractional-N ring PLL using a near-ground pre-distorted switched-capacitor loop filter. 2015 IEEE International Solid-State Circuits Conference (ISSCC), 2015, 1[116] Yu X Y, Sun Y F, Rhee W, et al. An FIR-embedded noise filtering method for ΔΣ fractional-N PLL clock generators. IEEE J Solid-State Circuits, 2009, 44, 2426 doi: 10.1109/JSSC.2009.2021086[117] Yu X Y, Sun Y F, Rhee W, et al. A ΔΣ fractional-N synthesizer with customized noise shaping for WCDMA/HSDPA applications. IEEE J Solid-State Circuits, 2009, 44, 2193 doi: 10.1109/JSSC.2009.2022301[118] Kong L, Razavi B. A 2.4-GHz RF fractional-N synthesizer with BW = 0.25fREF. IEEE J Solid-State Circuits, 2018, 53, 1707 doi: 10.1109/JSSC.2018.2796544[119] Sanyal A, Sun N, Yu X Y, et al. Fractional-N PLL with multi-element fractional divider for noise reduction. Electron Lett, 2016, 52, 809 doi: 10.1049/el.2016.0680[120] Zhang Y L, Sanyal A, Yu X Y, et al. A fractional-N PLL with space–time averaging for quantization noise reduction. IEEE J Solid-State Circuits, 2020, 55, 602 doi: 10.1109/JSSC.2019.2950154[121] Hu Y Z, Chen X, Siriburanon T, et al. A 21.7-to-26.5GHz charge-sharing locking quadrature PLL with implicit digital frequency-tracking loop achieving 75fs jitter and −250dB FoM. 2020 IEEE International Solid- State Circuits Conference (ISSCC), 2020, 276[122] Turker D, Bekele A, Upadhyaya P, et al. A 7.4-to-14GHz PLL with 54fsrms jitter in 16nm FinFET for integrated RF-data-converter SoCs. 2018 IEEE International Solid-State Circuits Conference (ISSCC), 2018, 378[123] Lee J, Wang H D. Study of subharmonically injection-locked PLLs. IEEE J Solid-State Circuits, 2009, 44, 1539 doi: 10.1109/JSSC.2009.2016701[124] Zhang Z, Yang J C, Liu L Y, et al. An 18–23 GHz 57.4-fs RMS jitter −253.5-dB FoM sub-harmonically injection-locked all-digital PLL with single-ended injection technique and ILFD aided adaptive injection timing alignment technique. IEEE Trans Circuits Syst I, 2019, 66, 3733 doi: 10.1109/TCSI.2019.2911531[125] Huang Y C, Liu S I. A 2.4-GHz subharmonically injection-locked PLL with self-calibrated injection timing. IEEE J Solid-State Circuits, 2013, 48, 417 doi: 10.1109/JSSC.2012.2227609[126] Wei C L, Kuan T K, Liu S I. A subharmonically injection-locked PLL with calibrated injection pulsewidth. IEEE Trans Circuits Syst II, 2015, 62, 548 doi: 10.1109/TCSII.2015.2407753[127] Liang C F, Hsiao K J. An injection-locked ring PLL with self-aligned injection window. 2011 IEEE International Solid-State Circuits Conference, 2011, 90[128] Lee I T, Chen Y J, Liu S I, et al. A divider-less sub-harmonically injection-locked PLL with self-adjusted injection timing. 2013 IEEE International Solid-State Circuits Conference, 2013, 414[129] Zhang Z, Liu L Y, Wu N J. A novel 2.4-to-3.6 GHz wideband subharmonically injection-locked PLL with adaptively-aligned injection timing. 2014 IEEE Asian Solid-State Circuits Conf (A-SSCC), 2014, 369[130] Choi S, Yoo S, Lim Y, et al. A PVT-robust and low-jitter ring-VCO-based injection-locked clock multiplier with a continuous frequency-tracking loop using a replica-delay cell and a dual-edge phase detector. IEEE J Solid-State Circuits, 2016, 51, 1878 doi: 10.1109/JSSC.2016.2574804[131] Kim M, Choi S, Seong T, et al. A low-jitter and fractional-resolution injection-locked clock multiplier using a DLL-based real-time PVT calibrator with replica-delay cells. IEEE J Solid-State Circuits, 2016, 51, 401 doi: 10.1109/JSSC.2015.2496781[132] Lee D, Lee T, Kim Y J, et al. A 21%-jitter-improved self-aligned dividerless injection-locked PLL with a VCO control voltage ripple-compensated phase detector. IEEE Trans Circuits Syst II, 2016, 63, 733 doi: 10.1109/TCSII.2016.2530098[133] Chang H Y, Yeh Y L, Liu Y C, et al. A low-jitter low-phase-noise 10-GHz sub-harmonically injection-locked PLL with self-aligned DLL in 65-nm CMOS technology. IEEE Trans Microw Theory Tech, 2014, 62, 543 doi: 10.1109/TMTT.2014.2302747[134] Chang H Y, Chan C C, Shen I Y E, et al. Design and analysis of CMOS low-phase-noise low-jitter subharmonically injection-locked VCO with FLL self-alignment technique. IEEE Trans Microw Theory Tech, 2016, 64, 4632 doi: 10.1109/TMTT.2016.2623784[135] Huang K, Wang Z Q, Zheng X Q, et al. A 80 mW 40 Gb/s transmitter with automatic serializing time window search and 2-tap pre-emphasis in 65 nm CMOS technology. IEEE Trans Circuits Syst I, 2015, 62, 1441 doi: 10.1109/TCSI.2015.2411791[136] Yoo S, Choi S, Kim J, et al. A low-integrated-phase-noise 27–30-GHz injection-locked frequency multiplier with an ultra-low-power frequency-tracking loop for mm-wave-band 5G transceivers. IEEE J Solid-State Circuits, 2018, 53, 375 doi: 10.1109/JSSC.2017.2749420[137] Yoon H, Park S, Choi J. A low-jitter injection-locked multi-frequency generator using digitally controlled oscillators and time-interleaved calibration. IEEE J Solid-State Circuits, 2019, 54, 1564 doi: 10.1109/JSSC.2019.2893513[138] Yoon H, Kim J, Park S, et al. A −31dBc integrated-phase-noise 29GHz fractional-N frequency synthesizer supporting multiple frequency bands for backward-compatible 5G using a frequency doubler and injection-locked frequency multipliers. 2018 IEEE International Solid-State Circuits Conference (ISSCC), 2018, 366[139] Choi S, Yoo S, Lee Y, et al. An ultra-low-jitter 22.8-GHz ring-LC-hybrid injection-locked clock multiplier with a multiplication factor of 114. IEEE J Solid-State Circuits, 2019, 54, 927 doi: 10.1109/JSSC.2018.2883090[140] Shin D, Koh K J. An injection frequency-locked loop: Autonomous injection frequency tracking loop with phase noise self-calibration for power-efficient mm-wave signal sources. IEEE J Solid-State Circuits, 2018, 53, 825 doi: 10.1109/JSSC.2017.2782762[141] Yoo S, Choi S, Lee Y, et al. A 140fsrms-jitter and –72dBc-reference-spur ring-VCO-based injection-locked clock multiplier using a background triple-point frequency/phase/slope calibrator. 2019 IEEE International Solid-State Circuits Conference (ISSCC), 2019, 490[142] Liu X L, Luong H C. A fully integrated 0.27-THz injection-locked frequency synthesizer with frequency-tracking loop in 65-nm CMOS. IEEE J Solid-State Circuits, 2020, 55, 1051 doi: 10.1109/JSSC.2019.2954232[143] Tseng Y H, Yeh C W, Liu S I. A 2.25–2.7 GHz area-efficient subharmonically injection-locked fractional-N frequency synthesizer with a fast-converging correlation loop. IEEE Trans Circuits Syst I, 2017, 64, 811 doi: 10.1109/TCSI.2016.2620151[144] Yang J C, Zhang Z, Qi N, et al. 2.4–3.2 GHz robust self-injecting injection-locked phase-locked loop. Jpn J Appl Phys, 2018, 57, 04FF05 doi: 10.7567/JJAP.57.04FF05[145] Zhang H S, Narayanan A T, Herdian H, et al. 0.2mW 70fs rms-jitter injection-locked PLL using de-sensitized SSPD-based injecting-time self-alignment achieving –270dB FoM and –66dBc reference spur. 2019 Symposium on VLSI Circuits, 2019, C38[146] Yang J C, Zhang Z, Qi N, et al. A 0.45-to-1.8 GHz synthesized injection-locked bang-bang phase locked loop with fine frequency tuning circuits. Sci China Inf Sci, 2019, 62, 62405 doi: 10.1007/s11432-018-9423-y[147] Lin C Y, Hung Y T, Lin T H. A 2.4-GHz 500-µW 370-fsrms integrated jitter sub-sampling sub-harmonically injection-locked PLL in 90-nm CMOS. 2019 IEEE Asian Solid-State Circuits Conference (A-SSCC), 2019, 91[148] Gao X, Klumperink E A M, Bohsali M, et al. A low noise sub-sampling PLL in which divider noise is eliminated and PD/CP noise is not multiplied by N2. IEEE J Solid-State Circuits, 2009, 44, 3253 doi: 10.1109/JSSC.2009.2032723[149] Gao X, Klumperink E A M, Socci G, et al. Spur reduction techniques for phase-locked loops exploiting A sub-sampling phase detector. IEEE J Solid-State Circuits, 2010, 45, 1809 doi: 10.1109/JSSC.2010.2053094[150] Gao X, Klumperink E, Socci G, et al. A 2.2GHz sub-sampling PLL with 0.16psrms jitter and −125dBc/Hz in-band phase noise at 700µW loop-components power. 2010 Symposium on VLSI Circuits, 139[151] Szortyka V, Shi Q X, Raczkowski K, et al. A 42 mW 200 fs-jitter 60 GHz sub-sampling PLL in 40 nm CMOS. IEEE J Solid-State Circuits, 2015, 50, 2025 doi: 10.1109/JSSC.2015.2442998[152] Sharkia A, Mirabbasi S, Shekhar S. A type-I sub-sampling PLL with a 100 × 100 μm2 footprint and –255-dB FOM. IEEE J Solid-State Circuits, 2018, 53, 3553 doi: 10.1109/JSSC.2018.2874013[153] Yang X F, Chan C H, Zhu Y, et al. A −246dB jitter-FoM 2.4GHz calibration-free ring-oscillator PLL achieving 9% jitter variation over PVT. 2019 IEEE International Solid- State Circuits Conference (ISSCC), 2019, 260[154] Hsu C W, Tripurari K, Yu S A, et al. A sub-sampling-assisted phase-frequency detector for low-noise PLLs with robust operation under supply interference. IEEE Trans Circuits Syst I, 2015, 62, 90 doi: 10.1109/TCSI.2014.2359719[155] Lee D G, Mercier P P. A sub-mW 2.4-GHz active-mixer-adopted sub-sampling PLL achieving an FoM of –256 dB. IEEE J Solid-State Circuits, 2019, 1 doi: 10.1109/JSSC.2019.2951377[156] Qian Y C, Chao Y, Liu S I. A sub-sampling PLL with robust operation under supply interference and short re-locking time. 2019 IEEE Asian Solid-State Circuits Conference (A-SSCC), 2019, 95[157] Jiang B W, Luong H C. A 23-mW 60-GHz differential sub-sampling PLL with an NMOS-only differential-inductively-tuned VCO. 2019 IEEE Asian Solid-State Circuits Conference (A-SSCC), 2019, 279[158] Siriburanon T, Kondo S, Katsuragi M, et al. A low-power low-noise mm-wave subsampling PLL using dual-step-mixing ILFD and tail-coupling quadrature injection-locked oscillator for IEEE 802.11ad. IEEE J Solid-State Circuits, 2016, 51, 1246 doi: 10.1109/JSSC.2016.2529004[159] Wang H, Momeni O. A 9.6 mW low-noise millimeter-wave sub-sampling PLL with a divider-less sub-sampling lock detector in 65 nm CMOS. 2019 IEEE Radio Freq Integr Circuits Symp RFIC, 2019, 171[160] Yi X, Liang Z P, Feng G Y, et al. A 93.4-to-104.8 GHz 57 mW fractional-N cascaded sub-sampling PLL with true in-phase injection-coupled QVCO in 65 nm CMOS. 2016 IEEE Radio Freq Integr Circuits Symp RFIC, 2016, 122[161] Lee S, Takano K, Hara S, et al. A −40-dBc integrated-phase-noise 45-GHz sub-sampling PLL with 3.9-dBm output and 2.1% DC-to-RF efficiency. 2019 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), 2019, 175[162] El-Halwagy W, Nag A, Hisayasu P, et al. A 28-GHz quadrature fractional-N frequency synthesizer for 5G transceivers with less than 100-fs jitter based on cascaded PLL architecture. IEEE Trans Microw Theory Tech, 2017, 65, 396 doi: 10.1109/TMTT.2016.2647698[163] Ting H H, Lee T C. A 5.25GHz subsampling PLL with a VCO-phase-noise suppression technique. 2020 IEEE International Solid- State Circuits Conference (ISSCC), 2020, 390[164] Nagam S S, Kinget P R. A low-jitter ring-oscillator phase-locked loop using feedforward noise cancellation with a sub-sampling phase detector. IEEE J Solid-State Circuits, 2018, 53, 703 doi: 10.1109/JSSC.2017.2788876[165] Kim J, Lim Y, Yoon H, et al. An ultra-low-jitter, mmW-band frequency synthesizer based on digital subsampling PLL using optimally spaced voltage comparators. IEEE J Solid-State Circuits, 2019, 54, 3466 doi: 10.1109/JSSC.2019.2936765[166] Yang Z S, Chen Y, Yang S H, et al. A 25.4-to-29.5GHz 10.2mW isolated sub-sampling PLL achieving –252.9dB jitter-power FoM and –63dBc reference spur. 2019 IEEE International Solid- State Circuits Conference (ISSCC), 2019, 270[167] Zhang Z, Zhu G, Yue C P. A 0.65V 12-to-16GHz sub-sampling PLL with 56.4fsrms integrated jitter and –256.4dB FoM. 2019 IEEE International Solid-State Circuits Conference (ISSCC), 2019, 488[168] Zhang Z, Zhu G, Yue C P. A 0.65-V 12-16-GHz sub-sampling PLL with 56.4-fsrms integrated jitter and –256.4-dB FoM. IEEE J Solid-State Circuits, 2020, 55, 1665 doi: 10.1109/JSSC.2020.2967562[169] Lim Y, Kim J, Jo Y, et al. A 170MHz-lock-in-range and −253dB-FoM jitter 12-to-14.5GHz subsampling PLL with a 150µW frequency-disturbance-correcting loop using a low-power unevenly spaced edge generator. 2020 IEEE International Solid- State Circuits Conference (ISSCC), 2020, 280[170] Liao D Y, Dai F F, Nauta B, et al. A 2.4-GHz 16-phase sub-sampling fractional-N PLL with robust soft loop switching. IEEE J Solid-State Circuits, 2018, 53, 715 doi: 10.1109/JSSC.2018.2791486[171] Liao D Y, Wang R X, Dai F F. A low-noise inductor-less fractional-N sub-sampling PLL with multi-ring oscillator. 2017 IEEE Radio Freq Integr Circuits Symp RFIC, 2017, 108[172] Chang W S, Huang P C, Lee T C. A fractional-N divider-less phase-locked loop with a subsampling phase detector. IEEE J Solid-State Circuits, 2014, 49, 2964 doi: 10.1109/JSSC.2014.2359670[173] Bajestan M M, Attah H, Entesari K. A 2.8–4.3GHz wideband fractional-N sub-sampling synthesizer with −112.5dBc/Hz in-band phase noise. 2016 IEEE Radio Freq Integr Circuits Symp RFIC, 2016, 126[174] Narayanan A T, Katsuragi M, Kimura K, et al. A fractional-N sub-sampling PLL using a pipelined phase-interpolator with an FoM of –250 dB. IEEE J Solid-State Circuits, 2016, 51, 1630 doi: 10.1109/JSSC.2016.2539344[175] Raczkowski K, Markulic N, Hershberg B, et al. A 9.2–12.7 GHz wideband fractional-N subsampling PLL in 28 nm CMOS with 280 fs RMS jitter. IEEE J Solid-State Circuits, 2015, 50, 1203 doi: 10.1109/JSSC.2015.2403373[176] Markulic N, Raczkowski K, Martens E, et al. A DTC-based subsampling PLL capable of self-calibrated fractional synthesis and two-point modulation. IEEE J Solid-State Circuits, 2016, 51, 3078 doi: 10.1109/JSSC.2016.2596766[177] Markulic N, Renukaswamy P T, Martens E, et al. A 5.5-GHz background-calibrated subsampling polar transmitter with –41.3-dB EVM at 1024 QAM in 28-nm CMOS. IEEE J Solid-State Circuits, 2019, 54, 1059 doi: 10.1109/JSSC.2018.2886324[178] Shi Q X, Bunsen K, Markulic N, et al. A self-calibrated 16-GHz subsampling-PLL-based fast-chirp FMCW modulator with 1.5-GHz bandwidth. IEEE J Solid-State Circuits, 2019, 54, 3503 doi: 10.1109/JSSC.2019.2941113[179] Renukaswamy P T, Markulic N, Park S, et al. A 12mW 10GHz FMCW PLL based on an integrating DAC with 90kHz rms frequency error for 23MHz/µs slope and 1.2GHz chirp bandwidth. 2020 IEEE International Solid- State Circuits Conference (ISSCC), 2020, 278[180] Siriburanon T, Kondo S, Kimura K, et al. A 2.2 GHz –242 dB-FOM 4.2 mW ADC-PLL using digital sub-sampling architecture. IEEE J Solid-State Circuits, 2016, 51, 1385 doi: 10.1109/JSSC.2016.2546304[181] Chen Z Z, Wang Y H, Shin J, et al. Sub-sampling all-digital fractional-N frequency synthesizer with −111dBc/Hz in-band phase noise and an FOM of −242dB. 2015 IEEE International Solid-State Circuits Conference (ISSCC), 2015, 1[182] Chang W S, Lee T C. A 5 GHz fractional-N ADC-based digital phase-locked loops with –243.8 dB FOM. IEEE Trans Circuits Syst I, 2016, 63, 1845 doi: 10.1109/TCSI.2016.2599516[183] Liu M L, Ma R, Liu S B, et al. A 5-GHz low-power low-noise integer-N digital subsampling PLL with SAR ADC PD. IEEE Trans Microw Theory Tech, 2018, 66, 4078 doi: 10.1109/TMTT.2018.2840987[184] Liao D Y, Zhang Y C, Dai F F, et al. An mm-wave synthesizer with robust locking reference-sampling PLL and wide-range injection-locked VCO. IEEE J Solid-State Circuits, 2020, 55, 536 doi: 10.1109/JSSC.2019.2959513[185] Yang Z S, Chen Y, Mak P I, et al. A 0.003-mm2 440fsRMS-jitter and -64dBc-reference-spur ring-VCO-based type-I PLL using a current-reuse sampling phase detector in 28-nm CMOS. 2019 IEEE Asian Solid-State Circuits Conference (A-SSCC), 2019, 283[186] Ko C T, Kuan T K, Shen R P, et al. A 7-nm FinFET CMOS PLL with 388-fs jitter and –80-dBc reference spur featuring a track-and-hold charge pump and automatic loop gain control. IEEE J Solid-State Circuits, 2020, 55, 1043 doi: 10.1109/JSSC.2019.2959735[187] Sharma J, Krishnaswamy H. A 2.4-GHz reference-sampling phase-locked loop that simultaneously achieves low-noise and low-spur performance. IEEE J Solid-State Circuits, 2019, 54, 1407 doi: 10.1109/JSSC.2018.2889690[188] Raj M, Bekele A, Turker D, et al. A 164fsrms 9-to-18GHz sampling phase detector based PLL with in-band noise suppression and robust frequency acquisition in 16nm FinFET. 2017 Symposium on VLSI Circuits, 2017, 182[189] Gao X, Burg O, Wang H S, et al. A 2.7-to-4.3GHz, 0.16psrms-jitter, −246.8dB-FOM, digital fractional-N sampling PLL in 28nm CMOS. 2016 IEEE International Solid-State Circuits Conference (ISSCC), 2016, 174[190] Wu W H, Yao C W, Godbole K, et al. A 28-nm 75-fsrms analog fractional-N sampling PLL with a highly linear DTC incorporating background DTC gain calibration and reference clock duty cycle correction. IEEE J Solid-State Circuits, 2019, 54, 1254 doi: 10.1109/JSSC.2019.2899726[191] Mercandelli M, Santiccioli A, Parisi A, et al. A 12.5GHz fractional-N type-I sampling PLL achieving 58fs integrated jitter. 2020 IEEE International Solid-State Circuits Conference (ISSCC), 2020, 274[192] Tao J C, Heng C H. A 2.2-GHz 3.2-mW DTC-free sampling ΔΣ fractional-N PLL with –110-dBc/Hz in-band phase noise and –246-dB FoM and –83-dBc reference spur. IEEE Trans Circuits Syst I, 2019, 66, 3317 doi: 10.1109/TCSI.2019.2926326 -

Proportional views

DownLoad:

DownLoad: