| Citation: |

Jiaxin Liu, Xiyuan Tang, Linxiao Shen, Shaolan Li, Zhelu Li, Wenjuan Guo, Nan Sun. Error suppression techniques for energy-efficient high-resolution SAR ADCs[J]. Journal of Semiconductors, 2020, 41(11): 111403. doi: 10.1088/1674-4926/41/11/111403

****

J X Liu, X Y Tang, L X Shen, S L Li, Z L Li, W J Guo, N Sun, Error suppression techniques for energy-efficient high-resolution SAR ADCs[J]. J. Semicond., 2020, 41(11): 111403. doi: 10.1088/1674-4926/41/11/111403.

|

Error suppression techniques for energy-efficient high-resolution SAR ADCs

DOI: 10.1088/1674-4926/41/11/111403

More Information

-

Abstract

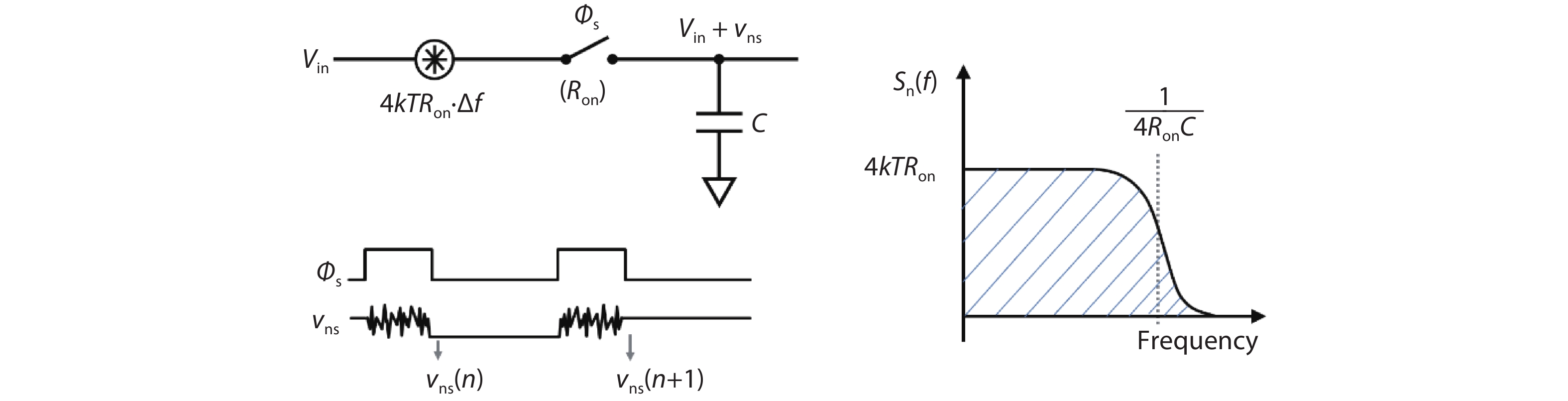

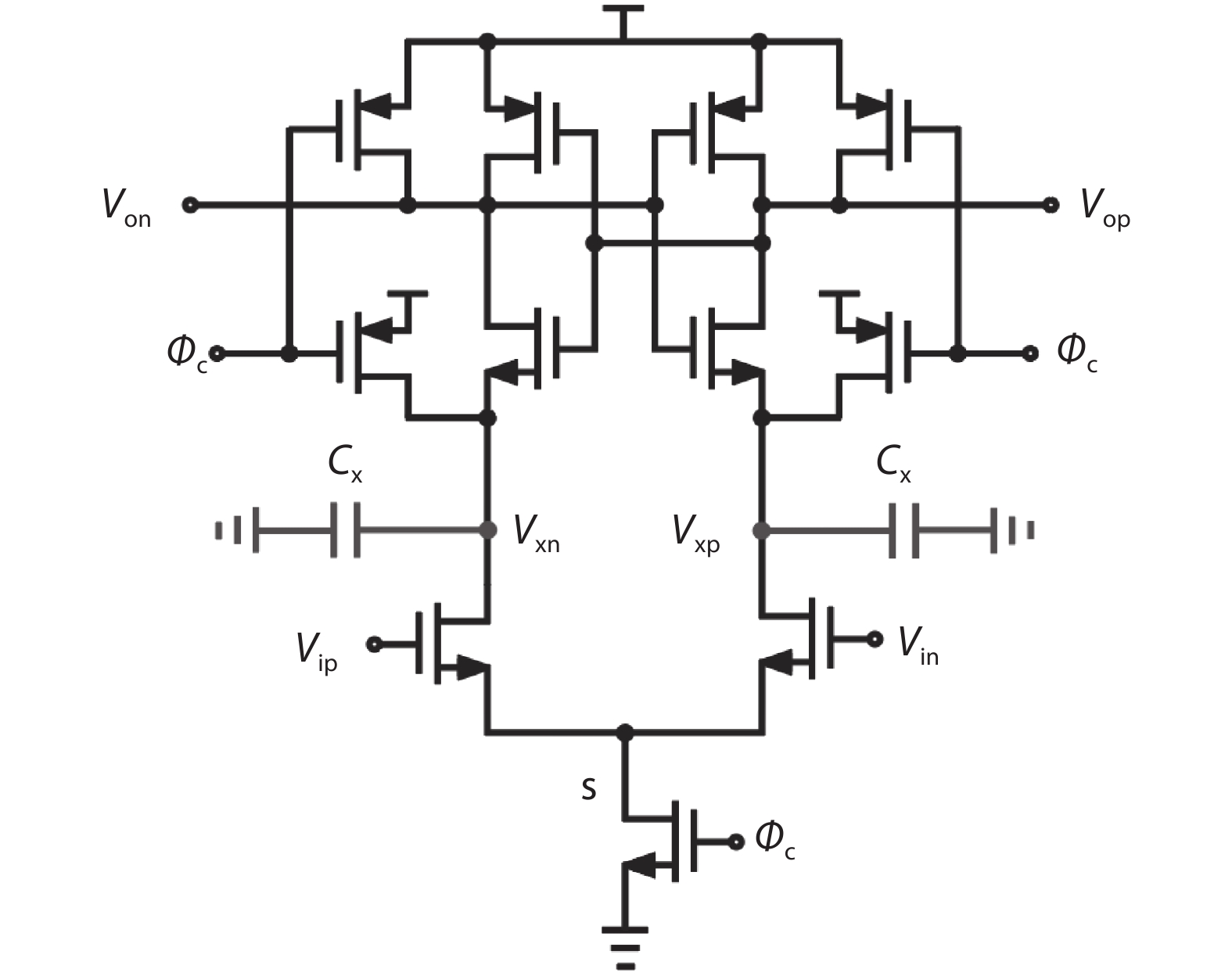

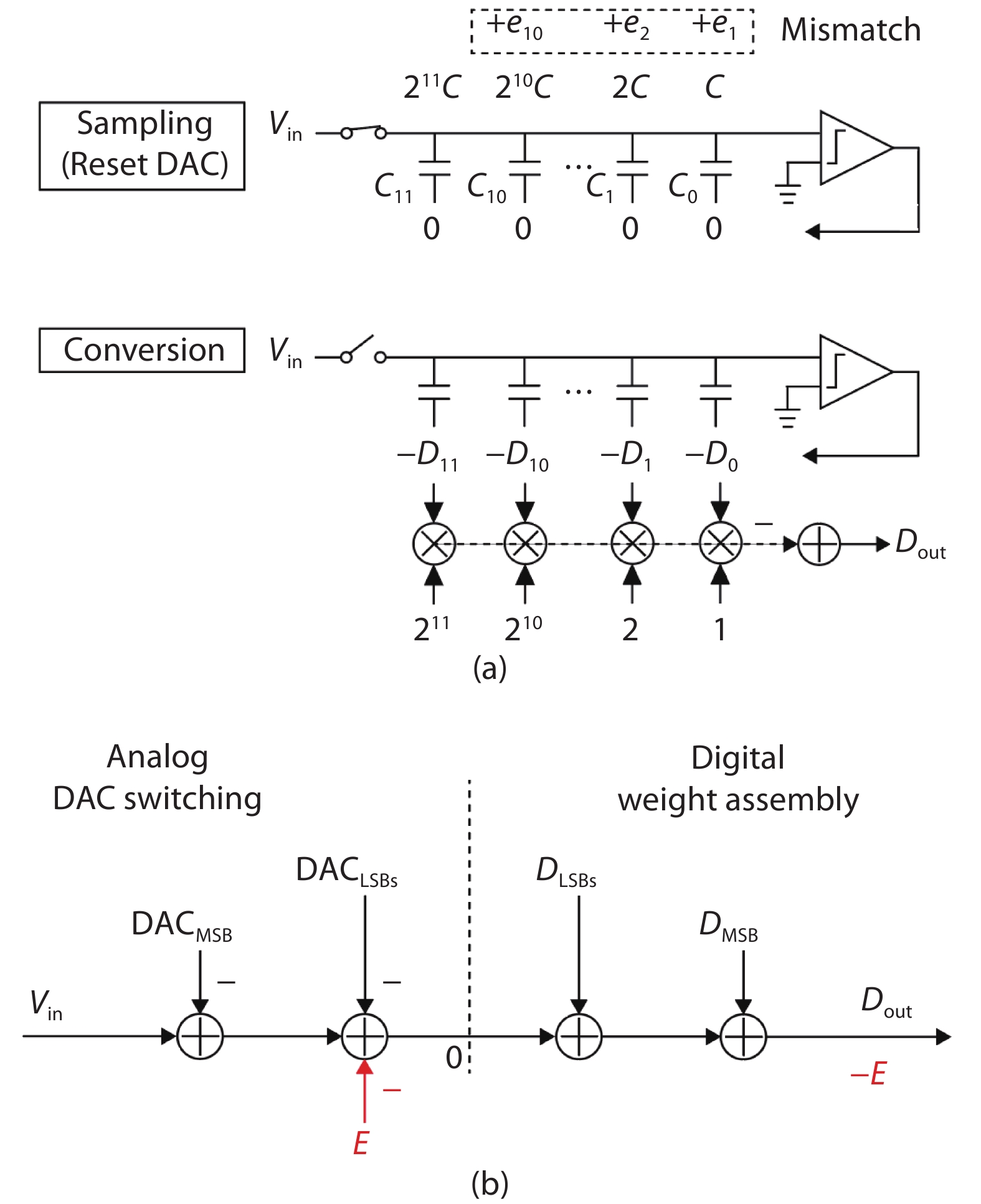

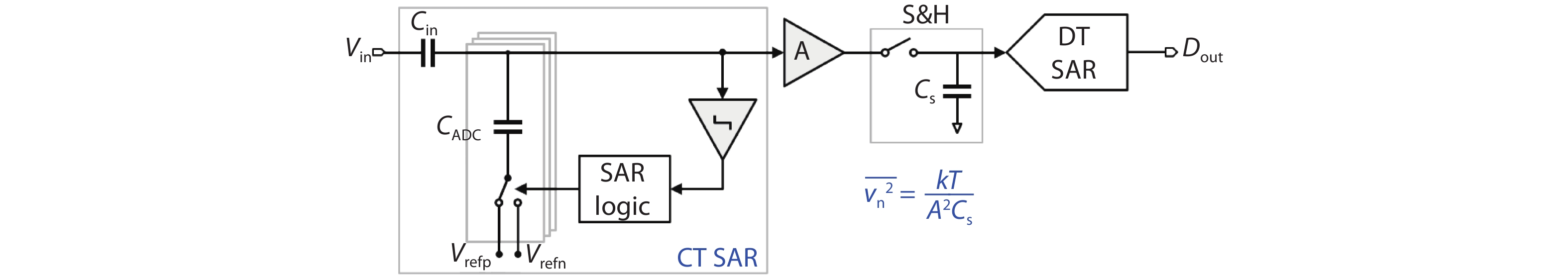

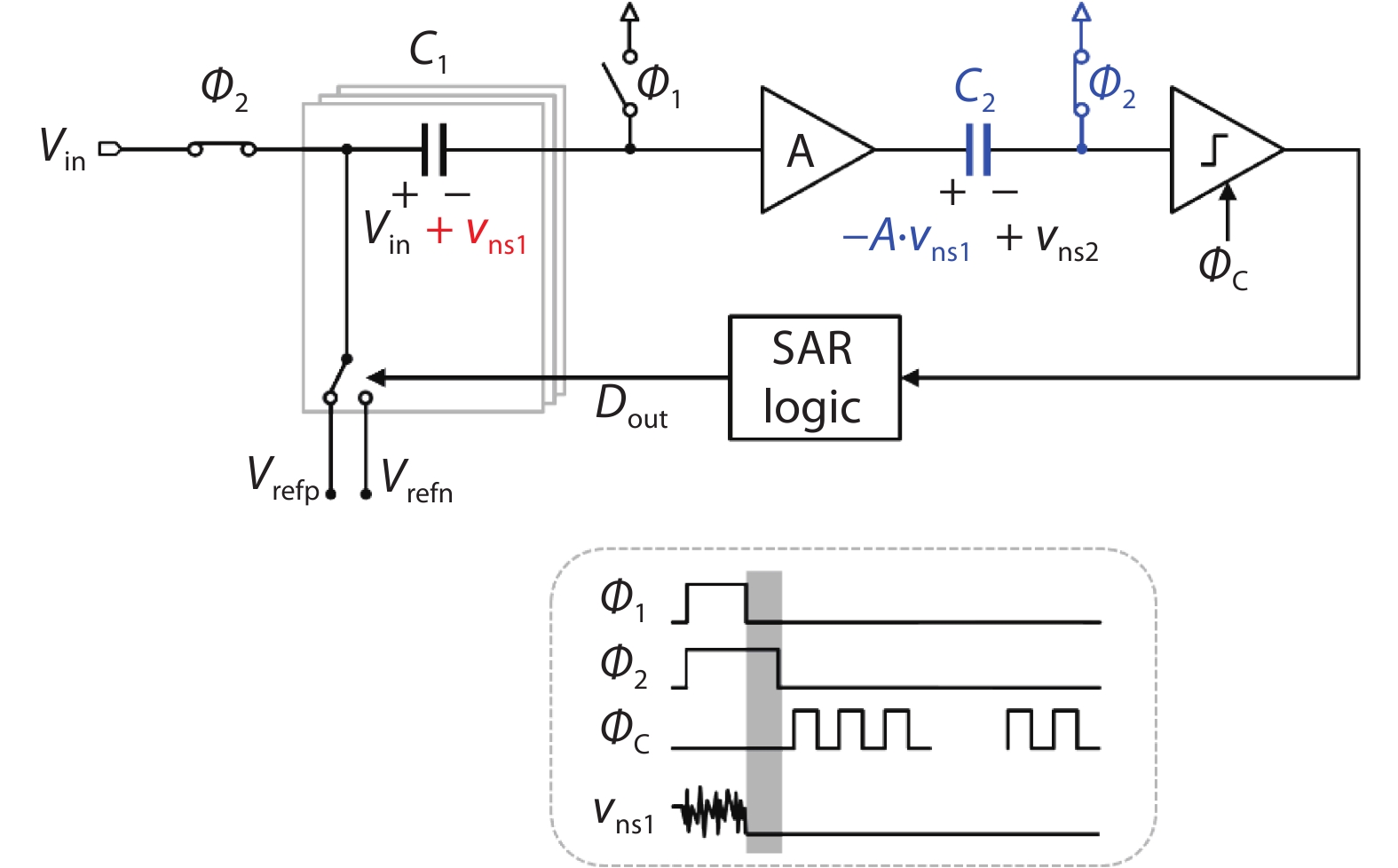

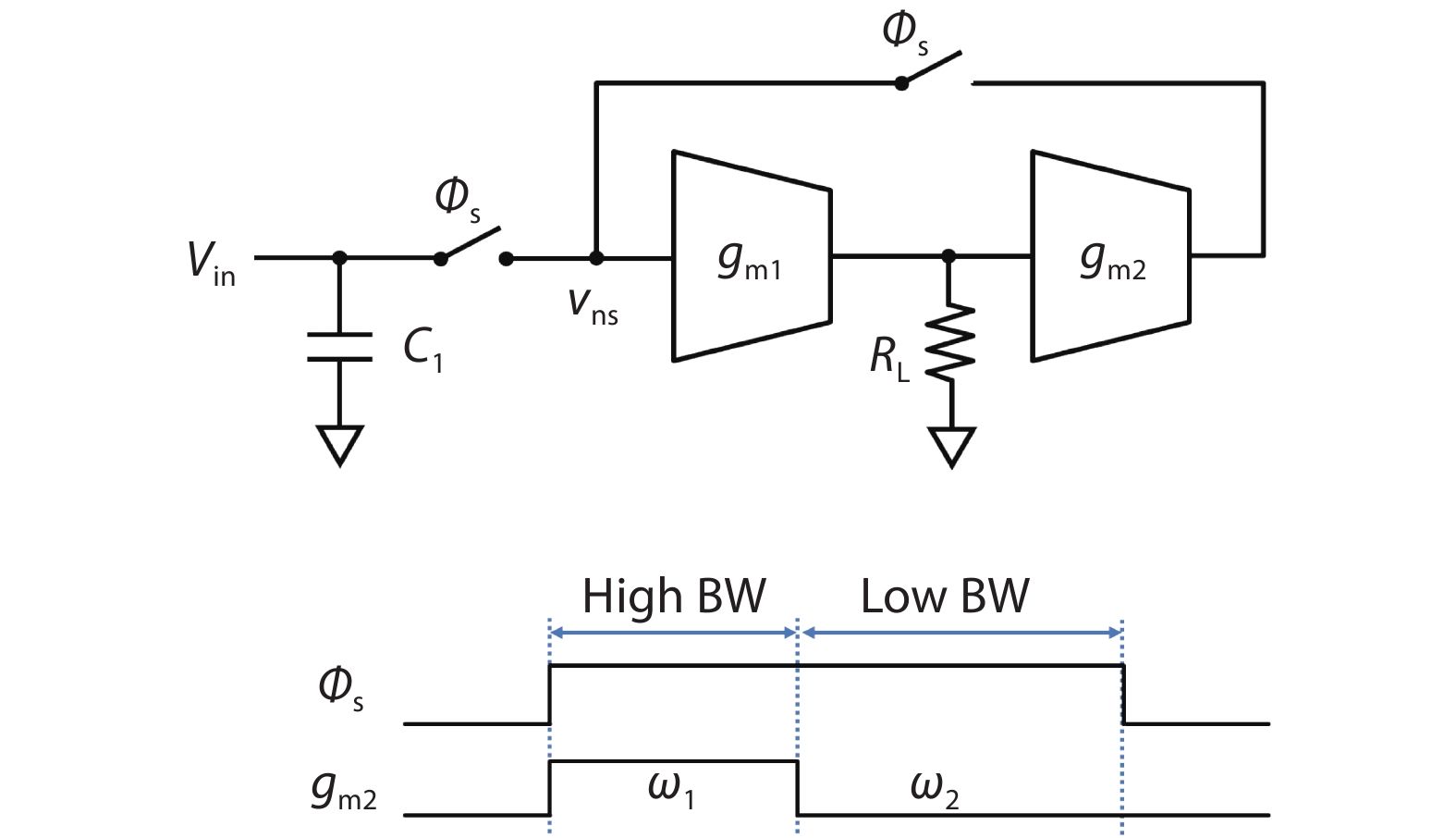

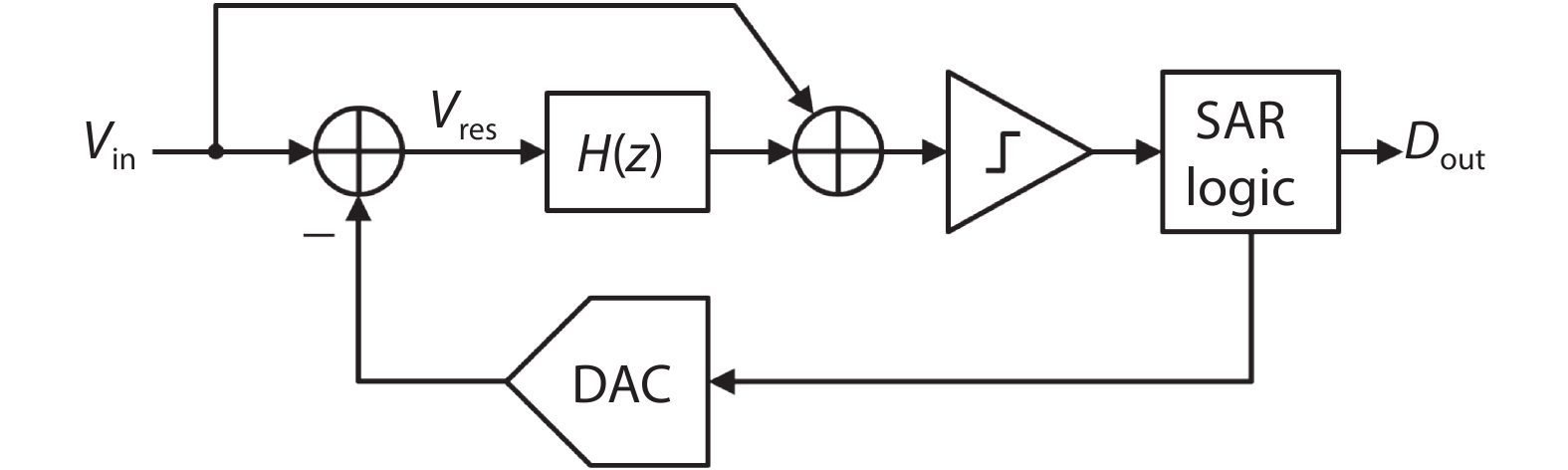

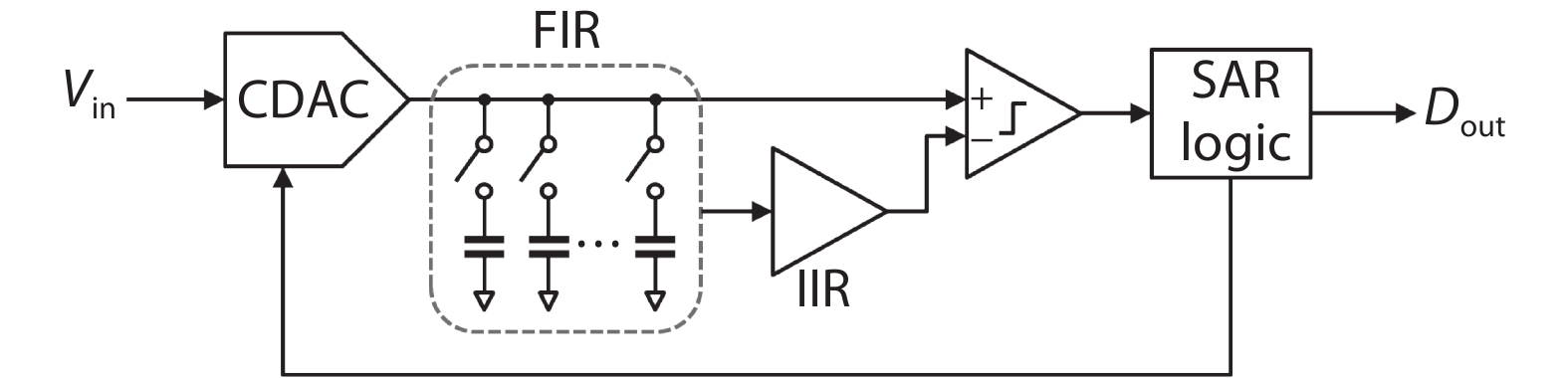

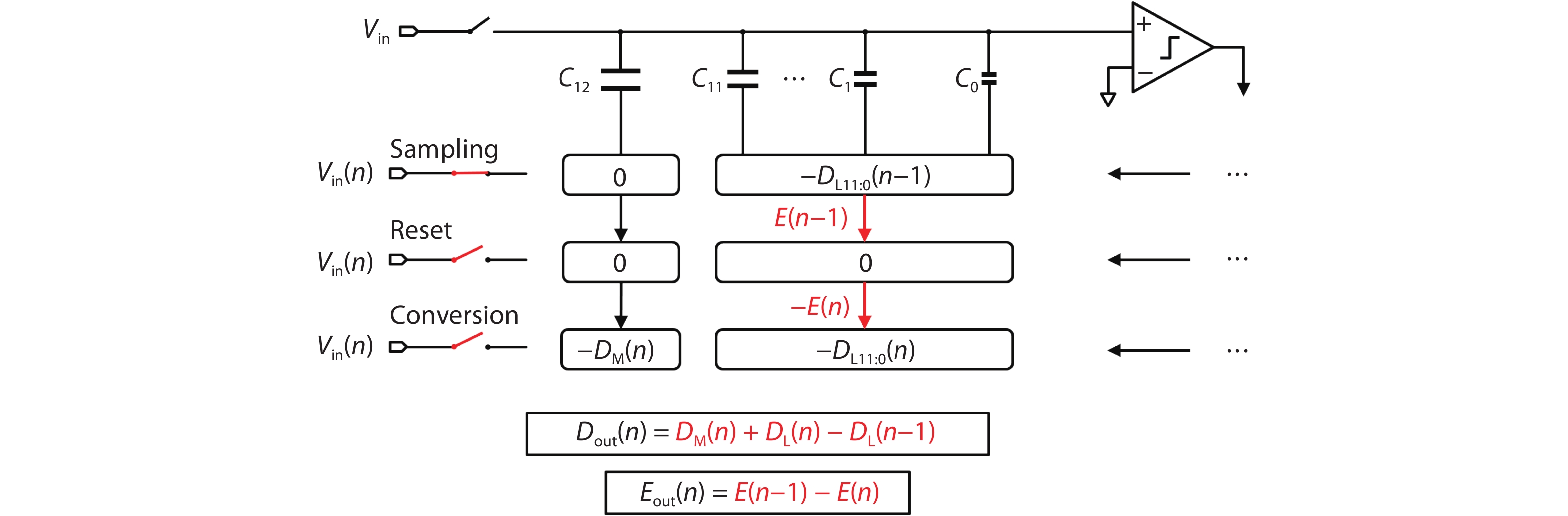

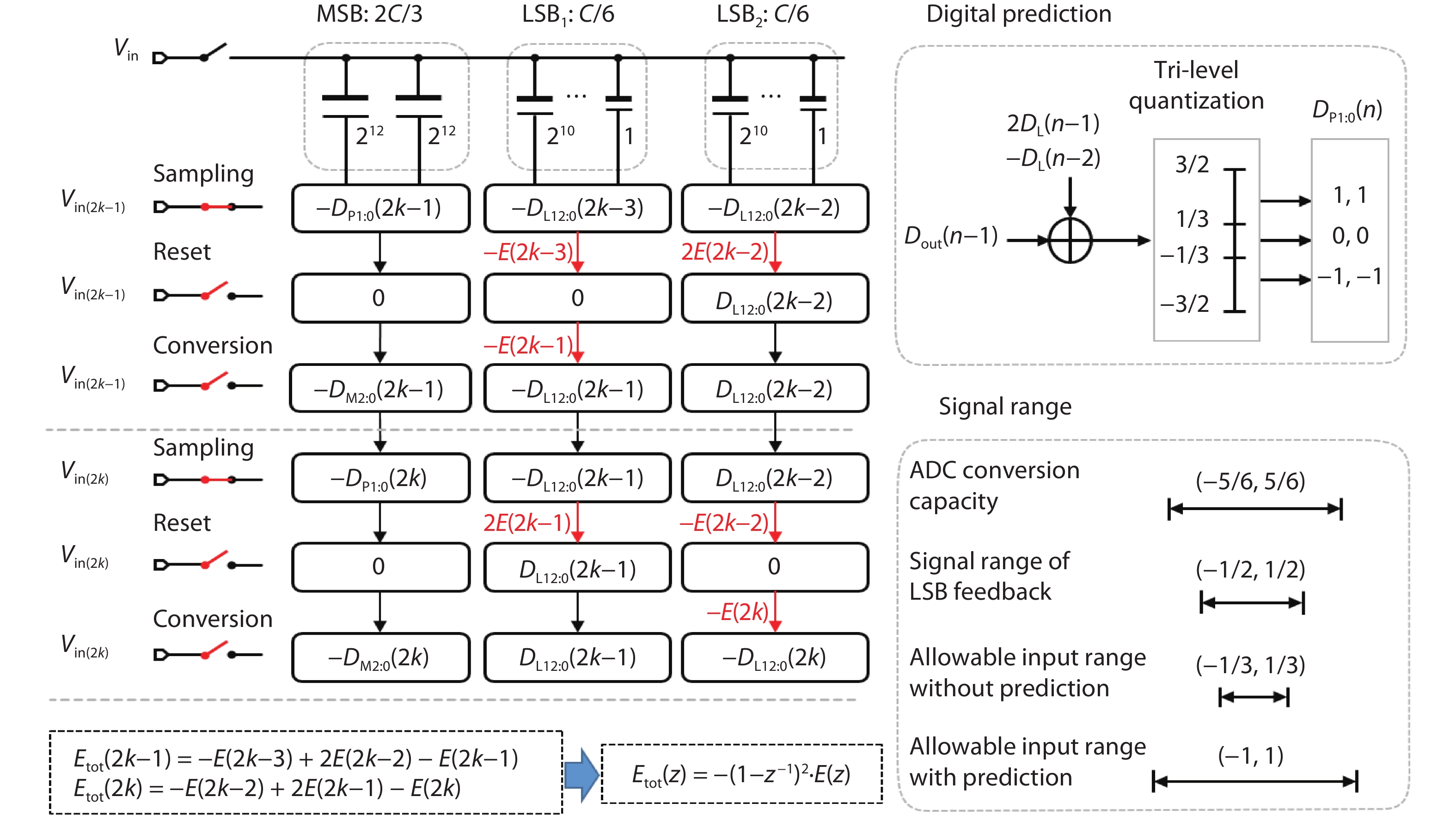

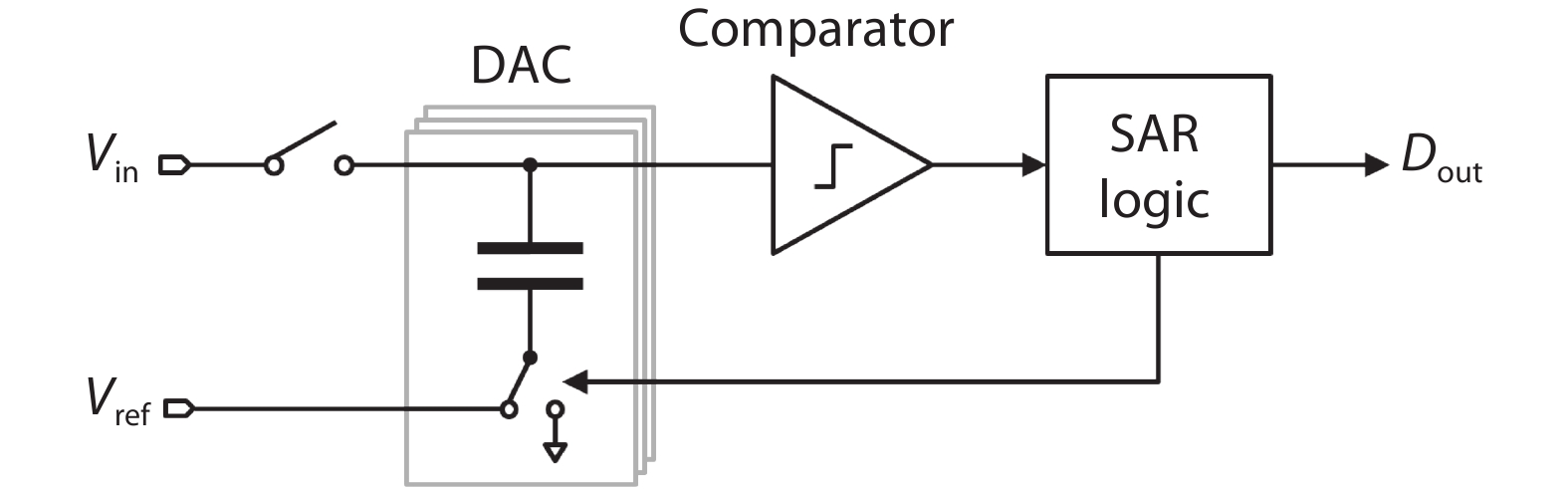

The successive approximation register (SAR) is one of the most energy-efficient analog-to-digital converter (ADC) architecture for medium-resolution applications. However, its high energy efficiency quickly diminishes when the target resolution increases. This is because a SAR ADC suffers from several major error source, including the sampling kT/C noise, the comparator noise, and the DAC mismatch. These errors are increasing hard to address in high-resolution SAR ADCs. This paper reviews recent advances on error suppression techniques for SAR ADCs, including the sampling kT/C noise reduction, the noise-shaping (NS) SAR, and the mismatch error shaping (MES). These techniques aim to boost the resolution of SAR ADCs while maintaining their superior energy efficiency. -

References

[1] Montanaro J, Witek R T, Anne K, et al. A 160-MHz, 32-b, 0.5-W CMOS RISC microprocessor. IEEE J Solid-State Circuits, 1996, 31, 1703 doi: 10.1109/JSSC.1996.542315[2] Nuzzo P, de Bernardinis F, Terreni P, et al. Noise analysis of regenerative comparators for reconfigurable ADC architectures. IEEE Trans Circuits Syst I, 2008, 55, 1441 doi: 10.1109/TCSI.2008.917991[3] Shen L X, Sun N, Shen Y, et al. A two-step ADC with a continuous-time SAR-based first stage. IEEE J Solid-State Circuits, 2019, 54, 3375 doi: 10.1109/JSSC.2019.2933951[4] Liu J X, Tang X Y, Zhao W D, et al. A 13b 0.005 mm2 40 MS/s SAR ADC with kT/C Noise Cancellation. 2020 IEEE International Solid- State Circuits Conference (ISSCC), 2020, 258[5] Poujois R, Baylac B, Barbier D, et al. Low-level MOS transistor amplifier using storage techniques. 1973 IEEE International Solid-State Circuits Conference, 1973, 152[6] Razavi B, Wooley B A. Design techniques for high-speed, high-resolution comparators. IEEE J Solid-State Circuits, 1992, 27, 1916 doi: 10.1109/4.173122[7] White M H, Lampe D R, Blaha F C, et al. Characterization of surface channel CCD image arrays at low light levels. IEEE J Solid-State Circuits, 1974, 9, 1 doi: 10.1109/JSSC.1974.1050448[8] Sugiki T, Ohsawa S, Miura H, et al. A 60 mW 10 b CMOS image sensor with column-to-column FPN reduction. 2000 IEEE International Solid-State Circuits Conference, 2000, 108[9] Yoshihara S, Nitta Y, Kikuchi M, et al. A 1/1.8-inch 6.4 MPixel 60 frames/s CMOS image sensor with seamless mode change. IEEE J Solid-State Circuits, 2006, 41, 2998 doi: 10.1109/JSSC.2006.884868[10] Kapusta R, Zhu H Y, Lyden C. Sampling circuits that break the kT/C thermal noise limit. IEEE J Solid-State Circuits, 2014, 49, 1694 doi: 10.1109/JSSC.2014.2320465[11] Li Z L, Dutta A, Mukherjee A, et al. A SAR ADC with reduced kT/C noise by decoupling noise PSD and BW. 2020 IEEE Symposium on VLSI Circuits, 2020, 1[12] Fredenburg J A, Flynn M P. A 90-MS/s 11-MHz-bandwidth 62-dB SNDR noise-shaping SAR ADC. IEEE J Solid-State Circuits, 2012, 47, 2898 doi: 10.1109/JSSC.2012.2217874[13] Shu Y S, Kuo L T, Lo T Y. An oversampling SAR ADC with DAC mismatch error shaping achieving 105 dB SFDR and 101 dB SNDR over 1 kHz BW in 55 nm CMOS. 2016 IEEE Int Solid-State Circuits Conf ISSCC, 2016, 458[14] Obata K, Matsukawa K, Miki T, et al. A 97.99 dB SNDR, 2 kHz BW, 37.1 μW noise-shaping SAR ADC with dynamic element matching and modulation dither effect. 2016 IEEE Symposium on VLSI Circuits (VLSI-Circuits), 2016, 1[15] Tang X Y, Yang X X, Zhao W D, et al. 9.5 A 13.5b-ENOB second-order noise-shaping SAR with PVT-robust closed-loop dynamic amplifier. 2020 IEEE International Solid-State Circuits Conference (ISSCC), 2020, 162[16] Liu C C, Huang M C. A 0.46 mW 5 MHz-BW 79.7 dB-SNDR noise-shaping SAR ADC with dynamic-amplifier-based FIR-IIR filter. 2017 IEEE International Solid-State Circuits Conference (ISSCC), 2017, 466[17] Li S L, Qiao B, Gandara M, et al. A 13-ENOB second-order noise-shaping SAR ADC realizing optimized NTF zeros using the error-feedback structure. IEEE J Solid-State Circuits, 2018, 53, 3484 doi: 10.1109/JSSC.2018.2871081[18] Jie L, Zheng B Y, Flynn M P. A calibration-free time-interleaved fourth-order noise-shaping SAR ADC. IEEE J Solid-State Circuits, 2019, 54, 3386 doi: 10.1109/JSSC.2019.2938626[19] Jie L, Zheng B, Chen H W, et al. 9.4 A 4th-order cascaded-noise-shaping SAR ADC with 88 dB SNDR over 100 kHz bandwidth. 2020 IEEE International Solid-State Circuits Conference (ISSCC), 2020, 160[20] Chen Z J, Miyahara M, Matsuzawa A. A 9.35-ENOB, 14.8 fJ/conv.-step fully-passive noise-shaping SAR ADC. 2015 Symposium on VLSI Circuits (VLSI Circuits), 2015, C64[21] Guo W J, Sun N. A 12b-ENOB 61μW noise-shaping SAR ADC with a passive integrator. ESSCIRC Conference 2016: 42nd European Solid-State Circuits Conference, 2016, 405[22] Zhuang H Y, Guo W J, Liu J X, et al. A second-order noise-shaping SAR ADC with passive integrator and tri-level voting. IEEE J Solid-State Circuits, 2019, 54, 1636 doi: 10.1109/JSSC.2019.2900150[23] Liu J X, Li S L, Guo W J, et al. A 0.029-mm2 17-fJ/conversion-step third-order CT ΔΣ ADC with a single OTA and second-order noise-shaping SAR quantizer. IEEE J Solid-State Circuits, 2019, 54, 428 doi: 10.1109/JSSC.2018.2879955[24] Chen Z J, Miyahara M, Matsuzawa A. A 2nd order fully-passive noise-shaping SAR ADC with embedded passive gain. 2016 IEEE Asian Solid-State Circuits Conference (A-SSCC), 2016, 309[25] Lin Y Z, Lin C, Tsou S C, et al. A 40 MHz-BW 320 MS/s passive noise-shaping SAR ADC with passive signal-residue summation in 14 nm FinFET. 2019 IEEE International Solid- State Circuits Conference (ISSCC), 2019, 330[26] Liu J X, Wang X, Gao Z J, et al. 9.3 A 40 kHz-BW 90 dB-SNDR noise-shaping SAR with 4 × passive gain and 2nd-order mismatch error shaping. 2020 IEEE International Solid-State Circuits Conference (ISSCC), 2020, 158[27] Liu J X, Hsu C K, Tang X Y, et al. Error-feedback mismatch error shaping for high-resolution data converters. IEEE Trans Circuits Syst I, 2019, 66, 1342 doi: 10.1109/TCSI.2018.2879582[28] Liu J, Wen G, Sun N. Second-order DAC MES for SAR ADCs. Electron Lett, 2017, 53, 1570 doi: 10.1049/el.2017.3138 -

Proportional views

DownLoad:

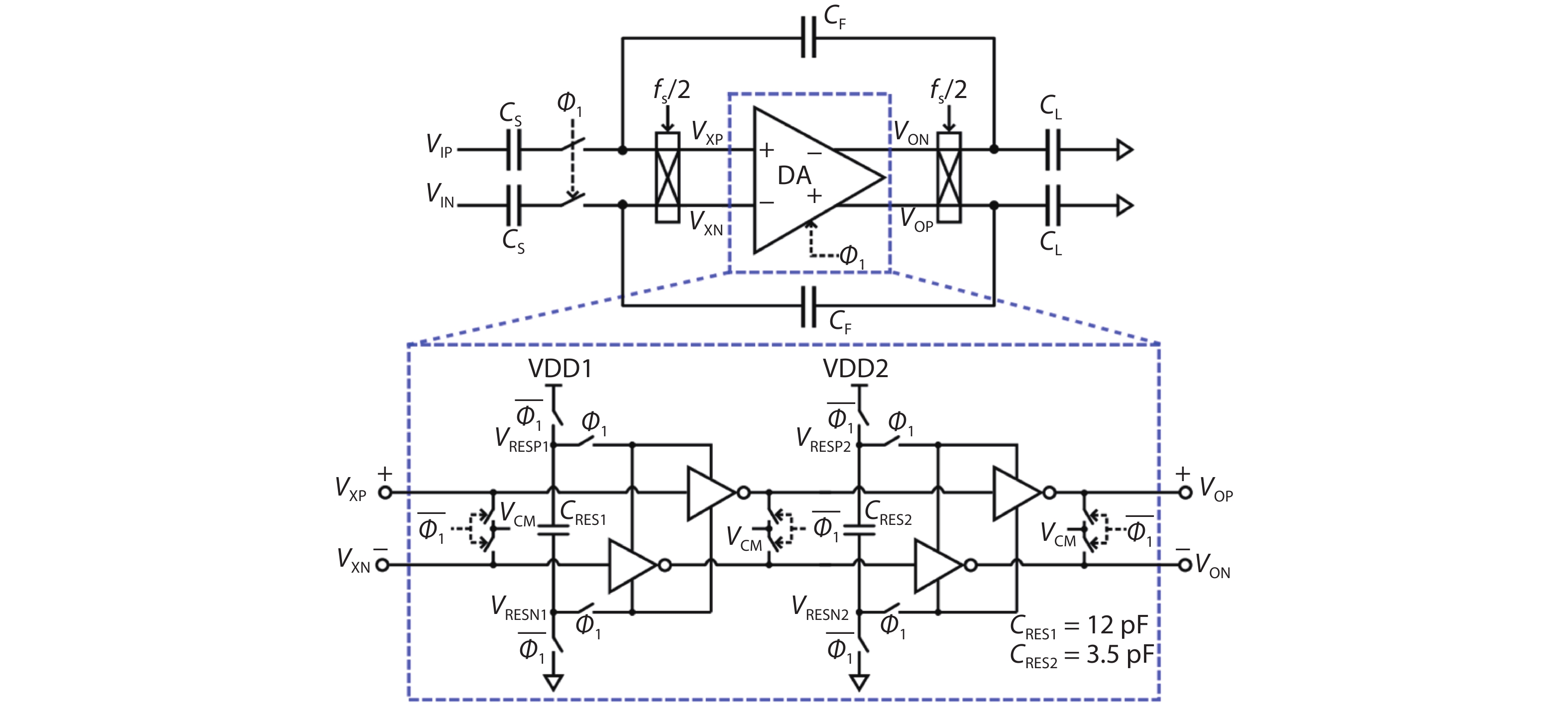

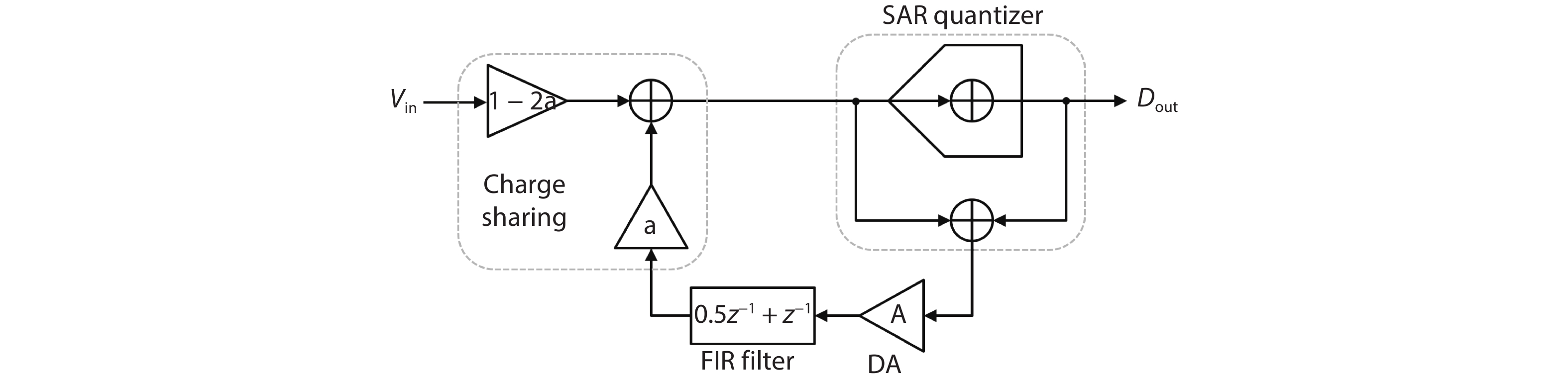

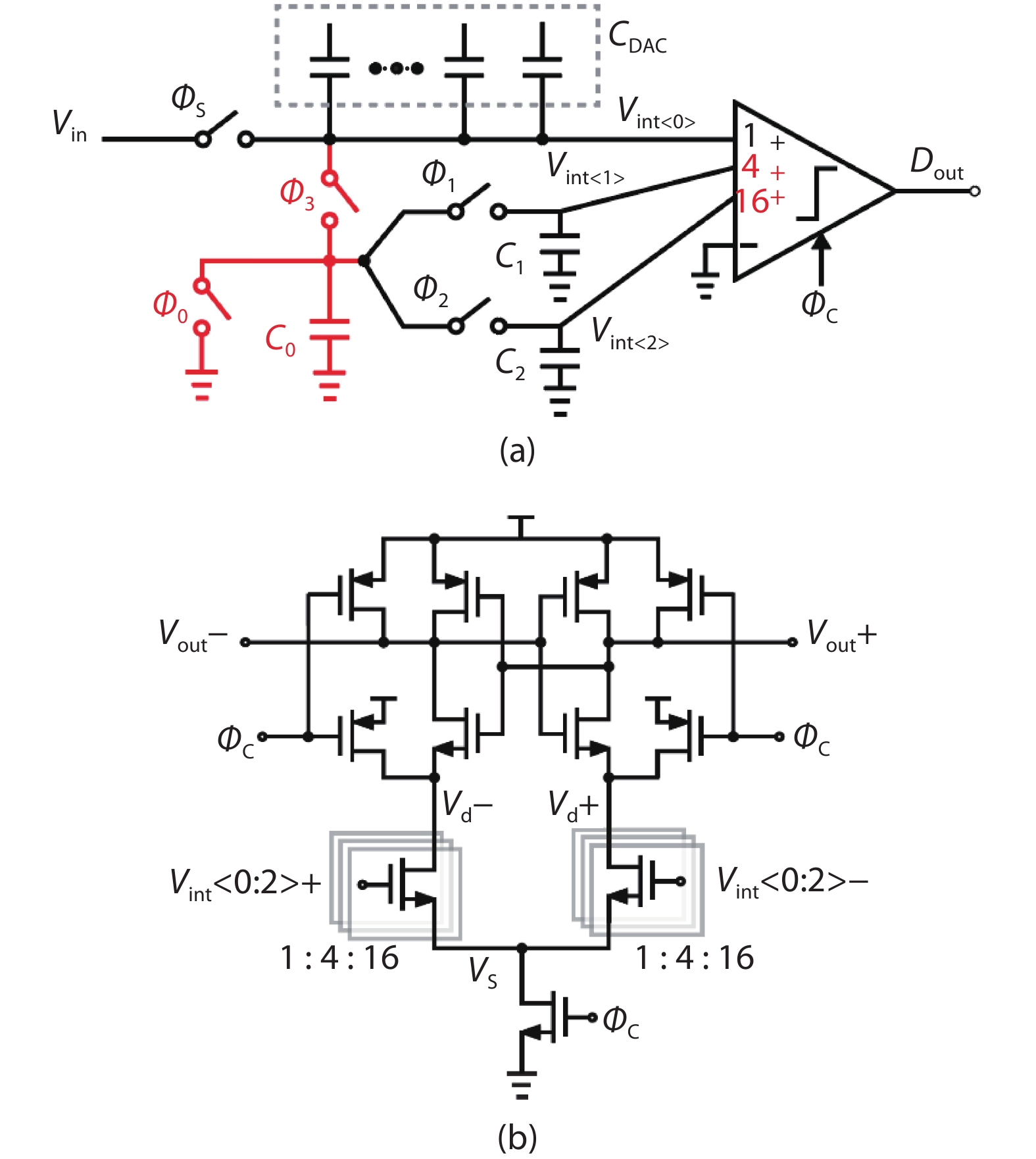

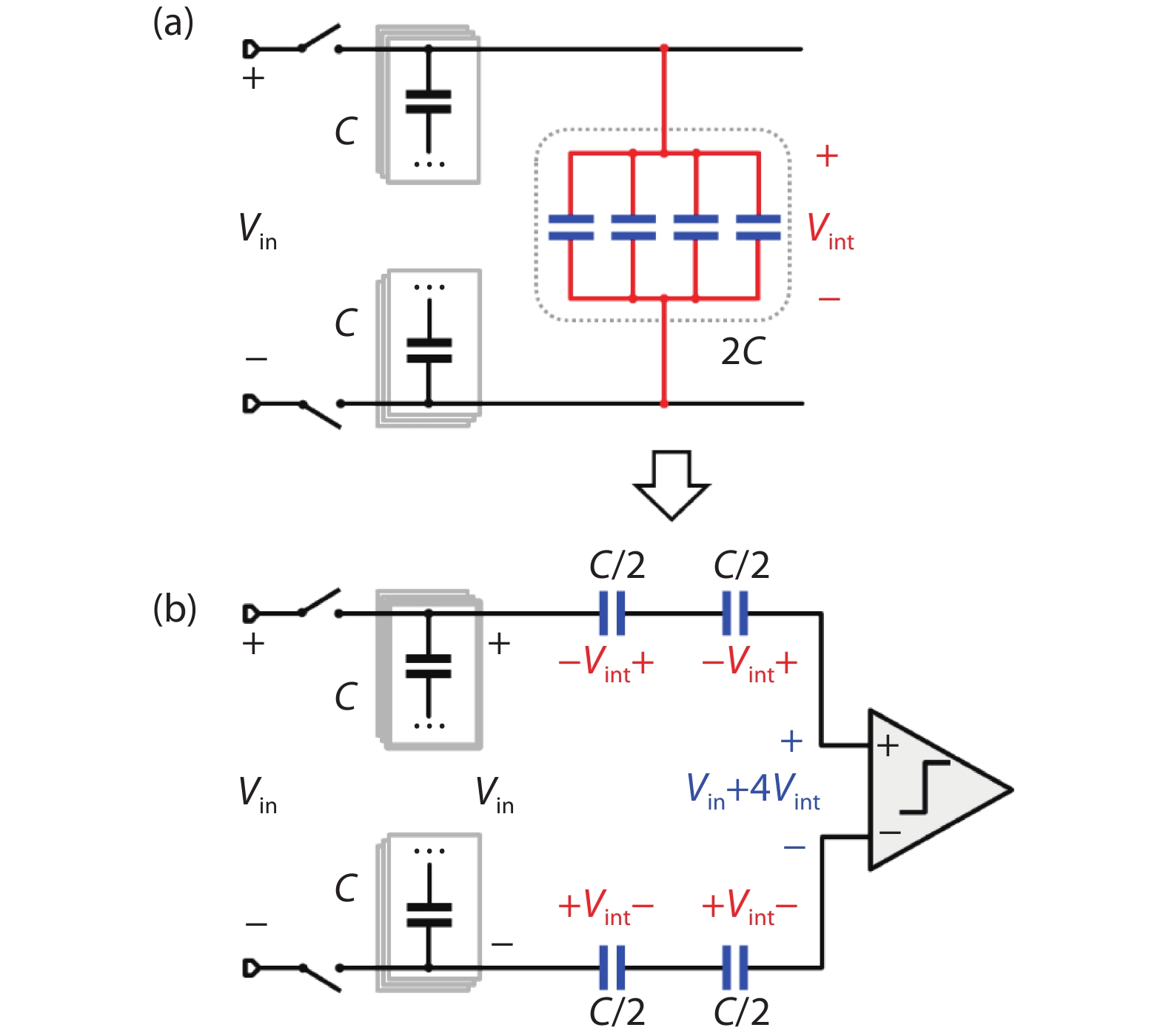

DownLoad: