| Citation: |

Xing Li, Lei Zhou. A survey of high-speed high-resolution current steering DACs[J]. Journal of Semiconductors, 2020, 41(11): 111404. doi: 10.1088/1674-4926/41/11/111404

****

X Li, L Zhou, A survey of high-speed high-resolution current steering DACs[J]. J. Semicond., 2020, 41(11): 111404. doi: 10.1088/1674-4926/41/11/111404.

|

A survey of high-speed high-resolution current steering DACs

DOI: 10.1088/1674-4926/41/11/111404

More Information

-

Abstract

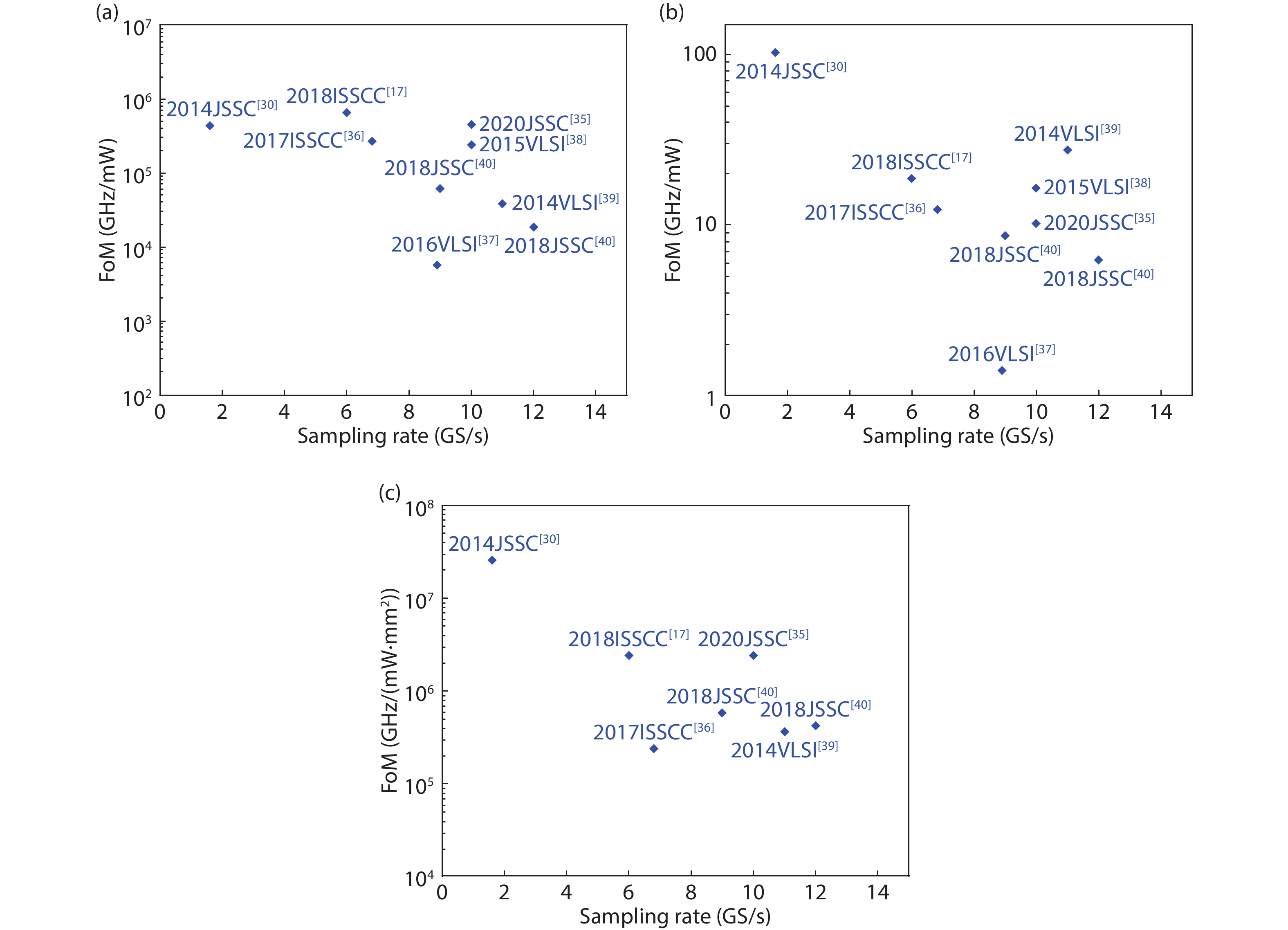

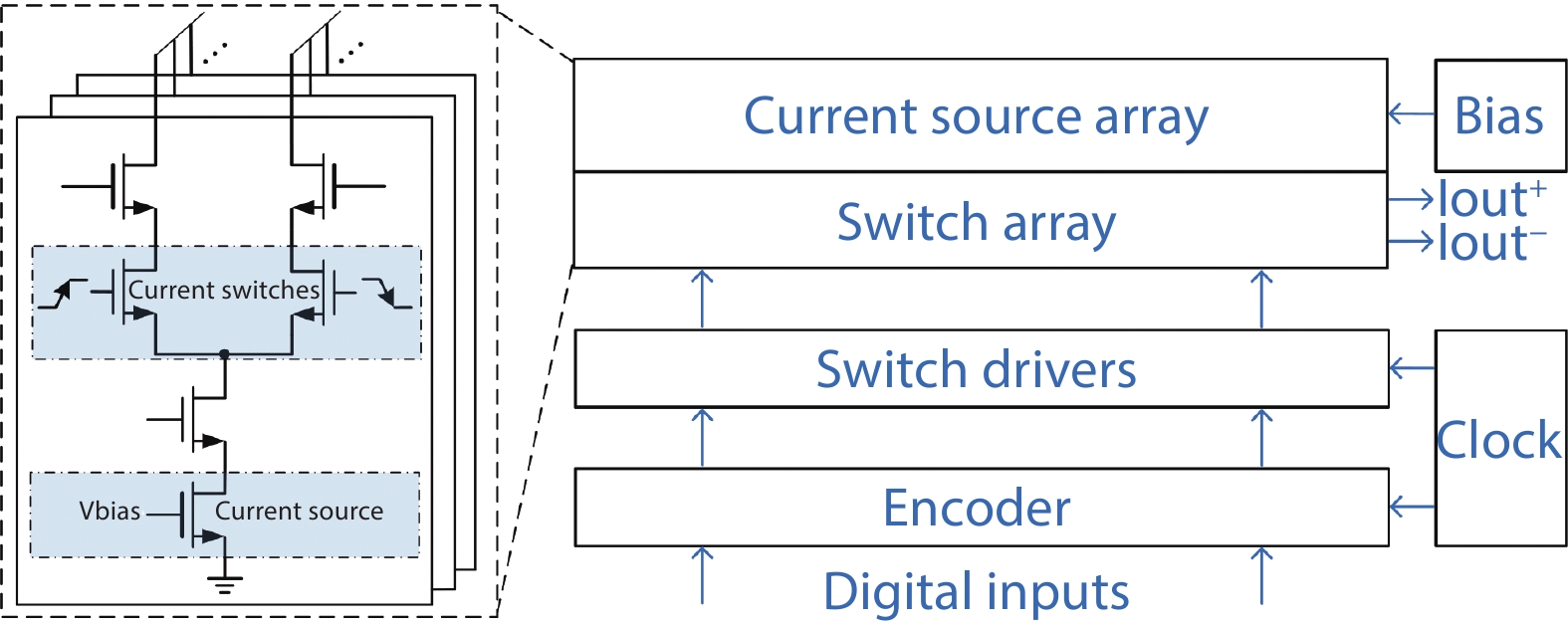

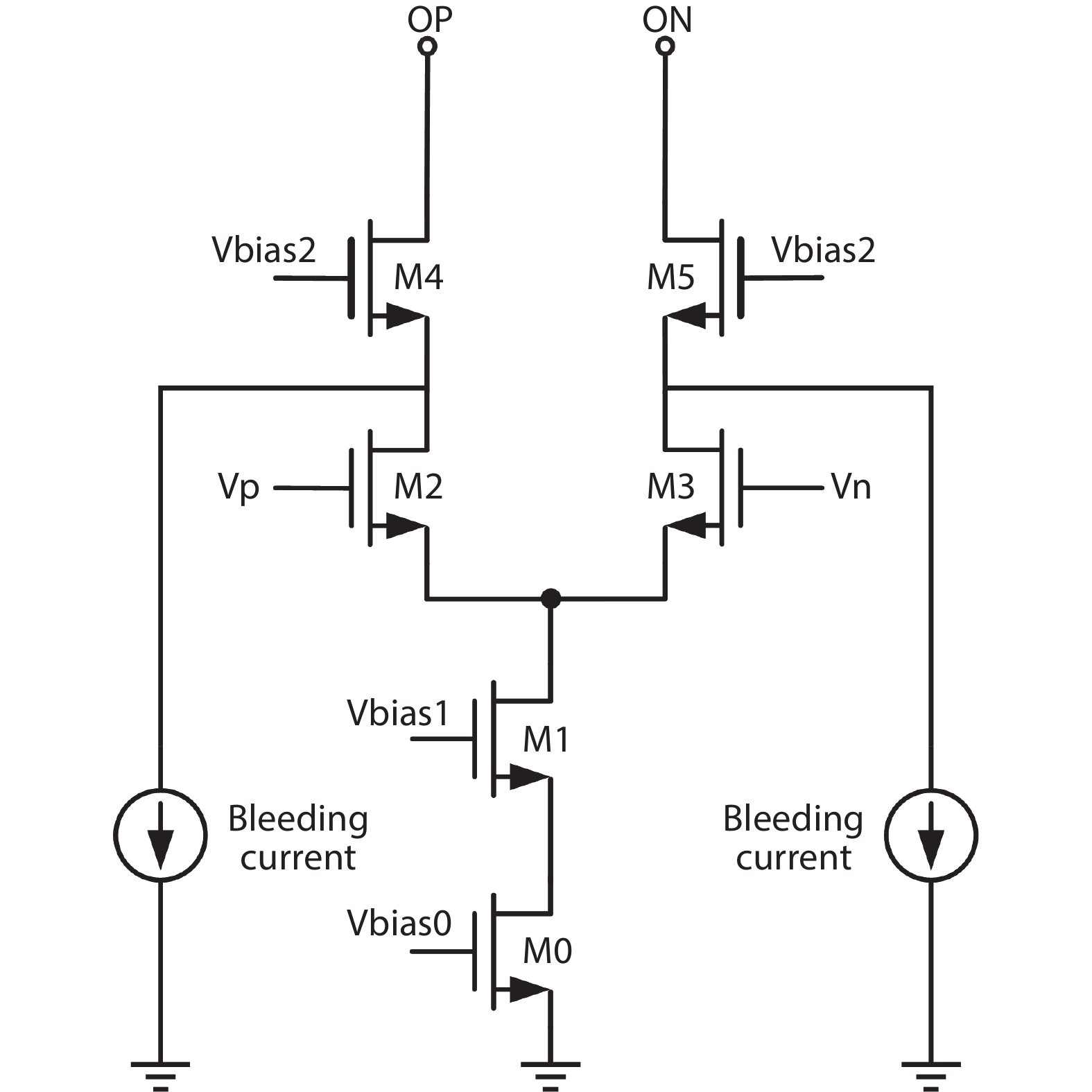

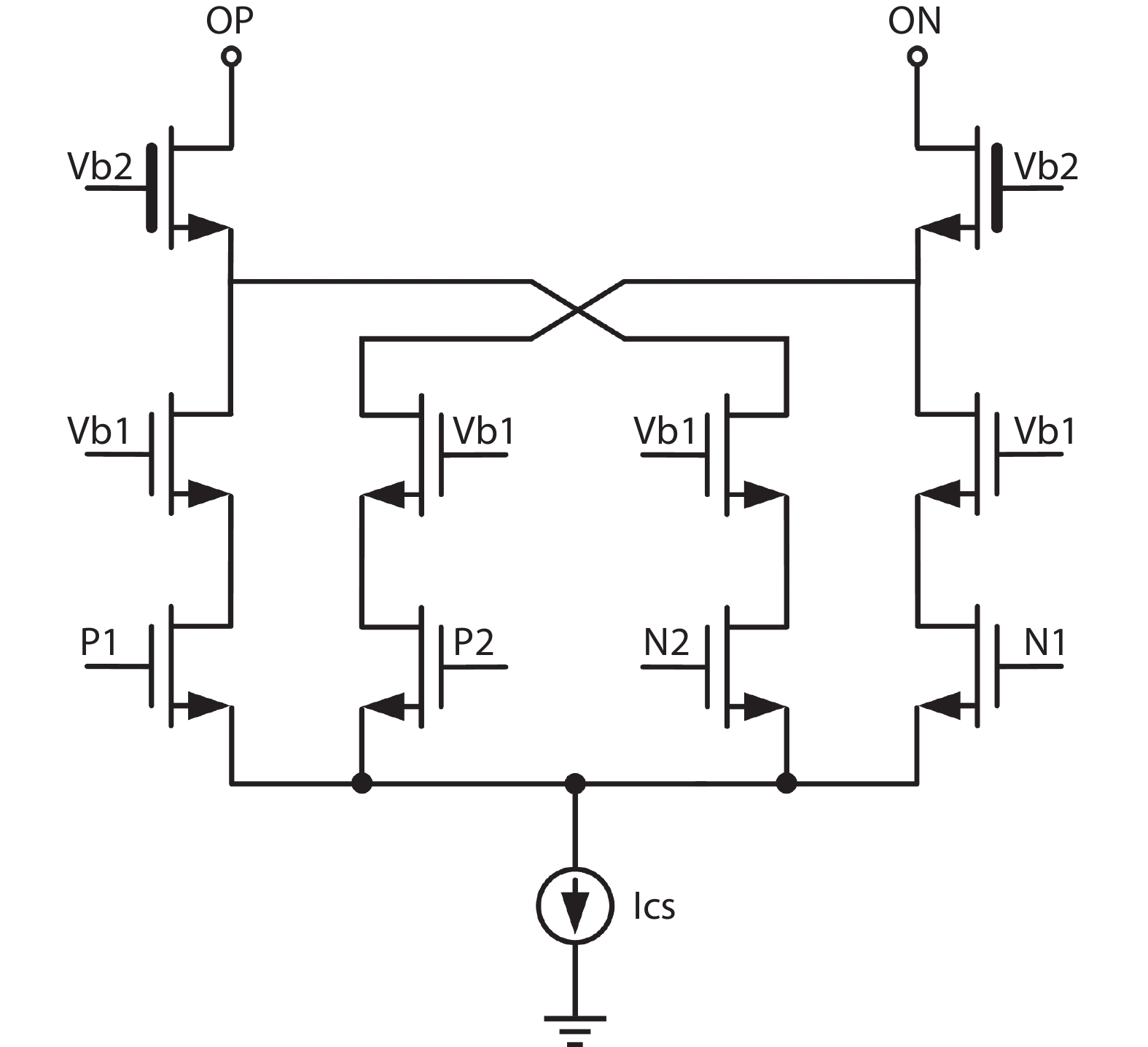

Digital to analog converters (DAC) play an important role as a bridge connecting the analog world and the digital world. With the rapid development of wireless communication, wideband digital radar, and other emerging technologies, better performing high-speed high-resolution DACs are required. In those applications, signal bandwidth and high-frequency linearity often limited by data converters are the bottleneck of the system. This article reviews the state-of-the-art technologies of high-speed and high-resolution DACs reported in recent years. Comparisons are made between different architectures, circuit implementations and calibration techniques along with the figure of merit (FoM) results. -

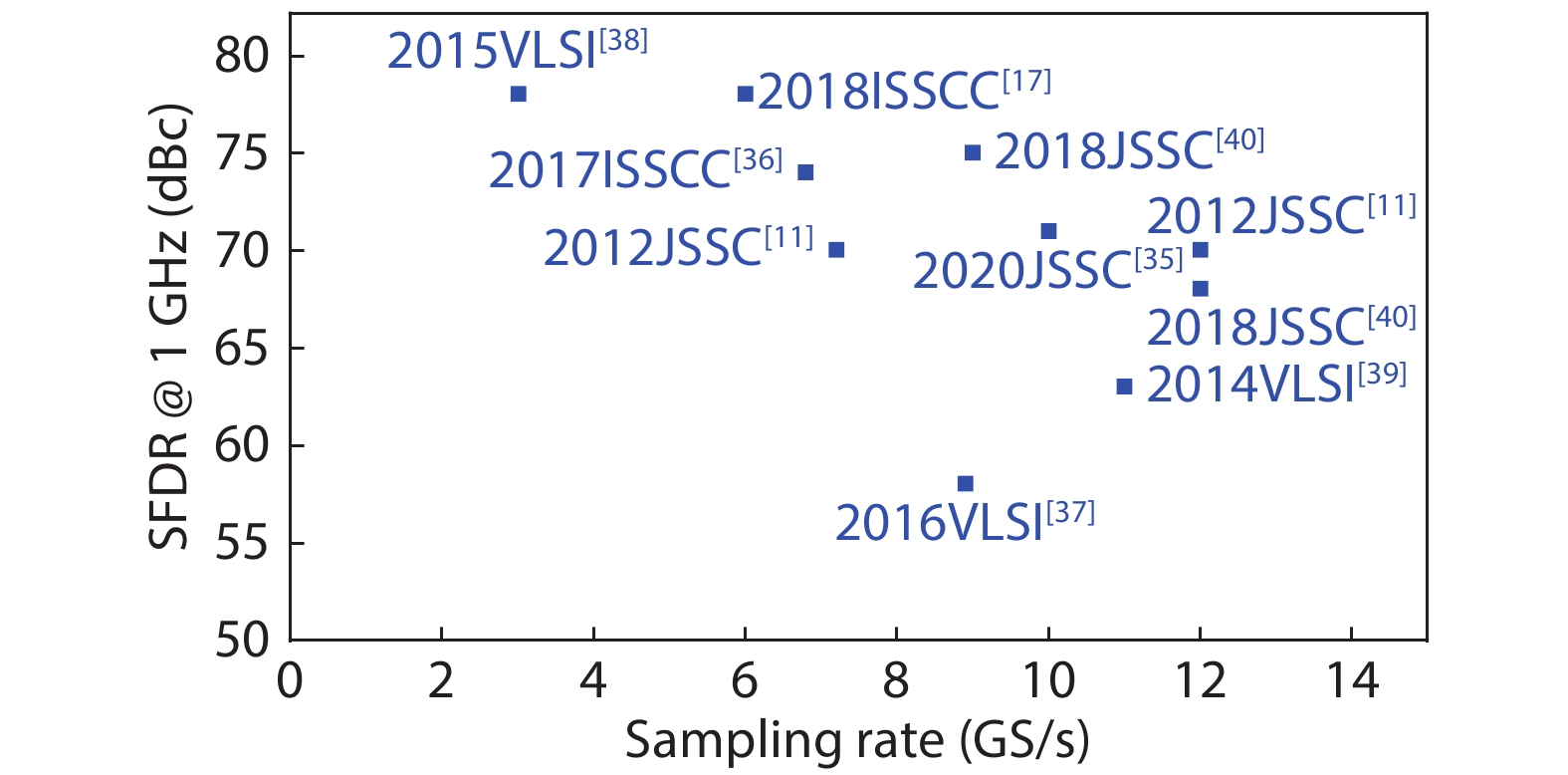

References

[1] Doris K, van Roermund A, Leenaerts D. Wide-bandwidth high-dynamic range D/A converters. Boston, MA: Springer, 2006[2] Spiridon S, Tang J, Yan H, et al. A 375 mW multimode DAC-based transmitter with 2.2 GHz signal bandwidth and in-band IM3 < –58 dBc in 40 nm CMOS. IEEE J Solid State Circuits, 2013, 48, 1595 doi: 10.1109/JSSC.2013.2253219[3] KrishneGowda K, Wimmer L, Javed A R, et al. Analysis of PSSS modulation for optimization of DAC bit resolution for 100 Gbps systems. 2018 15th International Symposium on Wireless Communication Systems (ISWCS), 2018, 1[4] Xiao J, Chen B, Kim T K, et al. A 13-bit 9GS/s RF DAC-based broadband transmitter in 28nm CMOS. IEEE Symposium on VLSI Circuits, 2013, 262[5] Ku P C, Shih K Y, Lu L H. A high-voltage DAC-based transmitter for coded signals in high frequency ultrasound imaging applications. IEEE Trans Circuits Syst I, 2018, 65, 2797 doi: 10.1109/TCSI.2018.2817634[6] Erdmann C, Verbruggen B, Vaz B, et al. A modular 16nm direct-RF TX/RX embedding 9GS/S DAC and 4.5GS/S ADC with 90dB isolation and sub-80PS channel alignment for monolithic integration in 5G base-station SoC. 2018 IEEE Symposium on VLSI Circuits, 2018, 219[7] Rivet F, Deval Y, Begueret J B, et al. A software-defined radio based on sampled analog signal processing dedicated to digital modulations. 2007 PhD Research in Microelectronics and Electronics Conference, 2007, 121[8] Roshan-Zamir A, Wang B, Telaprolu S, et al. A two-segment optical DAC 40 Gb/s PAM4 silicon microring resonator modulator transmitter in 65nm CMOS. IEEE Optical Interconnects Conference (OI), 2017, 5[9] Li W Z, Zhou L, Luo M, et al. 100Gb/s/λ optical fiber transmission based on high speed DAC in SiGe technology. 2018 Conference on Lasers and Electro-Optics Pacific Rim, 2018, 1[10] Ostrovskyy P, Schrape O, Helmric K T, et al. A radiation hardened 16 GS/s arbitrary waveform generator ic for a submillimeter wave chirp-transform spectrometer. 2018 IEEE Nordic Circuits and Systems Conference (NORCAS): NORCHIP and International Symposium of System-on-Chip (SoC), 2018, 1[11] Van de Sande F, Lugil N, Demarsin F, et al. A 7.2 GSa/s, 14 bit or 12 GSa/s, 12 bit signal generator on a chip in a 165 GHz fT BiCMOS process. IEEE J Solid-State Circuits, 2012, 47, 1003 doi: 10.1109/JSSC.2012.2185172[12] Aliakbari A, Yeganeh Y M, Safari S. Simulation of DAC-based truncated sine excitation pulse generator. 2015 2nd International Conference on Knowledge-Based Engineering and Innovation (KBEI), 2015, 689[13] Zhuang Y, Magstadt B, Chen T, et al. High-purity sine wave generation using nonlinear DAC with predistortion based on low-cost accurate DAC–ADC co-testing. IEEE Trans Instrum Meas, 2018, 67, 279 doi: 10.1109/TIM.2017.2769238[14] Hansen J S, Jue G. New approach to spectrum and emitter simulation: For the evaluation of radar and electronic warfare systems. 2013 International Conference on Radar, 2013, 532[15] Glascott-Jones A, Chantier N, Bore F, et al. Direct conversion to X band using a 4.5 GSps SiGe digital to analog converter. 2014 International Radar Conference, 2014, 1[16] Yao Y, Dai F, Jaeger R C, et al. A 12-bit cryogenic and radiation-tolerant digital-to-analog converter for aerospace extreme environment applications. IEEE Trans Ind Electron, 2008, 55, 2810 doi: 10.1109/TIE.2008.924174[17] Lin C H, Wong K L J, Kim T Y, et al. A 16b 6GS/S Nyquist DAC with IMD < –90dBc up to 1.9GHz in 16nm CMOS. 2018 IEEE International Solid-State Circuits Conference (ISSCC), 2018, 360[18] van den Bosch A, Borremans M A F, Steyaert M S J, et al. A 10-bit 1-GSample/s Nyquist current-steering CMOS D/A converter. IEEE J Solid-State Circuits, 2001, 36, 315 doi: 10.1109/4.910469[19] Kim B C, Cho M H, Kim Y G, et al. A 1 V 6-bit 2.4 GS/s Nyquist CMOS DAC for UWB systems. 2010 IEEE MTT-S International Microwave Symposium, 2010, 912[20] Chou F T, Chen C M, Chen Z Y, et al. A novel glitch reduction circuitry for binary-weighted DAC. 2014 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), 2014, 240[21] Lin C H, van der Goes F M L, Westra J R, et al. A 12 bit 2.9 GS/s DAC with IM3 < < –60 dBc beyond 1 GHz in 65 nm CMOS. IEEE J Solid-State Circuits, 2009, 44, 3285 doi: 10.1109/JSSC.2009.2032624[22] Gong Y H, Geiger R L. Switching sequence optimization for gradient error compensation in thermometer-decoded DAC arrays. IEEE Trans Circuits Syst II, 2000, 47, 585 doi: 10.1109/82.850417[23] Chen H, Liu L Y, Li D M, et al. A 12-bit current steering DAC with 2-dimensional gradient-error tolerant switching scheme. J Semicond, 2010, 31, 105006 doi: 10.1088/1674-4926/31/10/105006[24] Mercer D A. Low-power approaches to high-speed current-steering digital-to-analog converters in 0.18-μm CMOS. IEEE J Solid-State Circuits, 2007, 42, 1688 doi: 10.1109/JSSC.2007.900279[25] Chen H H, Lee J, Weiner J, et al. A 14-b 150 MS/s CMOS DAC with digital background calibration. 2006 Symposium on VLSI Circuits, 2006, 51[26] Clara M, Klatzer W, Seger B, et al. A 1.5V 200MS/s 13b 25mW DAC with randomized nested background calibration in 0.13μm CMOS. 2007 IEEE International Solid-State Circuits Conference, 2007, 250[27] Zhu H Y, Yang W H, Egan N, et al. Calibration technique tracking temperature for current-steering digital-to-analog converters. 2014 IEEE 57th International Midwest Symposium on Circuits and Systems (MWSCAS), 2014, 1[28] Zhu H Y, Yang W H, Engel G, et al. A two-parameter calibration technique tracking temperature variations for current source mismatch. IEEE Trans Circuits Syst II, 2017, 64, 387 doi: 10.1109/TCSII.2016.2572667[29] Xu S H, Lee J W. Calibration and correction of timing mismatch error in two-channel time-interleaved DACs. 2019 IEEE International Symposium on Circuits and Systems (ISCAS), 2019, 1[30] Lin W T, Huang H Y, Kuo T H. A 12-bit 40 nm DAC achieving SFDR > 70 dB at 1.6 GS/s and IMD –61dB at 2.8 GS/s with DEMDRZ technique. IEEE J Solid-State Circuits, 2014, 49, 708 doi: 10.1109/JSSC.2014.2301769[31] Boiocchi S. Self-calibration in high speed current steering CMOS D/A converters. Second International Conference on Advanced A-D and D-A Conversion Techniques and their Applications, 1994, 148[32] Bechthum E, Radulov G I, Briaire J, et al. A wideband RF mixing-DAC achieving IMD < –82 dBc up to 1.9 GHz. IEEE J Solid-State Circuits, 2016, 51, 1374 doi: 10.1109/JSSC.2016.2543703[33] Su S, Chen M S. A 12-Bit 2 GS/s dual-rate hybrid DAC with pulse-error predistortion and in-band noise cancellation achieving > 74 dBc SFDR and < –80 dBc IM3 up to 1 GHz in 65 nm CMOS. IEEE J Solid-State Circuits, 2016, 51, 2963 doi: 10.1109/JSSC.2016.2594026[34] Park S, Kim G, Park S C, et al. A digital-to-analog converter based on differential-quad switching. IEEE J Solid-State Circuits, 2002, 37, 1335 doi: 10.1109/JSSC.2002.803056[35] Huang H, Kuo T. A 0.07-mm2 162-mW DAC achieving > 65 dBc SFDR and < –70 dBc IM3 at 10 GS/s with output impedance compensation and concentric parallelogram routing. IEEE J Solid-State Circuits, 2020, 55, 2478 doi: 10.1109/JSSC.2020.2993672[36] Erdmann C, Cullen E, Brouard D, et al. A 330mW 14b 6.8GS/s dual-mode RF DAC in 16nm FinFET achieving –70.8dBc ACPR in a 20MHz channel at 5.2GHz. 2017 IEEE International Solid-State Circuits Conference (ISSCC), 2017, 280[37] Ravinuthula V, Bright W, Weaver M, et al. A 14-bit 8.9GS/s RF DAC in 40nm CMOS achieving >71dBc LTE ACPR at 2.9GHz. 2016 IEEE Symposium on VLSI Circuits (VLSI-Circuits), 2016, 1[38] Engel G, Clara M, Zhu H Y, et al. A 16-bit 10Gsps current steering RF DAC in 65nm CMOS achieving 65dBc ACLR multi-carrier performance at 4.5GHz Fout. 2015 Symposium on VLSI Circuits (VLSI Circuits), C166[39] Olieman E, Annema A, Nauta B. A 110mW, 0.04mm2, 11GS/s 9-bit interleaved DAC in 28nm FDSOI with >50dB SFDR across Nyquist. IEEE Symposium on VLSI Circuits, 2014, 1[40] Su S Y, Chen M S W. A 16-bit 12-GS/s single-/dual-rate DAC with a successive bandpass delta-sigma modulator achieving <–67-dBc IM3 within DC to 6-GHz tunable passbands. IEEE J Solid-State Circuits, 2018, 53, 3517 doi: 10.1109/JSSC.2018.2871143[41] Van den Bosch A, Steyaert M S J, Sansen W. Solving static and dynamic performance limitations for high-speed D/A converters. Analog Circuit Design: Scalable Analog Circuit Design, High-Speed D/A Converters, RF Power Amplifiers. Norwell, MA: Kluwer, 2002[42] Chen T, Geens P, van der Plas G, et al. A 14-bit 130-MHz CMOS current-steering DAC with adjustable INL. Proceedings of the 30th European Solid-State Circuits Conference, 2004, 167[43] Nazemi A, Hu K M, Catli B, et al. 3.4 A 36Gb/s PAM4 transmitter using an 8b 18GS/S DAC in 28nm CMOS. 2015 IEEE International Solid-State Circuits Conference (ISSCC), 2015, 1[44] Greshishchev Y M, Pollex D, Wang S C, et al. A 56GS/S 6b DAC in 65nm CMOS with 256×6b memory. 2011 IEEE International Solid-State Circuits Conference, 2011, 194[45] Carreira J P. A two-step flash ADC for digital CMOS technology. Second International Conference on Advanced A-D and D-A Conversion Techniques and their Applications, 1994, 48[46] Bramburger S, Pitonak P, Killat D. A unary coded current steering DAC with sequential stepping of the thermometer coded register in 1 and 2 LSB steps. 2018 41st International Convention on Information and Communication Technology, Electronics and Microelectronics (MIPRO), 2018, 0089[47] Lin C H, Bult K. A 10-b, 500-MSample/s CMOS DAC in 0.6 mm2. IEEE J Solid-State Circuits, 1998, 33, 1948 doi: 10.1109/4.735535[48] Lin Y H, Lee D H, Yang C C, et al. High-speed DACs with random multiple data-weighted averaging algorithm. Proceedings of the 2003 International Symposium on Circuits and Systems, 2003, 1[49] Su S Y, Tsai T I, Sharma P K, et al. A 12 bit 1 GS/s dual-rate hybrid DAC with an 8 GS/s unrolled pipeline delta–sigma modulator achieving > 75 dB SFDR over the nyquist band. IEEE J Solid-State Circuits, 2015, 50, 896 doi: 10.1109/JSSC.2014.2385752[50] Schafferer B, Adams R. A 3V CMOS 400mW 14b 1.4GS/s DAC for multi-carrier applications. 2004 IEEE International Solid-State Circuits Conference, 2004, 360[51] Bugeja A R, Song B S, Rakers P L, et al. A 14-b, 100-MS/s CMOS DAC designed for spectral performance. IEEE J Solid-State Circuits, 1999, 34, 1719 doi: 10.1109/4.808897[52] Choe M J, Baek K H, Teshome M. A 1.6-GS/s 12-bit return-to-zero GaAs RF DAC for multiple Nyquist operation. IEEE J Solid-State Circuits, 2005, 40, 2456 doi: 10.1109/JSSC.2005.856276[53] Duncan L, Dupaix B, McCue J J, et al. A 10-bit DC-20-GHz multiple-return-to-zero DAC with >48-dB SFDR. IEEE J Solid-State Circuits, 2017, 52, 3262 doi: 10.1109/JSSC.2017.2749441[54] Luo F, Yin Y, Liang S, et al. Current switch driver and current source designs for high-speed current-steering DAC. 2008 2nd International Conference on Anti-counterfeiting, Security and Identification, 2008, 364[55] Luo M, Yu M Y, Li G. An 11-bit high-speed current steering DAC. 2012 2nd International Conference on Consumer Electronics, Communications and Networks (CECNet), 2012, 1622[56] Spiridon S, Yan H, Eberhart H. A linearity improvement technique for overcoming signal-dependent induced switching time mismatch in DAC-Based transmitters. 2015 41st European Solid-State Circuits Conference (ESSCIRC), 2015, 347[57] Li X Q, Wei Q, Xu Z, et al. A 14 bit 500 MS/s CMOS DAC using complementary switched current sources and time-relaxed interleaving DRRZ. IEEE Trans Circuits Syst I, 2014, 61, 2337 doi: 10.1109/TCSI.2014.2332248[58] van Roermund A, Vertreg M, Leenaerts D, et al. A 12b 500MS/s DAC with >70dB SFDR up to 120MHz in 0.18μm CMOS. 2005 IEEE International Digest of Technical Papers. Solid-State Circuits Conference, 2005, 116[59] Wang D, Zhou L, Wu D Y, et al. An 8 GSps 14 bit RF DAC with IM3 < –62 dBc up to 3.6 GHz. IEEE Trans Circuits Syst II, 2019, 66, 768 doi: 10.1109/TCSII.2019.2909354[60] Huang Q T, Francese P A, Martelli C, et al. A 200MS/s 14b 97mW DAC in 0.18μm CMOS. 2004 IEEE International Solid-State Circuits Conference, 2004, 364[61] Jensen H T, Galton I. A low-complexity dynamic element matching DAC for direct digital synthesis. IEEE Trans Circuits Syst II, 1998, 45, 13 doi: 10.1109/82.659453[62] Lin W, T. Kuo T A compact dynamic-performance-improved current-steering DAC with random rotation-based binary-weighted selection. IEEE J Solid-State Circuits, 2012, 47, 444 doi: 10.1109/JSSC.2011.2168651[63] Wang P J, Sun N. A random DEM technique with minimal element transition rate for high-speed DACs. 2014 IEEE International Symposium on Circuits and Systems (ISCAS), 2014, 1155[64] Van Der Plas G A M, Vandenbussche J, Sansen W, et al. A 14-bit intrinsic accuracy Q2 random walk CMOS DAC. IEEE J Solid-State Circuits, 1999, 34, 1708 doi: 10.1109/4.808896[65] Tseng W H, Wu J T, Chu Y C. A CMOS 8-bit 1.6-GS/s DAC with digital random return-to-zero. IEEE Trans Circuits Syst II, 2011, 58, 1 doi: 10.1109/TCSII.2011.2158710[66] Tseng W H, Fan C W, Wu J T. A 12-Bit 1.25-GS/s DAC in 90 nm CMOS with > 70 dB SFDR up to 500 MHz. IEEE J Solid-State Circuits, 2011, 46, 2845 doi: 10.1109/JSSC.2011.2164302[67] Liu J N, Li X Q, Wei Q, et al. A 14-bit 1.0-GS/s dynamic element matching DAC with >80 dB SFDR up to the Nyquist. 2015 IEEE International Symposium on Circuits and Systems (ISCAS), 2015, 1026[68] Lai L Q, Li X Q, Fu Y S, et al. Demystifying and mitigating code-dependent switching distortions in current-steering DACs. IEEE Trans Circuits Syst I, 2019, 66, 68 doi: 10.1109/TCSI.2018.2866819 -

Proportional views

DownLoad:

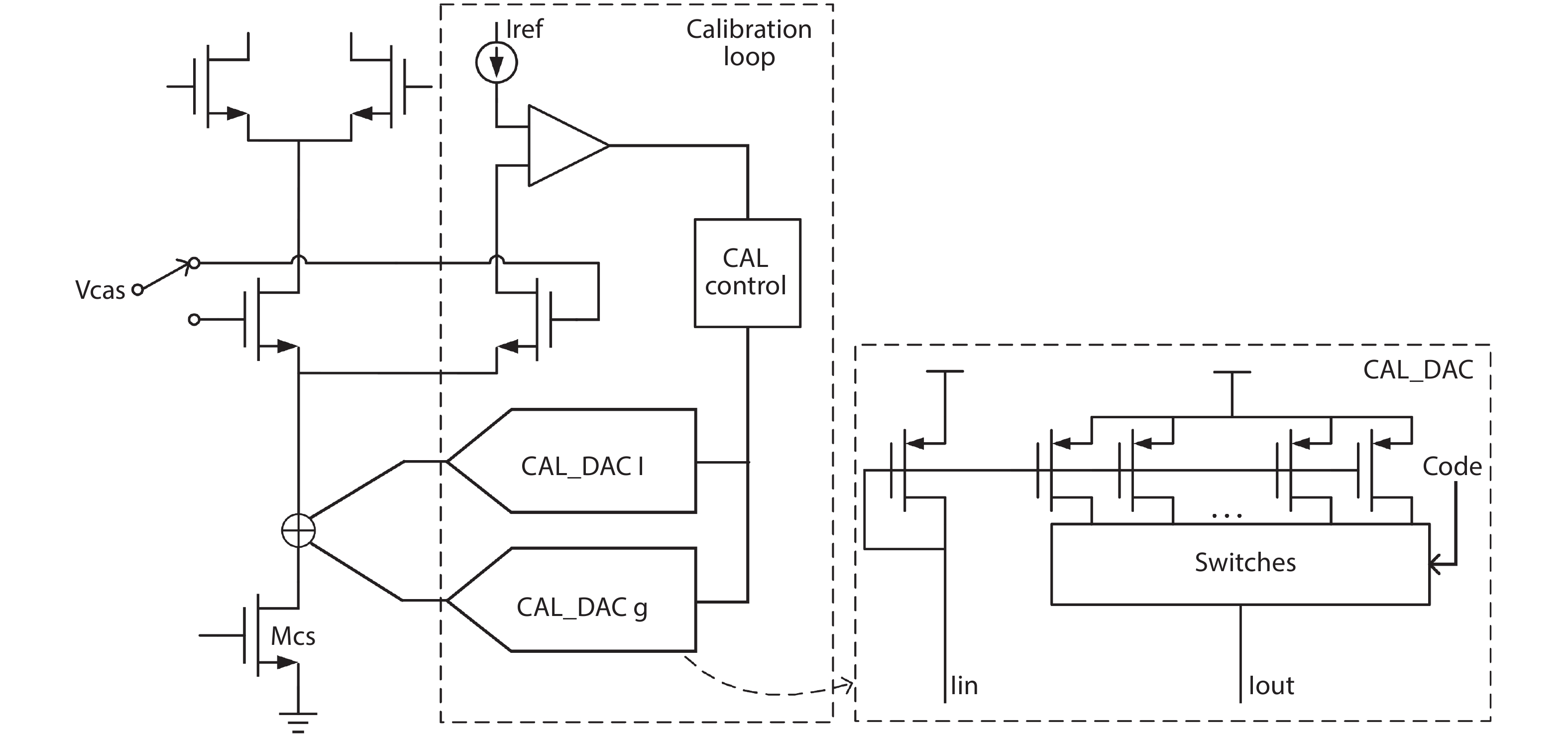

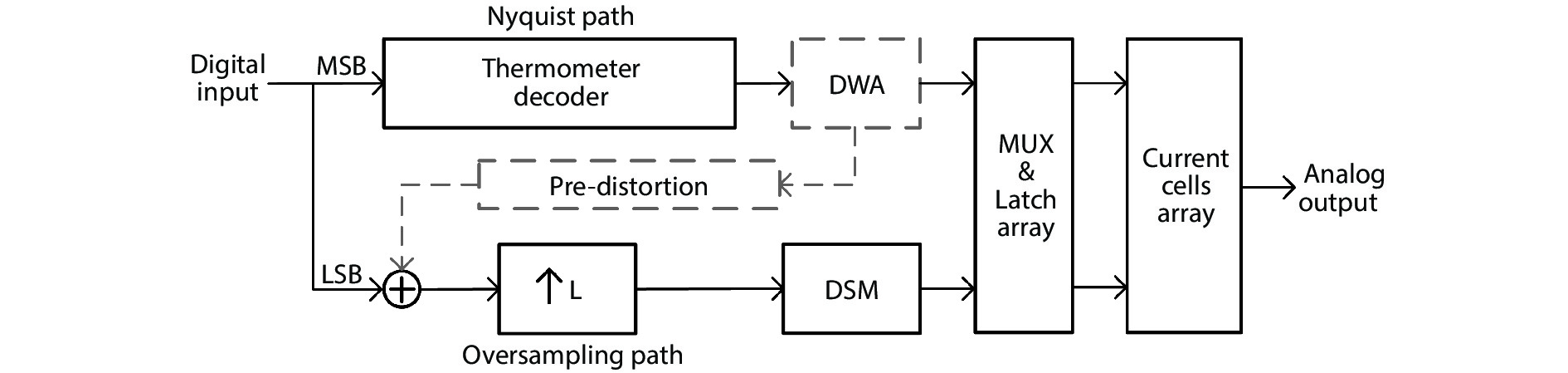

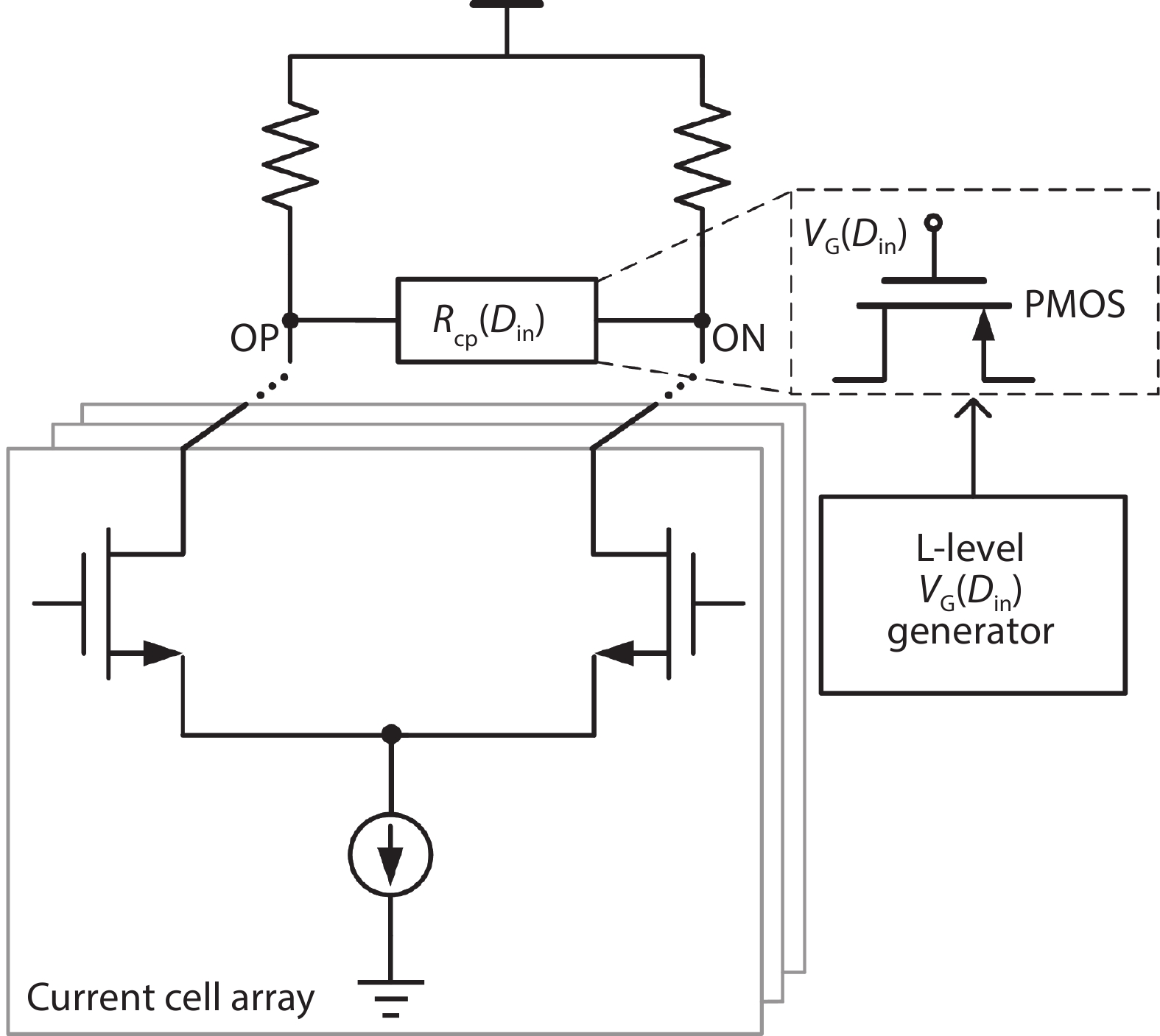

DownLoad: