| Citation: |

Zhaowu Tang, Chunsen Liu, Senfeng Zeng, Xiaohe Huang, Liwei Liu, Jiayi Li, Yugang Jiang, David Wei Zhang, Peng Zhou. Enhancement of refresh time in quasi-nonvolatile memory by the density of states engineering[J]. Journal of Semiconductors, 2021, 42(2): 024101. doi: 10.1088/1674-4926/42/2/024101

****

Z W Tang, C S Liu, S F Zeng, X H Huang, L W Liu, J Y Li, Y G Jiang, D W Zhang, P Zhou. Enhancement of refresh time in quasi-nonvolatile memory by the density of states engineering[J]. J. Semicond, 2021, 42(2): 024101. doi: 10.1088/1674-4926/42/2/024101

|

Enhancement of refresh time in quasi-nonvolatile memory by the density of states engineering

DOI: 10.1088/1674-4926/42/2/024101

More Information

-

Abstract

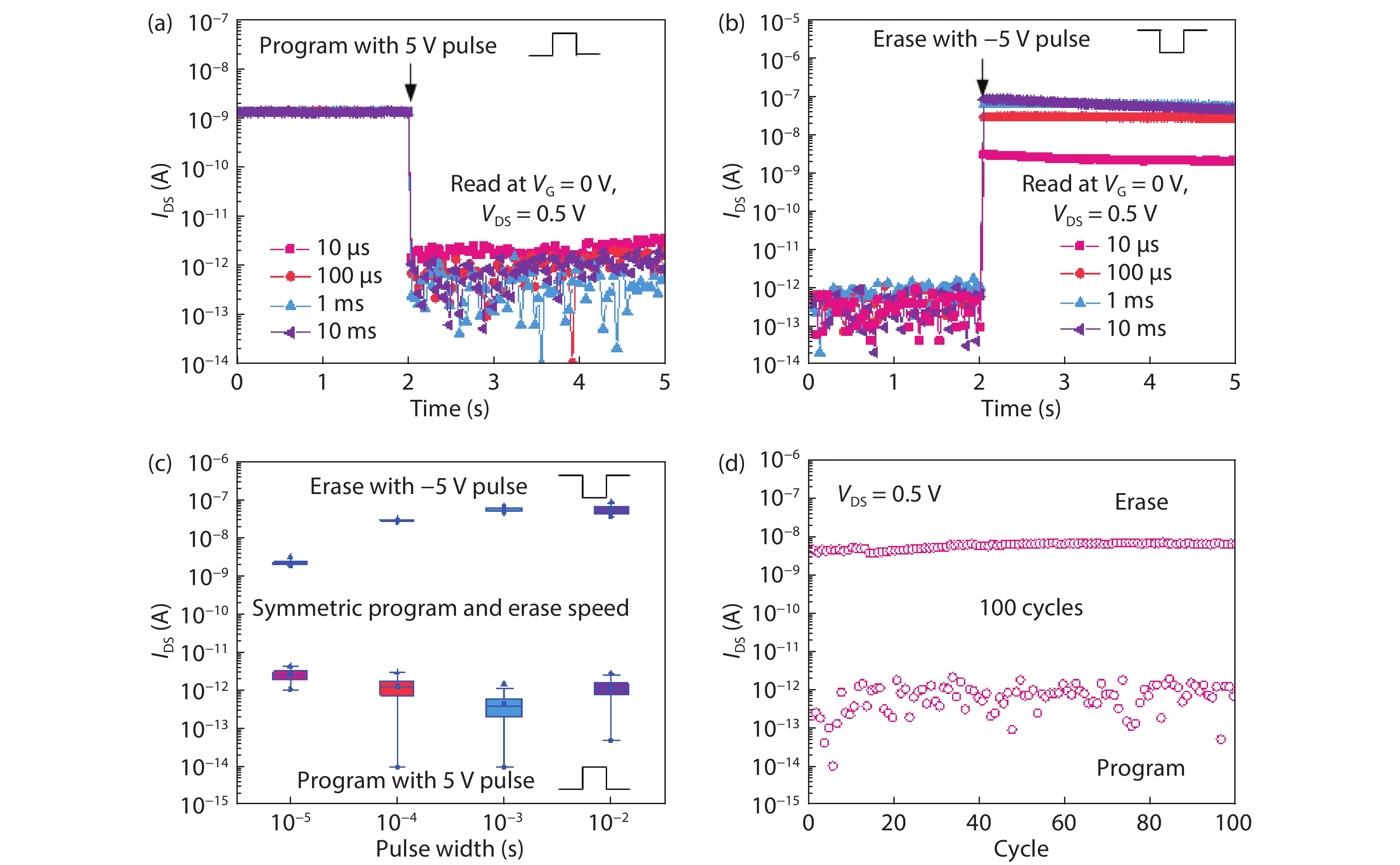

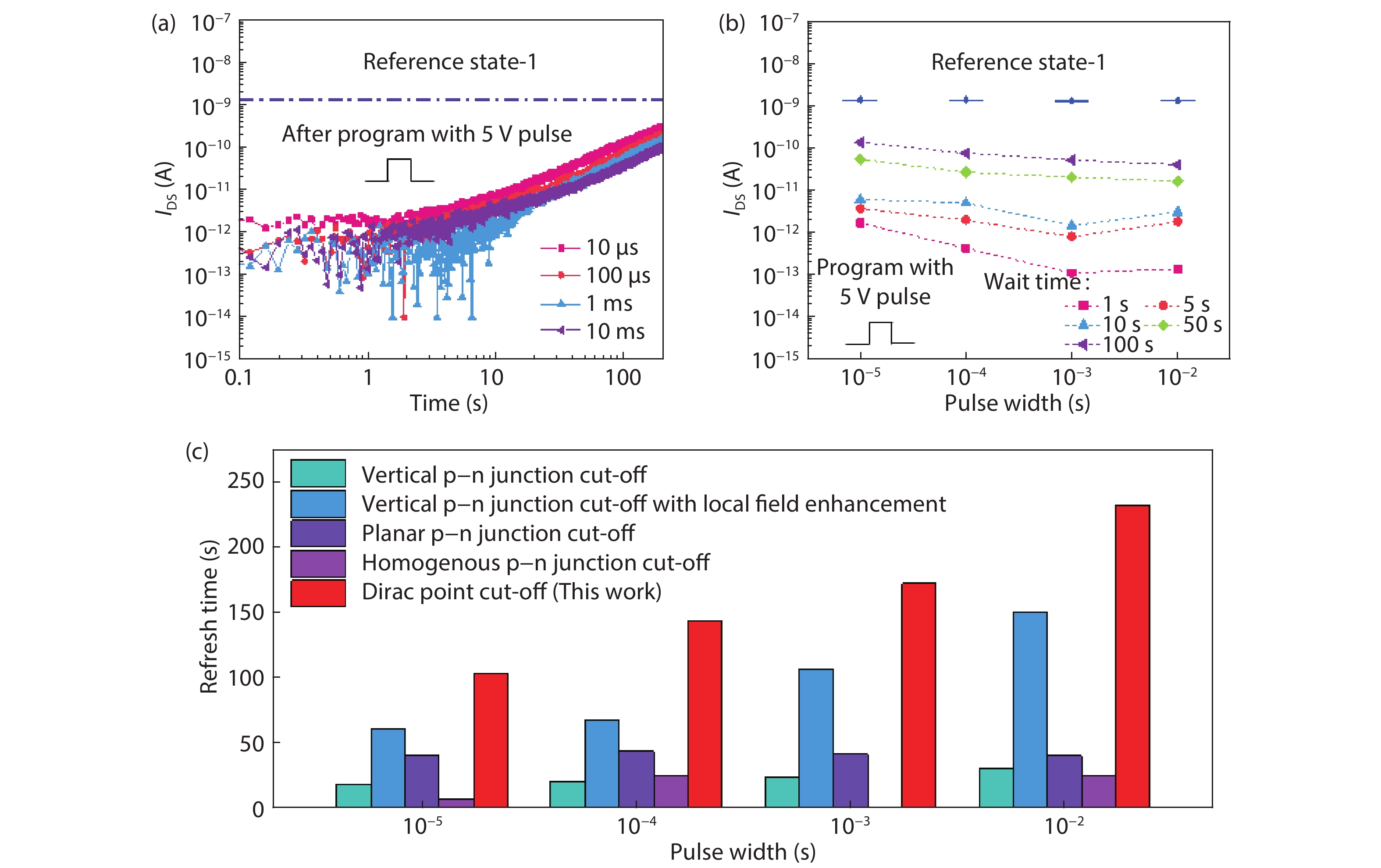

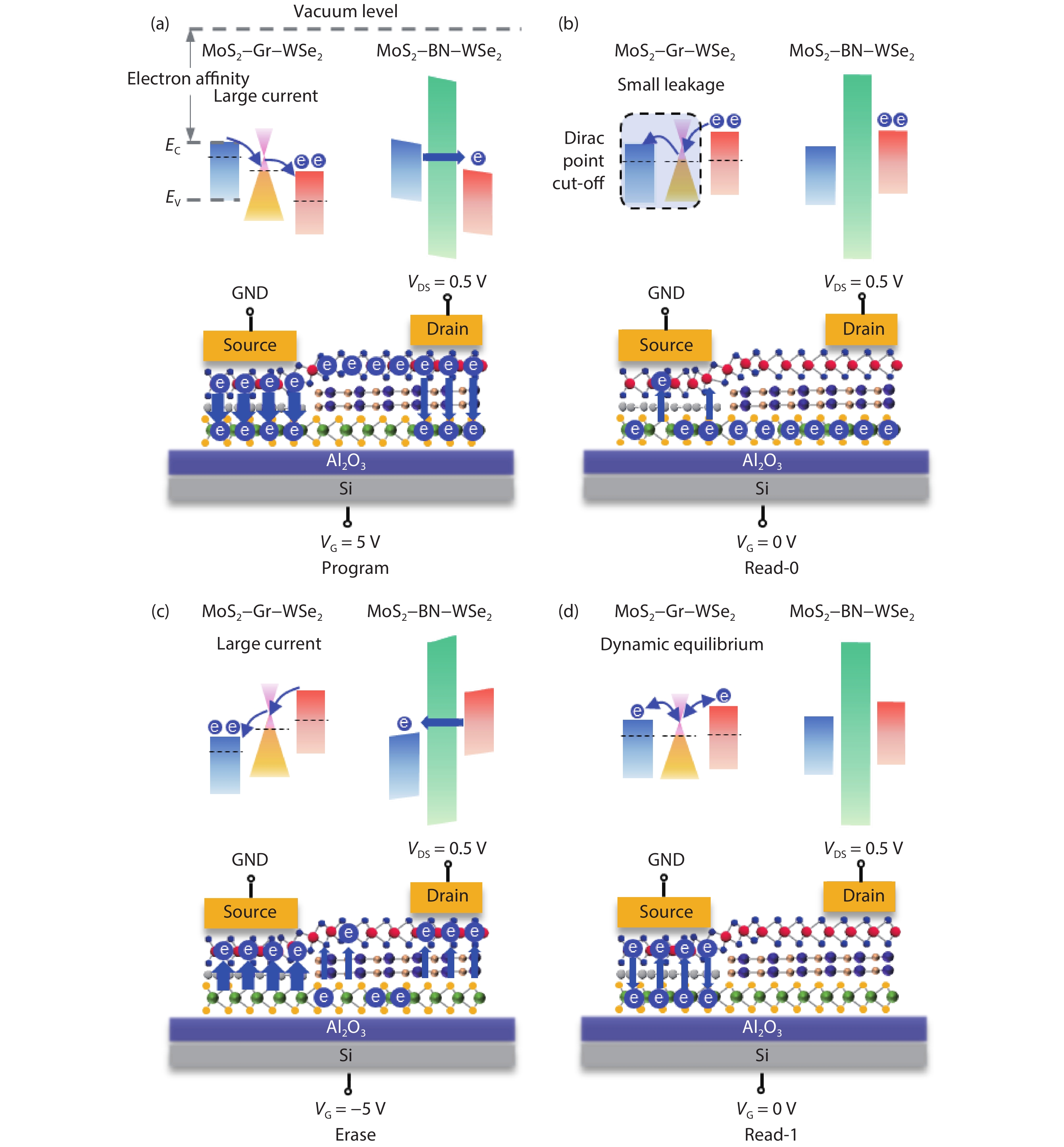

The recently reported quasi-nonvolatile memory based on semi-floating gate architecture has attracted extensive attention thanks to its potential to bridge the large gap between volatile and nonvolatile memory. However, the further extension of the refresh time in quasi-nonvolatile memory is limited by the charge leakage through the p–n junction. Here, based on the density of states engineered van der Waals heterostructures, the leakage of electrons from the floating gate to the channel is greatly suppressed. As a result, the refresh time is effectively extended to more than 100 s, which is the longest among all previously reported quasi-nonvolatile memories. This work provides a new idea to enhance the refresh time of quasi-nonvolatile memory by the density of states engineering and demonstrates great application potential for high-speed and low-power memory technology. -

References

[1] Liu C, Yan X, Song X, et al. A semi-floating gate memory based on van der Waals heterostructures for quasi-non-volatile applications. Nat Nanotechnol, 2018, 13(5), 404 doi: 10.1038/s41565-018-0102-6[2] Novoselov K S, Geim A K, Morozov S V, et al. Electric field effect in atomically thin carbon films. Science, 2004, 306(5696), 666 doi: 10.1126/science.1102896[3] Qiu C, Liu F, Xu L, et al. Dirac-source field-effect transistors as energy-efficient, high-performance electronic switches. Science, 2018, 361(6400), 387 doi: 10.1126/science.aap9195[4] Liu F, Qiu C, Zhang Z, et al. Dirac electrons at the source: breaking the 60-mV/decade switching limit. IEEE Trans Electron Devices, 2018, 65(7), 2736 doi: 10.1109/TED.2018.2836387[5] Liu F, Qiu C, Zhang Z, et al. First principles simulation of energy efficient switching by source density of states engineering. IEEE International Electron Devices Meeting (IEDM), 2018, 33[6] Lyu J, Pei J, Guo Y, et al. A new opportunity for 2D van der Waals heterostructures: making steep-slope transistors. Adv Mater, 2020, 32(2), 1906000 doi: 10.1002/adma.201906000[7] Yu W J, Chae S H, Lee S Y, et al. Ultra-transparent, flexible single-walled carbon nanotube non-volatile memory device with an oxygen-decorated graphene electrode. Adv Mater, 2011, 23(16), 1889 doi: 10.1002/adma.201004444[8] Lee S, Song E B, Kim S, et al. Impact of gate work-function on memory characteristics in Al2O3/HfOx/Al2O3/graphene charge-trap memory devices. Appl Phys Lett, 2012, 100(2), 023109 doi: 10.1063/1.3675633[9] Kim S M, Song E B, Lee S, et al. Transparent and flexible graphene charge-trap memory. ACS Nano, 2012, 6(9), 7879 doi: 10.1021/nn302193q[10] Bertolazzi S, Krasnozhon D, Kis A. Nonvolatile memory cells based on MoS2/graphene heterostructures. ACS Nano, 2013, 7(4), 3246 doi: 10.1021/nn3059136[11] Choi M S, Lee G H, Yu Y J, et al. Controlled charge trapping by molybdenum disulphide and graphene in ultrathin heterostructured memory devices. Nat Commun, 2013, 4(1), 1624 doi: 10.1038/ncomms2652[12] Zhang E, Wang W, Zhang C, et al. Tunable charge-trap memory based on few-layer MoS2. ACS Nano, 2015, 9(1), 612 doi: 10.1021/nn5059419[13] Vu Q A, Shin Y S, Kim Y R, et al. Two-terminal floating-gate memory with van der Waals heterostructures for ultrahigh on/off ratio. Nat Commun, 2016, 7(1), 12725 doi: 10.1038/ncomms12725[14] He G, Ramamoorthy H, Kwan C P, et al. Thermally assisted nonvolatile memory in monolayer MoS2 transistors. Nano Lett, 2016, 16(10), 6445 doi: 10.1021/acs.nanolett.6b02905[15] Lee Y T, Kwon H, Kim J S, et al. Nonvolatile ferroelectric memory circuit using black phosphorus nanosheet-based field-effect transistors with P(VDF-TrFE) polymer. ACS Nano, 2015, 9(10), 10394 doi: 10.1021/acsnano.5b04592[16] Hou X, Zhang H, Liu C, et al. Charge-trap memory based on hybrid 0D quantum dot-2D WSe2 structure. Small, 2018, 14(20), 1800319 doi: 10.1002/smll.201800319[17] Mishra A, Janardanan A, Khare M, et al. Reduced multilayer graphene oxide floating gate flash memory with large memory window and robust retention characteristics. IEEE Electron Device Lett, 2013, 34(9), 1136 doi: 10.1109/LED.2013.2272643[18] Ding Y, Liu L, Li J, et al. A semi-floating memory with 535% enhancement of refresh time by local field modulation. Adv Funct Mater, 2020, 30(15), 1908089 doi: 10.1002/adfm.201908089[19] Li J, Liu L, Chen X, et al. Symmetric ultrafast writing and erasing speeds in quasi-nonvolatile memory via van der Waals heterostructures. Adv Mater, 2019, 31(11), 1808035 doi: 10.1002/adma.201808035[20] Wu G, Tian B, Liu L, et al. Programmable transition metal dichalcogenide homojunctions controlled by nonvolatile ferroelectric domains. Nat Electron, 2020, 3(1), 43 doi: 10.1038/s41928-019-0350-y[21] Liu C, Zhou P. Memory Devices Based on Van der Waals Heterostructures. ACS Mater Lett, 2020, 2(9), 1101 doi: 10.1021/acsmaterialslett.0c00227[22] Liu J, Huang Z, Lai F, et al. Controllable growth of the graphene from millimeter-sized monolayer to multilayer on Cu by chemical vapor deposition. Nanoscale Res Lett, 2015, 10(1), 455 doi: 10.1186/s11671-015-1164-0[23] Dai G P, Wu M H, Taylor D K, et al. Hybrid 3D graphene and aligned carbon nanofiber array architectures. RSC Adv, 2012, 2(24), 8965 doi: 10.1039/c2ra21084c[24] Cao Y, Wang Z, Bian Q, et al. Phonon modes and photonic excitation transitions of MoS2 induced by top-deposited graphene revealed by Raman spectroscopy and photoluminescence. Appl Phys Lett, 2019, 114(13), 133103 doi: 10.1063/1.5083104[25] Mouri S, Miyauchi Y, Matsuda K. Tunable photoluminescence of monolayer MoS2 via chemical doping. Nano Lett, 2013, 13(12), 5944 doi: 10.1021/nl403036h[26] Ahn G H, Amani M, Rasool H, et al. Strain-engineered growth of two-dimensional materials. Nat Commun, 2017, 8(1), 608 doi: 10.1038/s41467-017-00516-5 -

Supplements

21010012suppl.pdf

21010012suppl.pdf

-

Proportional views

DownLoad:

DownLoad: