| Citation: |

Feilong Ding, Baokang Peng, Xi Li, Lining Zhang, Runsheng Wang, Zhitang Song, Ru Huang. A review of compact modeling for phase change memory[J]. Journal of Semiconductors, 2022, 43(2): 023101. doi: 10.1088/1674-4926/43/2/023101

****

F L Ding, B K Peng, X Li, L N Zhang, R S Wang, Z T Song, R Huang, A review of compact modeling for phase change memory[J]. J. Semicond., 2022, 43(2): 023101. doi: 10.1088/1674-4926/43/2/023101.

|

A review of compact modeling for phase change memory

DOI: 10.1088/1674-4926/43/2/023101

More Information

-

Abstract

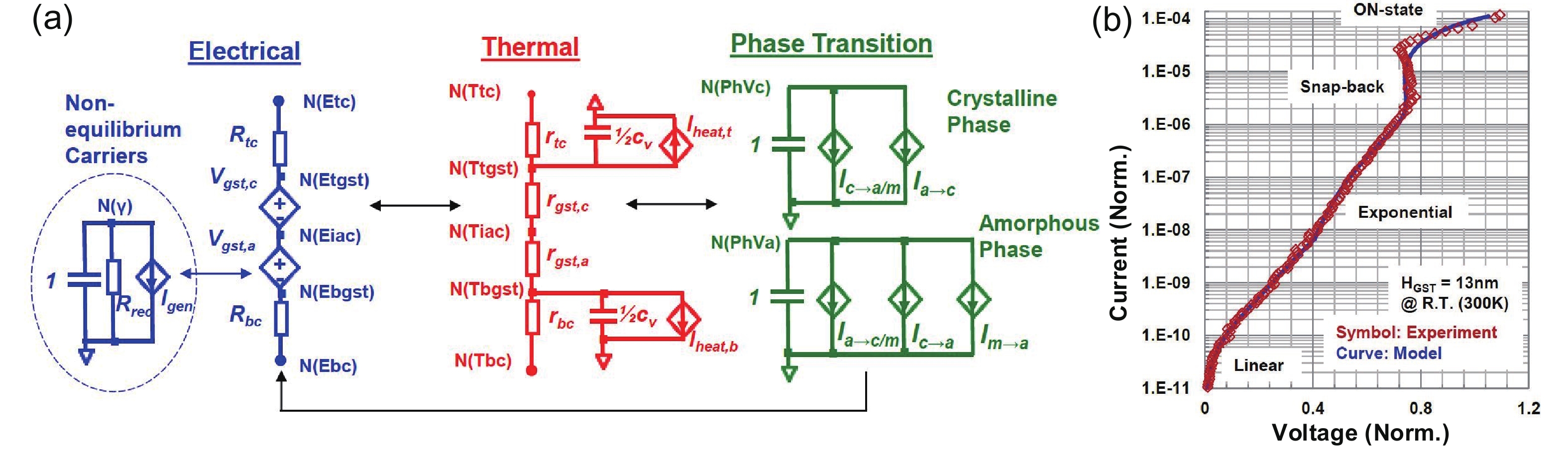

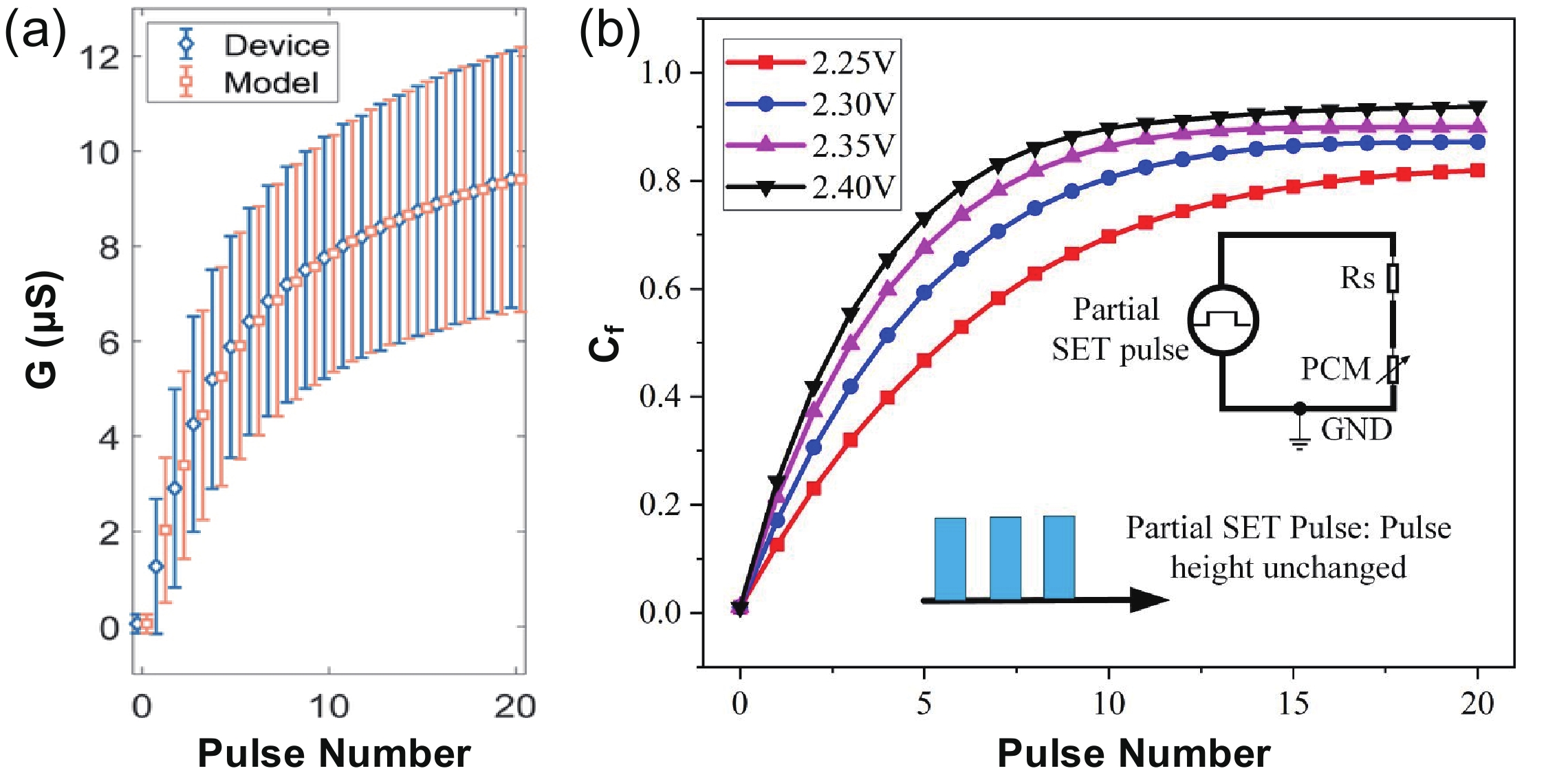

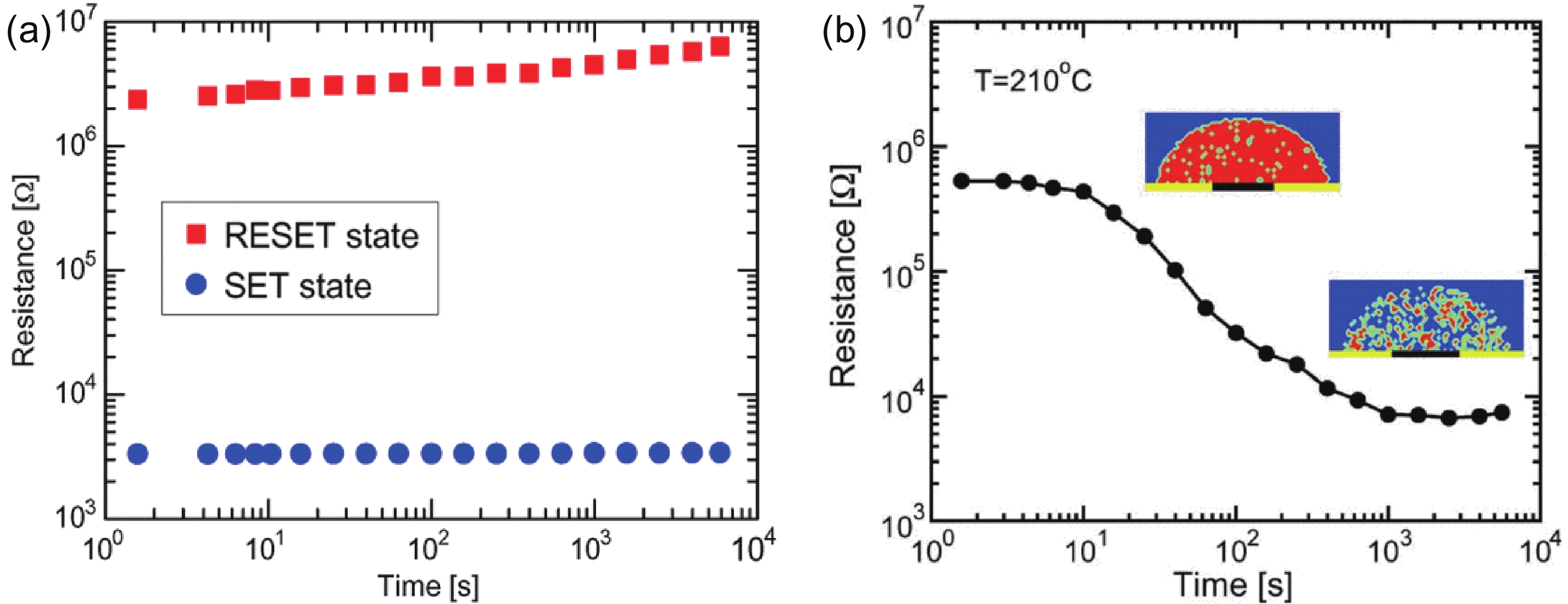

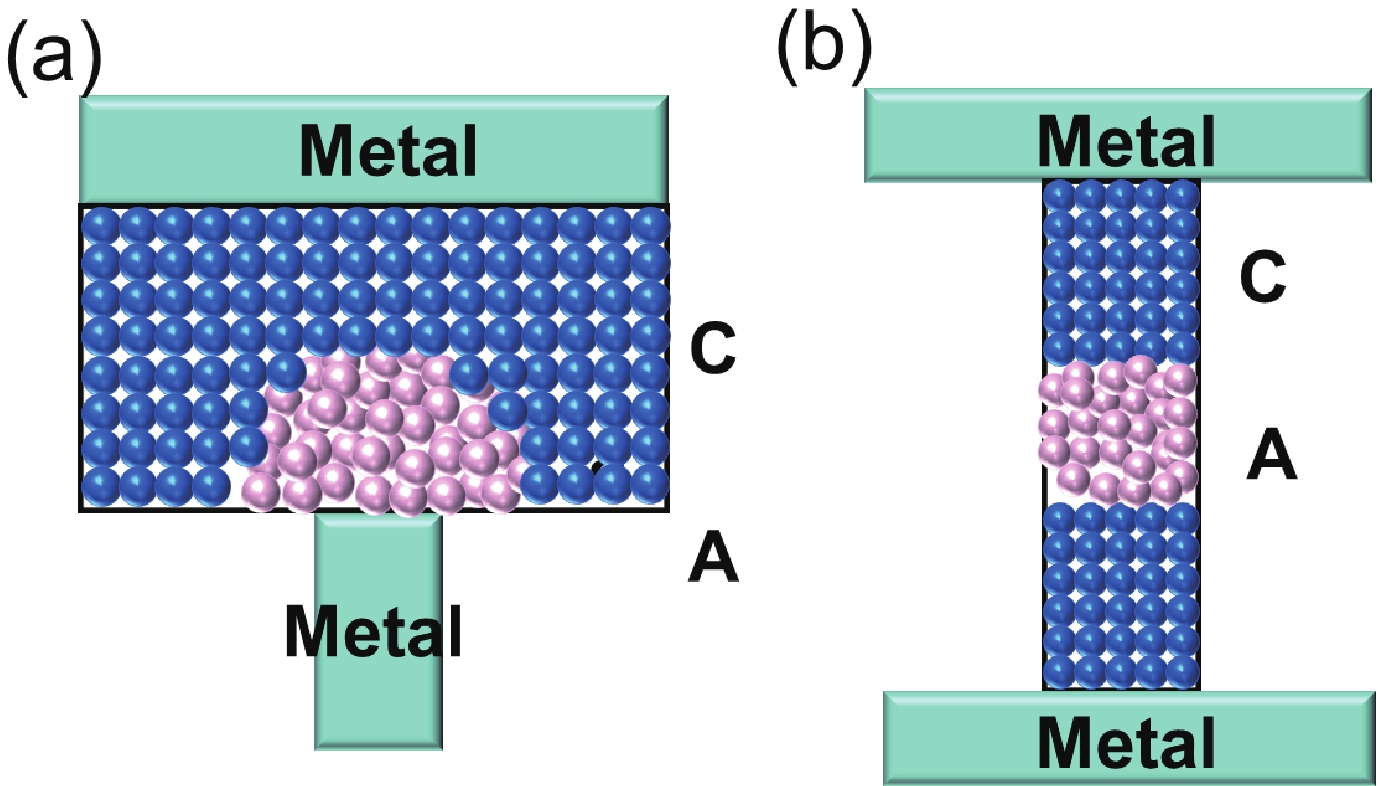

Phase change memory (PCM) attracts wide attention for the memory-centric computing and neuromorphic computing. For circuit and system designs, PCM compact models are mandatory and their status are reviewed in this work. Macro models and physics-based models have been proposed in different stages of the PCM technology developments. Compact modeling of PCM is indeed more complex than the transistor modeling due to their multi-physics nature including electrical, thermal and phase transition dynamics as well as their interactions. Realizations of the PCM operations including threshold switching, set and reset programming in these models are diverse, which also differs from the perspective of circuit simulations. For the purpose of efficient and reliable designs of the PCM technology, open issues and challenges of the compact modeling are also discussed.-

Keywords:

- phase change memory,

- compact model,

- macro model,

- physics-based model

-

References

[1] Kim T, Lee S. Evolution of phase-change memory for the storage-class memory and beyond. IEEE Trans Electron Devices, 2020, 67, 1394 doi: 10.1109/TED.2020.2964640[2] Le Gallo M, Sebastian A. An overview of phase-change memory device physics. J Phys D, 2020, 53, 213002 doi: 10.1088/1361-6463/ab7794[3] Gong N B. Multi level cell (MLC) in 3D crosspoint phase change memory array. Sci China Inf Sci, 2021, 64, 1 doi: 10.1007/s11432-021-3184-5[4] Lee S H. Technology scaling challenges and opportunities of memory devices. 2016 IEEE International Electron Devices Meeting (IEDM), 2016, 1.1.1 doi: 10.1109/IEDM.2016.7838026[5] Kau D, Tang S, Karpov I V, et al. A stackable cross point phase change memory. 2009 IEEE International Electron Devices Meeting, 2009, 1 doi: 10.1109/IEDM.2009.5424263[6] [7] Arnaud F, Zuliani P, Reynard J P, et al. Truly innovative 28nm FDSOI technology for automotive micro-controller applications embedding 16MB phase change memory. 2018 IEEE International Electron Devices Meeting (IEDM), 2018, 18.4.1 doi: 10.1109/IEDM.2018.8614595[8] Cappelletti P, Annunziata R, Arnaud F, et al. Phase change memory for automotive grade embedded NVM applications. J Phys D, 2020, 53, 193002 doi: 10.1088/1361-6463/ab71aa[9] [10] Neale R G, Nelson D L, Moore G E. Nonvolatile and reprogramable, read-mostly memory is here. Electronics, 1970, 43, 56[11] Tyson S, Wicker G, Lowrey T, et al. Nonvolatile, high density, high performance phase-change memory. 2000 IEEE Aerospace Conference, 2000, 385 doi: 10.1109/AERO.2000.878512[12] Lai S, Lowrey T. OUM – A 180 nm nonvolatile memory cell element technology for stand alone and embedded applications. International Electron Devices Meeting, 2001, 36.5.1 doi: 10.1109/IEDM.2001.979636[13] Oh J H, Park J H, Lim Y S, et al. Full integration of highly manufacturable 512Mb PRAM based on 90nm technology. 2006 International Electron Devices Meeting, 2006, 1 doi: 10.1109/IEDM.2006.346905[14] Annunziata R, Zuliani P, Borghi M, et al. Phase change memory technology for embedded non volatile memory applications for 90nm and beyond. 2009 IEEE International Electron Devices Meeting, 2009, 1 doi: 10.1109/IEDM.2009.5424413[15] Im D H, Lee J I, Cho S L, et al. A unified 7.5nm dash-type confined cell for high performance PRAM device. 2008 IEEE International Electron Devices Meeting, 2008, 1 doi: 10.1109/IEDM.2008.4796654[16] Kim T, Choi H, Kim M, et al. High-performance, cost-effective 2z nm two-deck cross-point memory integrated by self-align scheme for 128 Gb SCM. 2018 IEEE International Electron Devices Meeting, 2018, 37.1.1 doi: 10.1109/IEDM.2018.8614680[17] Chien W C, Ho Y H, Cheng H Y, et al. A novel self-converging write scheme for 2-bits/cell phase change memory for storage class memory (SCM) application. 2015 Symposium on VLSI Technology, 2015, T100 doi: 10.1109/VLSIT.2015.7223709[18] Gong N, Idé T, Kim S, et al. Signal and noise extraction from analog memory elements for neuromorphic computing. Nat Commun, 2018, 9, 2102 doi: 10.1038/s41467-018-04485-1[19] Kim S, Ishii M, Lewis S, et al. NVM neuromorphic core with 64k-cell (256-by-256) phase change memory synaptic array with on-chip neuron circuits for continuous in situ learning. 2015 IEEE International Electron Devices Meeting, 2015, 17.1.1 doi: 10.1109/IEDM.2015.7409716[20] Bedeschi F, Fackenthal R, Resta C, et al. A bipolar-selected phase change memory featuring multi-level cell storage. IEEE J Solid State Circuits, 2009, 44, 217 doi: 10.1109/JSSC.2008.2006439[21] Suri M N, Bichler O, Querlioz D, et al. Phase change memory as synapse for ultra-dense neuromorphic systems: Application to complex visual pattern extraction. 2011 International Electron Devices Meeting, 2011, 4.4.1 doi: 10.1109/IEDM.2011.6131488[22] Suri M N, Bichler O, Querlioz D, et al. Physical aspects of low power synapses based on phase change memory devices. J Appl Phys, 2012, 112, 054904 doi: 10.1063/1.4749411[23] Tuma T, Pantazi A, Le Gallo M, et al. Stochastic phase-change neurons. Nat Nanotechnol, 2016, 11, 693 doi: 10.1038/nnano.2016.70[24] Wright C D, Hosseini P, Diosdado J A V. Beyond von-Neumann computing with nanoscale phase-change memory devices. Adv Funct Mater, 2013, 23, 2248 doi: 10.1002/adfm.201202383[25] Wang Q, Niu G, Ren W, et al. Phase change random access memory for neuro-inspired computing. Adv Electron Mater, 2021, 7, 2001241 doi: 10.1002/aelm.202001241[26] Pavan P, Larcher L, Marmiroli A. Floating gate devices: Operation and compact modeling. IEEE Circuits and Devices Magazine, 2004, 120 doi: 10.1109/MCD.2006.1708380[27] Xu Z H, Sutaria K B, Yang C G, et al. Hierarchical modeling of Phase Change memory for reliable design. 2012 IEEE 30th International Conference on Computer Design, 2012, 115 doi: 10.1109/ICCD.2012.6378626[28] Sebastian A, Le Gallo M, Burr G W, et al. Tutorial: Brain-inspired computing using phase-change memory devices. J Appl Phys, 2018, 124, 111101 doi: 10.1063/1.5042413[29] Wong H S P, Raoux S, Kim S, et al. Phase change memory. Proc IEEE, 2010, 98, 2201 doi: 10.1109/JPROC.2010.2070050[30] Raoux S, Wełnic W, Ielmini D. Phase change materials and their application to nonvolatile memories. Chem Rev, 2010, 110, 240 doi: 10.1021/cr900040x[31] Zhang W, Mazzarello R, Wuttig M, et al. Designing crystallization in phase-change materials for universal memory and neuro-inspired computing. Nat Rev Mater, 2019, 4, 150 doi: 10.1038/s41578-018-0076-x[32] Zhang W, Mazzarello R, Ma E. Phase-change materials in electronics and photonics. MRS Bull, 2019, 44, 686 doi: 10.1557/mrs.2019.201[33] Eaton D L. Electrical conduction anomaly of semiconducting glasses in the system As-Te-I. J Am Ceram Soc, 1964, 47, 554 doi: 10.1111/j.1151-2916.1964.tb13816.x[34] Pirovano A, Lacaita A L, Benvenuti A, et al. Electronic switching in phase-change memories. IEEE Trans Electron Devices, 2004, 51, 452 doi: 10.1109/TED.2003.823243[35] Ielmini D. Threshold switching mechanism by high-field energy gain in the hopping transport of chalcogenide glasses. Phys Rev B, 2008, 78, 035308 doi: 10.1103/PhysRevB.78.035308[36] Peng C B, Cheng L, Mansuripur M. Experimental and theoretical investigations of laser-induced crystallization and amorphization in phase-change optical recording media. J Appl Phys, 1997, 82, 4183 doi: 10.1063/1.366220[37] Lacaita A L, Ielmini D, Mantegazza D. Status and challenges of phase change memory modeling. Solid State Electron, 2008, 52, 1443 doi: 10.1016/j.sse.2008.04.020[38] Li Z J, Jeyasingh R G D, Lee J, et al. Electrothermal modeling and design strategies for multibit phase-change memory. IEEE Trans Electron Devices, 2012, 59, 3561 doi: 10.1109/TED.2012.2219311[39] Redaelli A, Pirovano A, Benvenuti A, et al. Threshold switching and phase transition numerical models for phase change memory simulations. J Appl Phys, 2008, 103, 111101 doi: 10.1063/1.2931951[40] Schmithusen B, Tikhomirov P, Lyumkis E. Phase-change memory simulations using an analytical phase space model. 2008 International Conference on Simulation of Semiconductor Processes and Devices, 2008, 57 doi: 10.1109/SISPAD.2008.4648236[41] Weinberg M C, Birnie D P III, Shneidman V A III. Crystallization kinetics and the JMAK equation. J Non Cryst Solids, 1997, 219, 89 doi: 10.1016/S0022-3093(97)00261-5[42] Johnson W A, Mehl R F. Reaction kinetics in processes of nucleation and growth. Trans Amn Instit Mining Metall Eng, 1939, 135, 416[43] Senkader S, Wright C D. Models for phase-change of Ge2Sb2Te5 in optical and electrical memory devices. J Appl Phys, 2003, 95, 504 doi: 10.1063/1.1633984[44] Chen Z Q, Tong H, Cai W, et al. Modeling and simulations of the integrated device of phase change memory and ovonic threshold switch selector with a confined structure. IEEE Trans Electron Devices, 2021, 68, 1616 doi: 10.1109/TED.2021.3059436[45] Cobley R A, Wright C D. Parameterized SPICE model for a phase-change RAM device. IEEE Trans Electron Devices, 2006, 53, 112 doi: 10.1109/TED.2005.860642[46] Wei X Q, Shi L P, Walia R, et al. HSPICE macromodel of PCRAM for binary and multilevel storage. IEEE Trans Electron Devices, 2006, 53, 56 doi: 10.1109/TED.2005.860645[47] Cobley R A, Wright C D, Vázquez Diosdado J A. A model for multilevel phase-change memories incorporating resistance drift effects. IEEE J Electron Devices Soc, 2015, 3, 15 doi: 10.1109/JEDS.2014.2357577[48] Cobley R A, Hayat H, Wright C D. A self-resetting spiking phase-change neuron. Nanotechnology, 2018, 29, 195202 doi: 10.1088/1361-6528/aab177[49] Kwong K C, Li L, He J, et al. Verilog-A model for phase change memory simulation. 2008 9th International Conference on Solid-State and Integrated-Circuit Technology, 2008, 492 doi: 10.1109/ICSICT.2008.4734588[50] Fantini P, Benvenuti A, Pirovano A, et al. A compact model for Phase Change Memories. 2006 International Conference on Simulation of Semiconductor Processes and Devices, 2006, 162 doi: 10.1109/SISPAD.2006.282863[51] Ventrice D, Fantini P, Redaelli A, et al. A phase change memory compact model for multilevel applications. IEEE Electron Device Lett, 2007, 28, 973 doi: 10.1109/LED.2007.907288[52] Sonoda K, Sakai A, Moniwa M, et al. A compact model of phase-change memory based on rate equations of crystallization and amorphization. IEEE Trans Electron Devices, 2008, 55, 1672 doi: 10.1109/TED.2008.923740[53] Pigot C, Bocquet M, Gilibert F, et al. Comprehensive phase-change memory compact model for circuit simulation. IEEE Trans Electron Devices, 2018, 65, 4282 doi: 10.1109/TED.2018.2862155[54] Xu N, Wang J, Deng Y X, et al. Multi-domain compact modeling for GeSbTe-based memory and selector devices and simulation for large-scale 3-D cross-point memory arrays. 2016 IEEE International Electron Devices Meeting, 2016, 7.7.1 doi: 10.1109/IEDM.2016.7838371[55] Calderoni A, Ferro M, Ventrice D, et al. Physical modeling and control of switching statistics in PCM arrays. 2011 3rd IEEE Int Mem Work IMW, 2011, 1 doi: 10.1109/IMW.2011.5873230[56] Yoo S, Lee H D, Lee S, et al. Electro-thermal model for thermal disturbance in cross-point phase-change memory. IEEE Trans Electron Devices, 2020, 67, 1454 doi: 10.1109/TED.2019.2960444[57] Ielmini D, Mantegazza D, Lacaita A L. Voltage-controlled relaxation oscillations in phase-change memory devices. IEEE Electron Device Lett, 2008, 29, 568 doi: 10.1109/LED.2008.921957[58] Nardone M, Karpov V G, Karpov I V. Relaxation oscillations in chalcogenide phase change memory. J Appl Phys, 2010, 107, 054519 doi: 10.1063/1.3329387[59] Nardone M, Karpov V G, Jackson D C S, et al. A unified model of nucleation switching. Appl Phys Lett, 2009, 94, 103509 doi: 10.1063/1.3100779[60] Hu H F, Liu D Y, Chen X H, et al. A compact phase change memory model with dynamic state variables. IEEE Trans Electron Devices, 2020, 67, 133 doi: 10.1109/TED.2019.2956193[61] Schmidt P E, Callarotti R C. Theoretical and experimental study of the operation of ovonic switches in the relaxation oscillation mode. I. The charging characteristic during the off state. J Appl Phys, 1984, 55, 3144 doi: 10.1063/1.333314[62] Anbarasu M, Wimmer M, Bruns G, et al. Nanosecond threshold switching of GeTe6 cells and their potential as selector devices. Appl Phys Lett, 2012, 100, 143505 doi: 10.1063/1.3700743[63] Burr G W, Shenoy R S, Virwani K, et al. Access devices for 3D crosspoint memory. J Vac Sci Technol B, 2014, 32, 040802 doi: 10.1116/1.4889999[64] Lee M J, Lee D, Kim H, et al. Highly-scalable threshold switching select device based on chaclogenide glasses for 3D nanoscaled memory arrays. 2012 International Electron Devices Meeting, 2012, 2.6.1 doi: 10.1109/IEDM.2012.6478966[65] Ren K, Duan X, Xiong Q Q, et al. Constructing reliable PCM and OTS devices with an interfacial carbon layer. J Mater Sci: Mater Electron, 2019, 30, 20037 doi: 10.1007/s10854-019-02373-y[66] Chen X H, Ding F L, Huang X Q, et al. A robust and efficient compact model for phase-change memory circuit simulations. IEEE Trans Electron Devices, 2021, 68, 4404 doi: 10.1109/TED.2021.3098656[67] Nandakumar S R, Le Gallo M, Boybat I, et al. A phase-change memory model for neuromorphic computing. J Appl Phys, 2018, 124, 152135 doi: 10.1063/1.5042408[68] Chen X H, Hu H F, Huang X Q, et al. A SPICE model of phase change memory for neuromorphic circuits. IEEE Access, 2020, 8, 95278 doi: 10.1109/ACCESS.2020.2995907[69] Le Gallo M, Tuma T, Zipoli F, et al. Inherent stochasticity in phase-change memory devices. 2016 46th European Solid-State Device Research Conference, 2016, 373 doi: 10.1109/ESSDERC.2016.7599664[70] Boybat I, Le Gallo M, Nandakumar S R, et al. Neuromorphic computing with multi-memristive synapses. Nat Commun, 2018, 9, 2514 doi: 10.1038/s41467-018-04933-y[71] Boniardi M, Ielmini D. Physical origin of the resistance drift exponent in amorphous phase change materials. Appl Phys Lett, 2011, 98, 243506 doi: 10.1063/1.3599559[72] Boniardi M, Ielmini D, Lavizzari S, et al. Statistics of resistance drift due to structural relaxation in phase-change memory arrays. IEEE Trans Electron Devices, 2010, 57, 2690 doi: 10.1109/TED.2010.2058771[73] Russo U, Ielmini D, Redaelli A, et al. Intrinsic data retention in nanoscaled phase-change memories—part I: Monte Carlo model for crystallization and percolation. IEEE Trans Electron Devices, 2006, 53, 3032 doi: 10.1109/TED.2006.885527[74] Kim K, Ahn S J. Reliability investigations for manufacturable high density PRAM. 2005 IEEE International Reliability Physics Symposium, 2005, 157 doi: 10.1109/RELPHY.2005.1493077[75] Gleixner B, Pellizzer F, Bez R. Reliability characterization of phase change memory. 2009 10th Annual Non-Volatile Memory Technology Symposium, 2009, 7 doi: 10.1109/NVMT.2009.5429783[76] Yang T Y, Cho J Y, Park Y J, et al. Effects of dopings on the electric-field-induced atomic migration and void formation in Ge2Sb2Te5. 18th IEEE International Symposium on the Physical and Failure Analysis of Integrated Circuits, 2011, 1 doi: 10.1109/IPFA.2011.5992717[77] Pirovano A, Lacaita A L, Benvenuti A, et al. Scaling analysis of phase-change memory technology. 2003 IEEE International Electron Devices Meeting, 2003, 29.6.1 doi: 10.1109/IEDM.2003.1269376[78] Pirovano A, Lacaita A L, Pellizzer F, et al. Low-field amorphous state resistance and threshold voltage drift in chalcogenide materials. IEEE Trans Electron Devices, 2004, 51, 714 doi: 10.1109/TED.2004.825805[79] Koelmans W W, Sebastian A, Jonnalagadda V P, et al. Projected phase-change memory devices. Nat Commun, 2015, 6, 1 doi: 10.1038/ncomms9181[80] Giannopoulos I, Sebastian A, Le Gallo M, et al. 8-bit precision in-memory multiplication with projected phase-change memory. 2018 IEEE International Electron Devices Meeting, 2018, 27.7.1 doi: 10.1109/IEDM.2018.8614558[81] Redaelli A, Ielmini D, Russo U, et al. Intrinsic data retention in nanoscaled phase-change memories—part II: Statistical analysis and prediction of failure time. IEEE Trans Electron Devices, 2006, 53, 3040 doi: 10.1109/TED.2006.885525 -

Proportional views

DownLoad:

DownLoad: