| Citation: |

Quan Pan, Xiongshi Luo, Zhenghao Li, Zhengzhe Jia, Fuzhan Chen, Xuewei Ding, C. Patrick Yue. A 26-Gb/s CMOS optical receiver with a reference-less CDR in 65-nm CMOS[J]. Journal of Semiconductors, 2022, 43(7): 072401. doi: 10.1088/1674-4926/43/7/072401

****

Q Pan, X S Luo, Z H Li, Z Z Jia, F Z Chen, X W Ding, C P Yue. A 26-Gb/s CMOS optical receiver with a reference-less CDR in 65-nm CMOS[J]. J. Semicond, 2022, 43(7): 072401. doi: 10.1088/1674-4926/43/7/072401

|

A 26-Gb/s CMOS optical receiver with a reference-less CDR in 65-nm CMOS

DOI: 10.1088/1674-4926/43/7/072401

More Information

-

Abstract

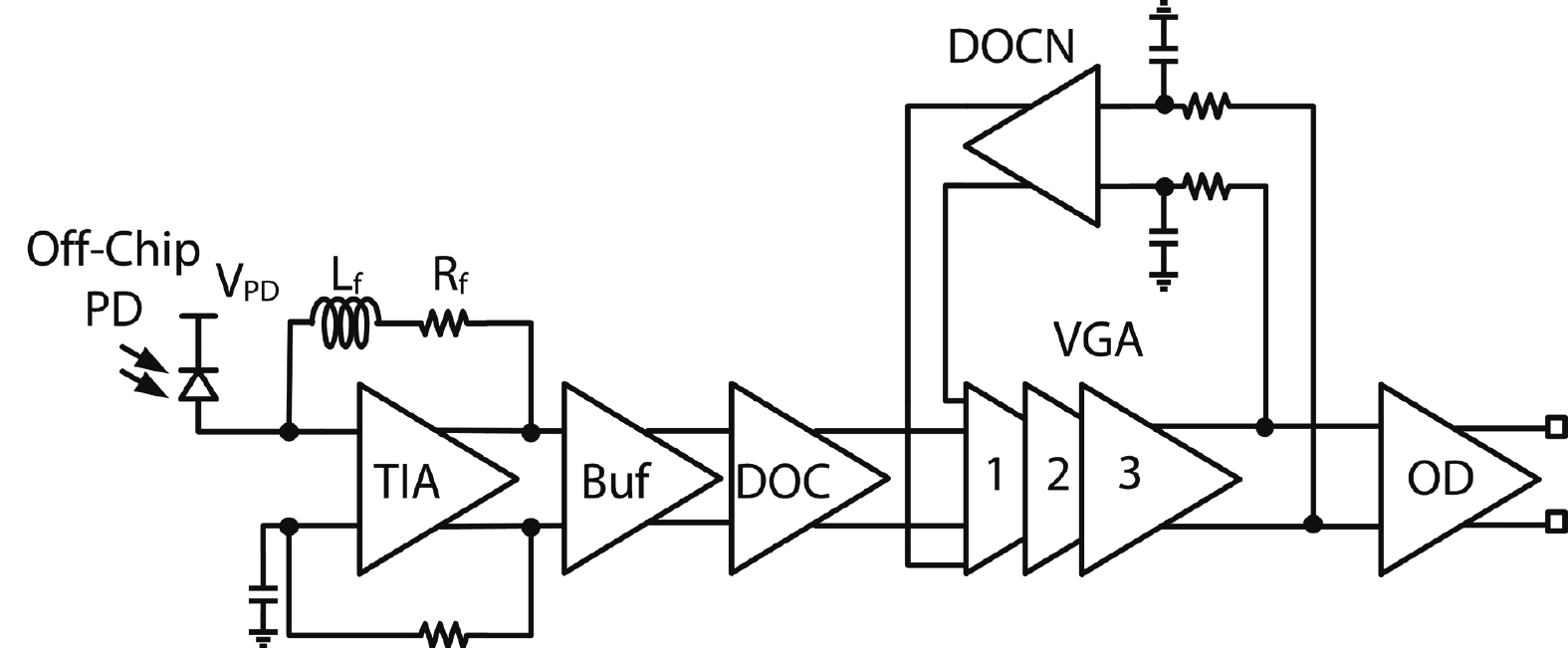

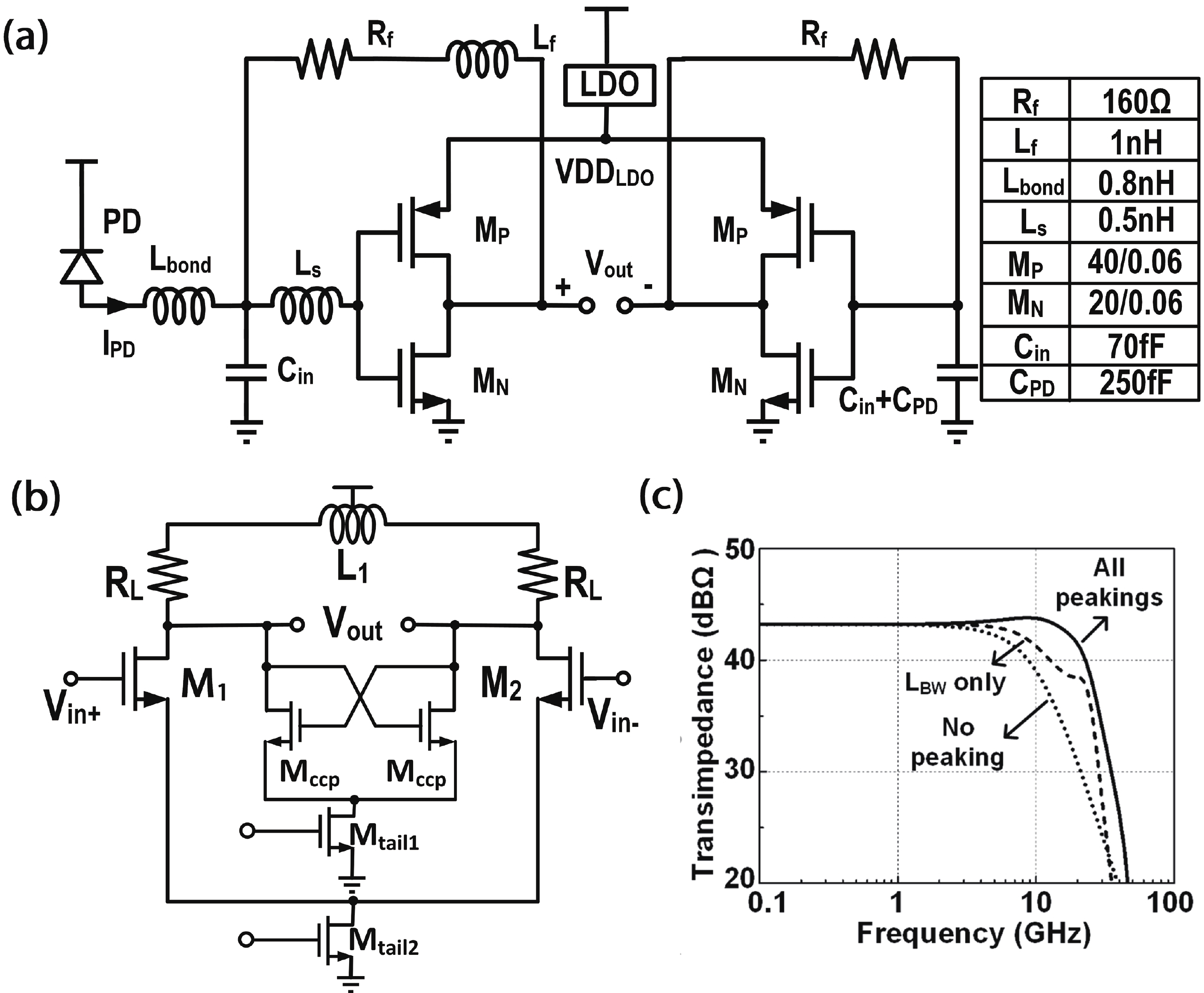

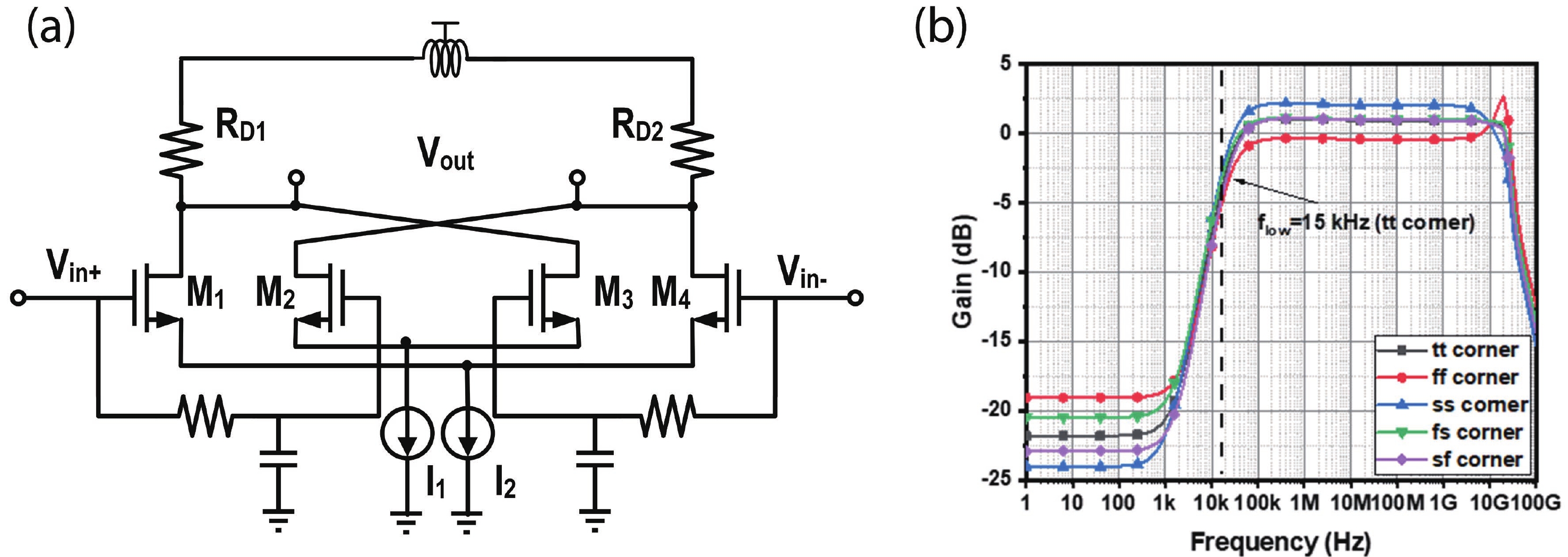

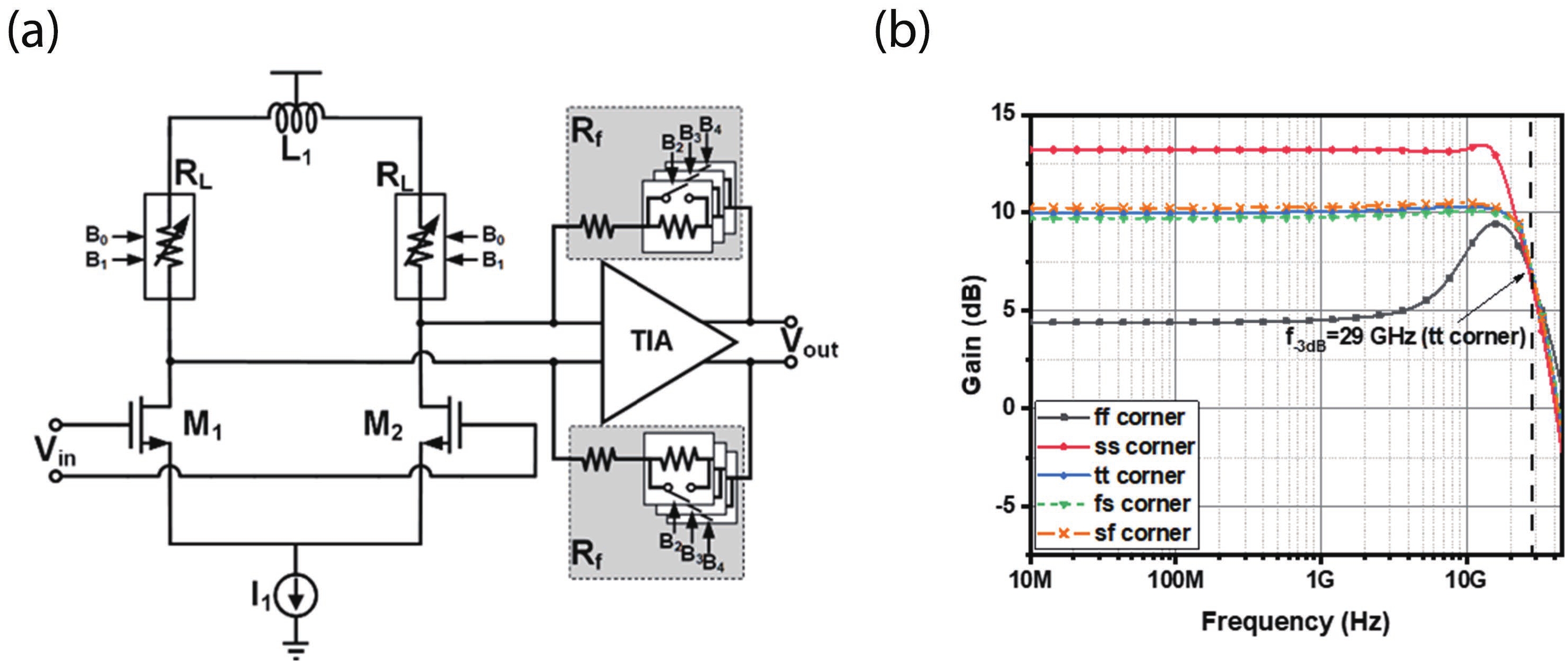

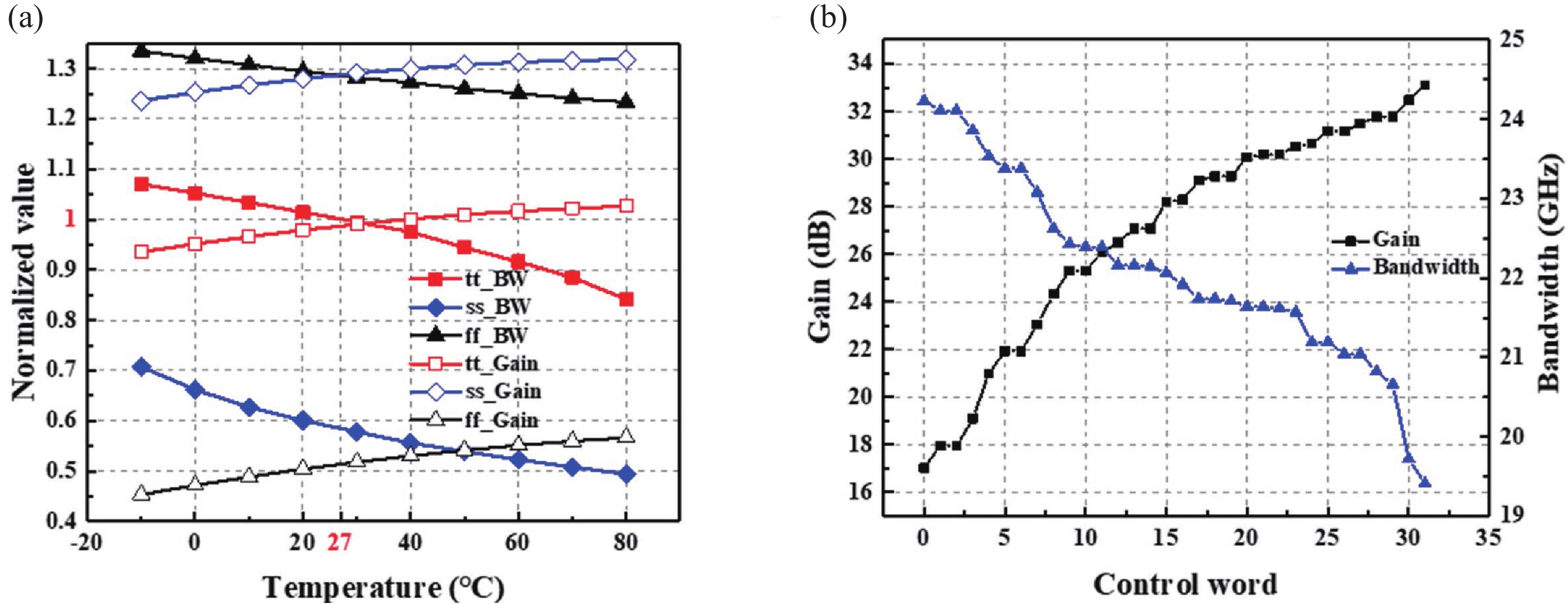

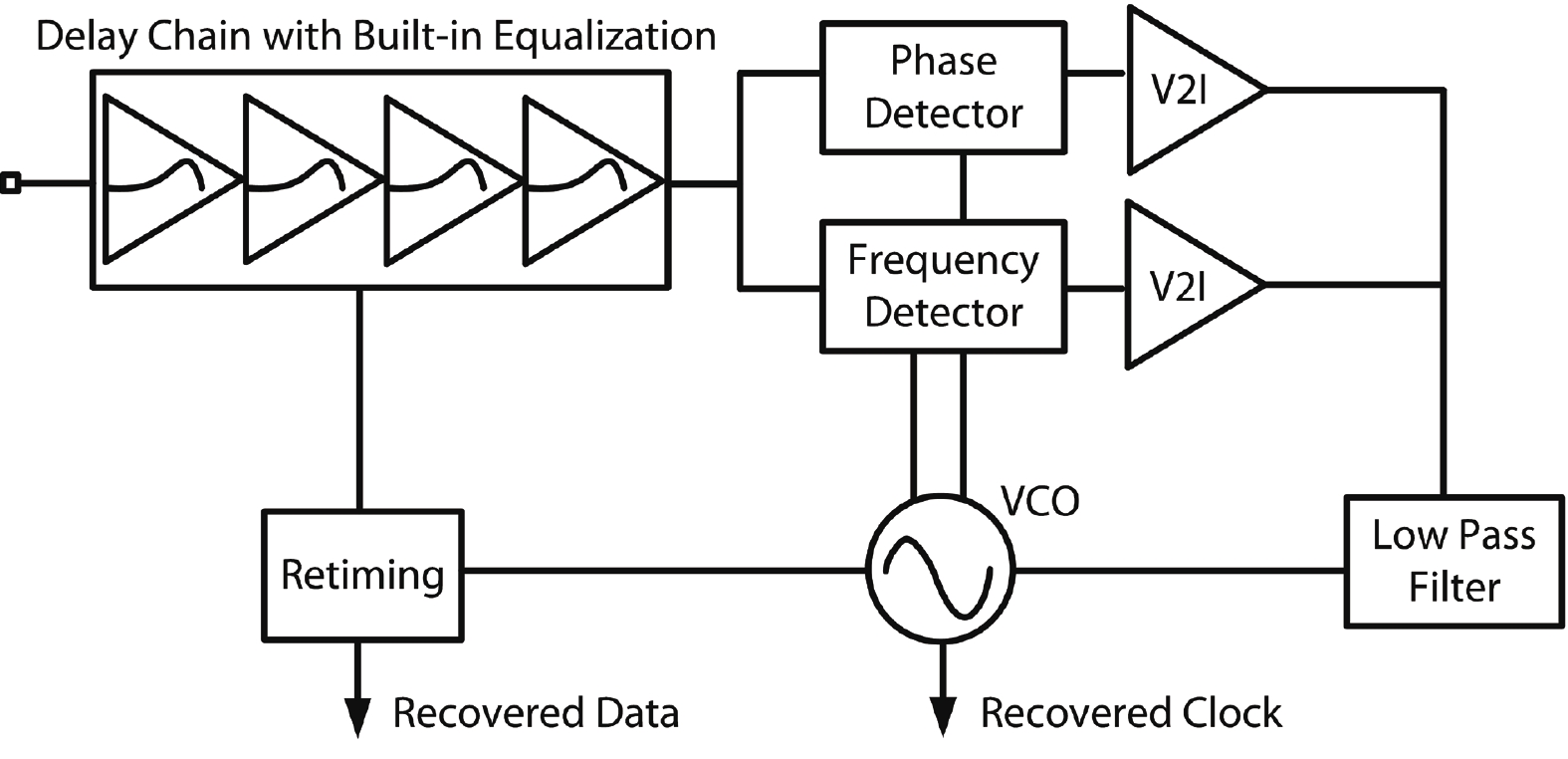

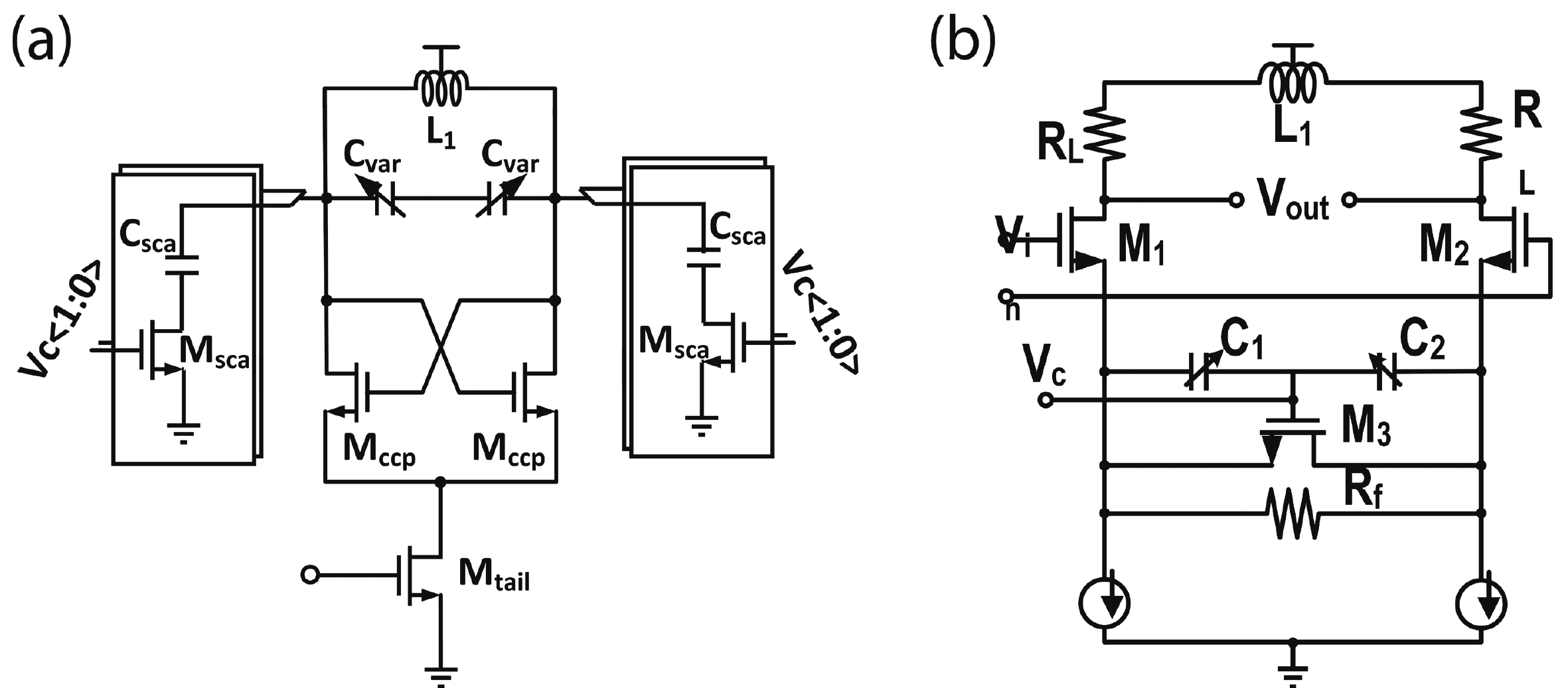

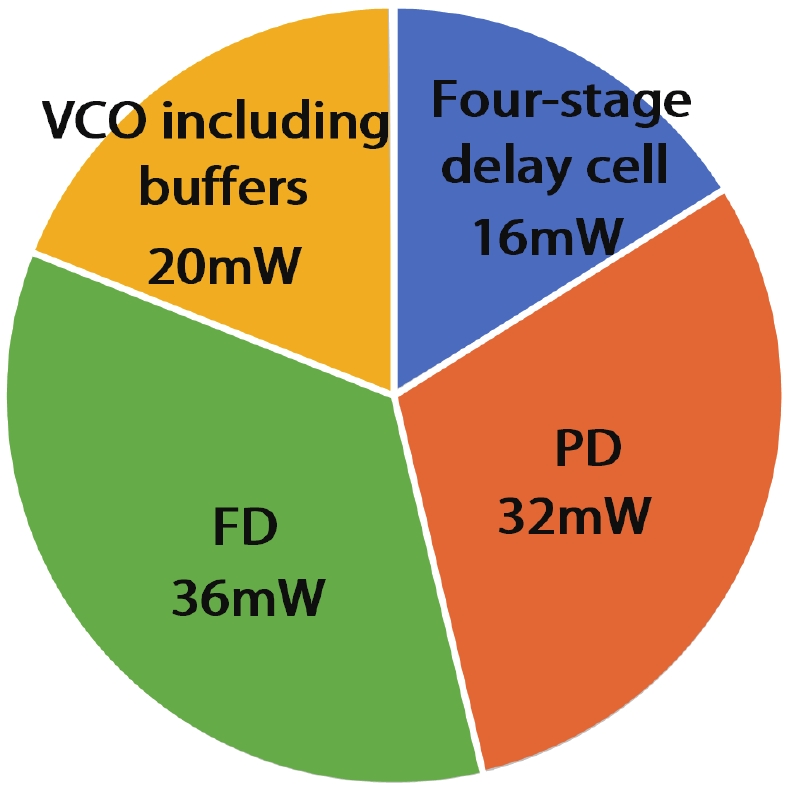

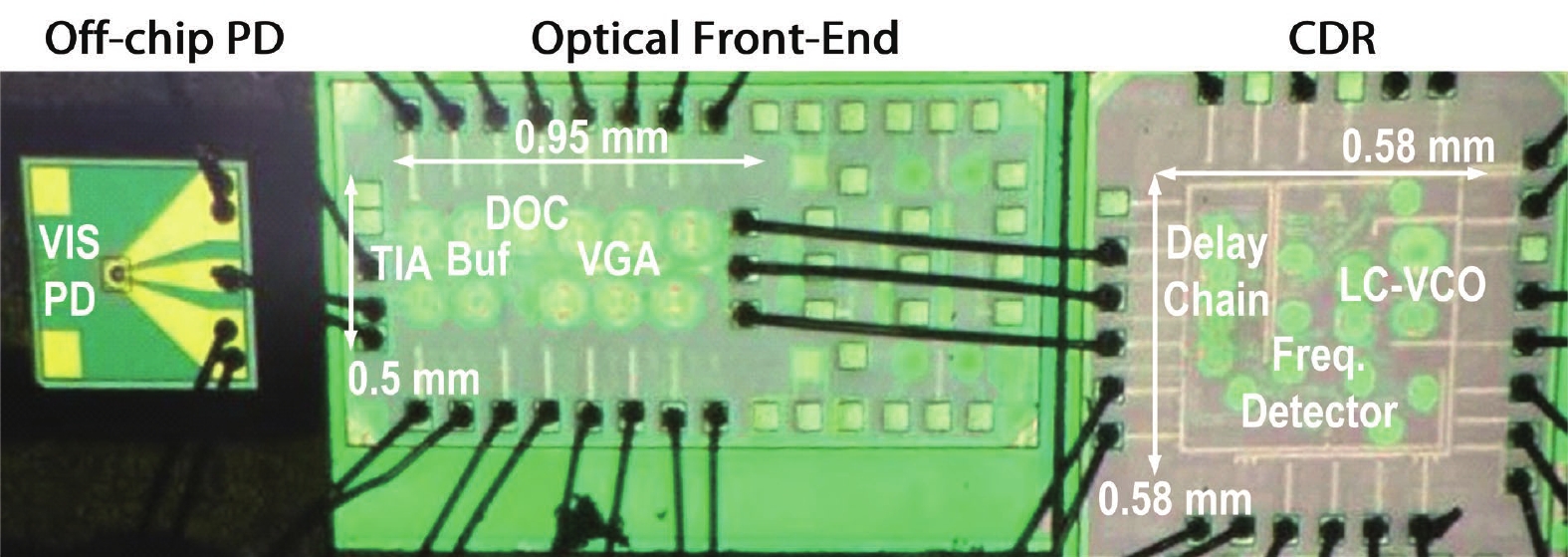

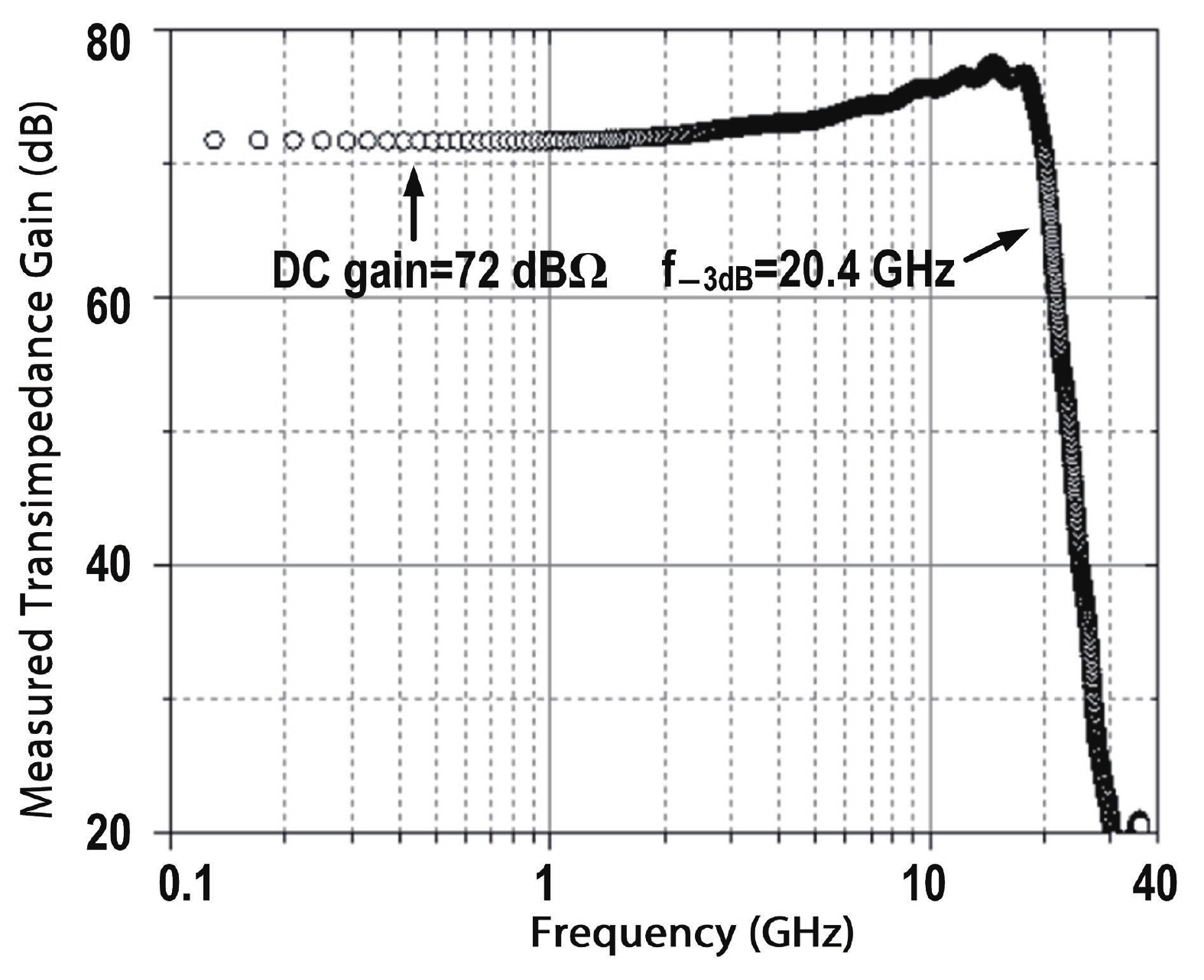

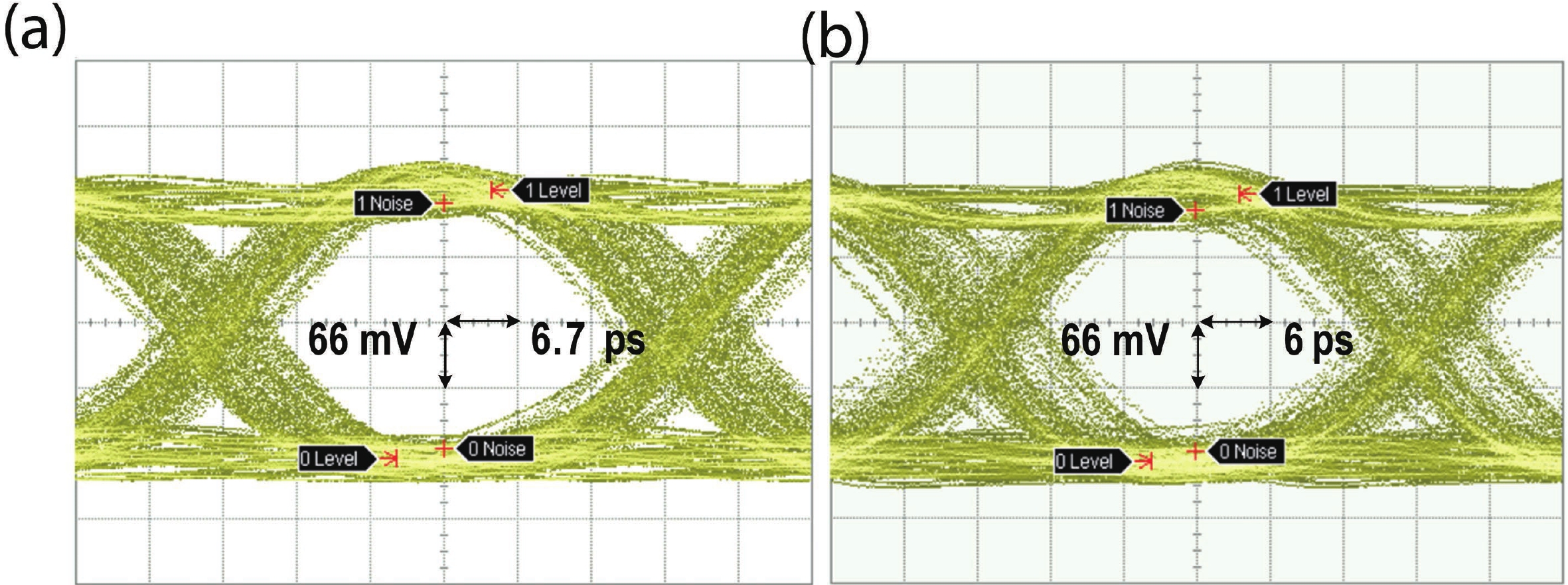

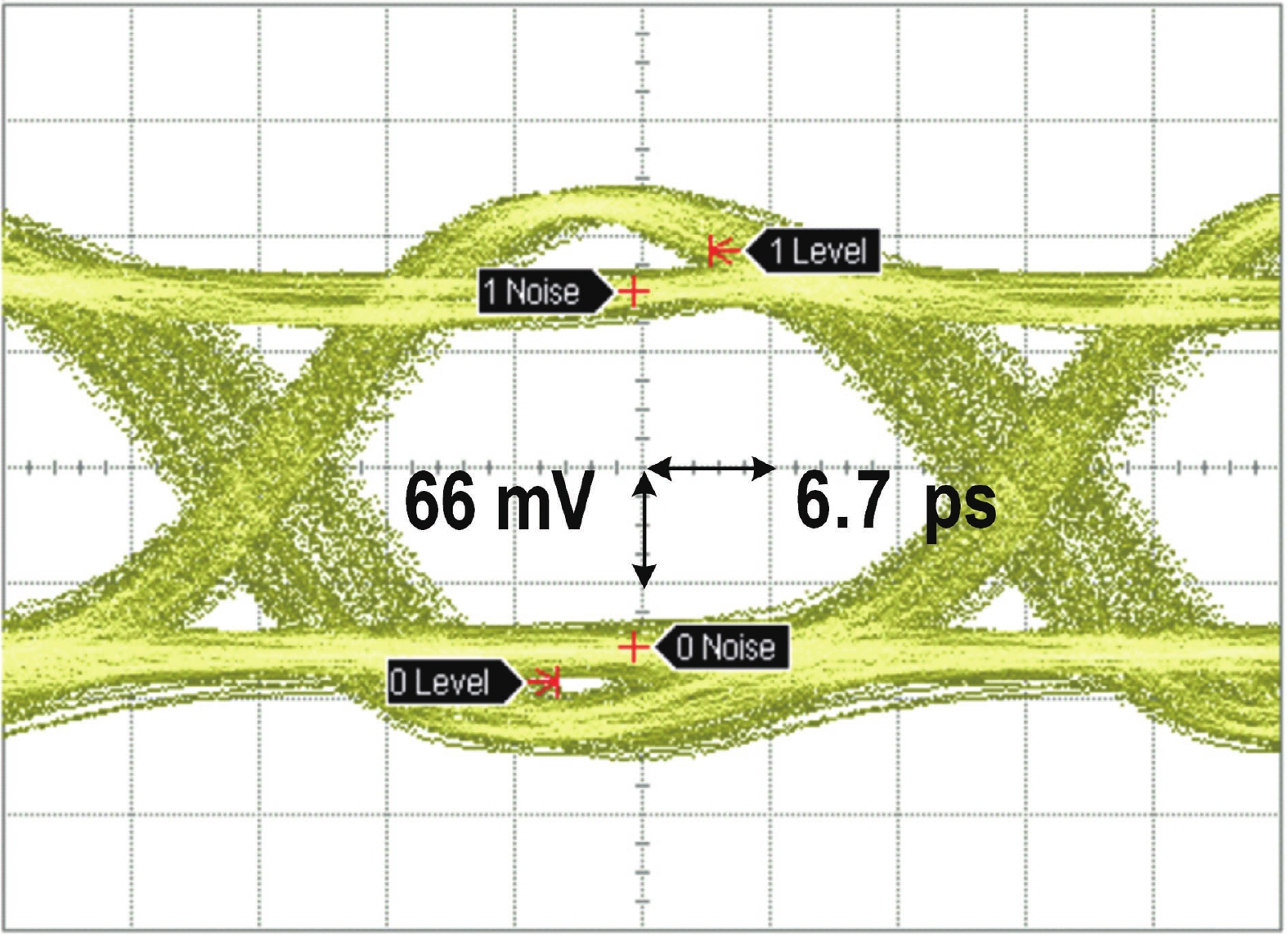

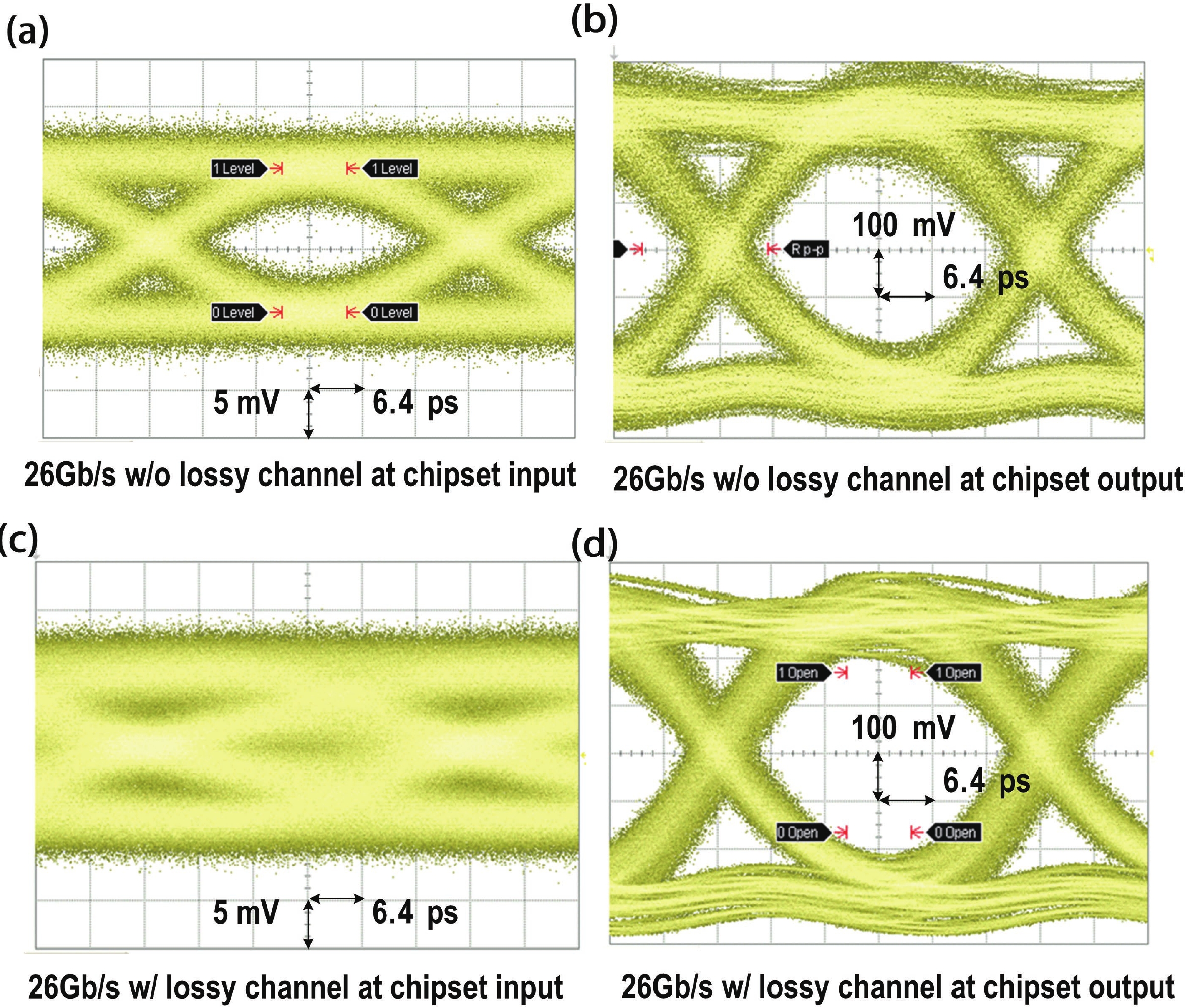

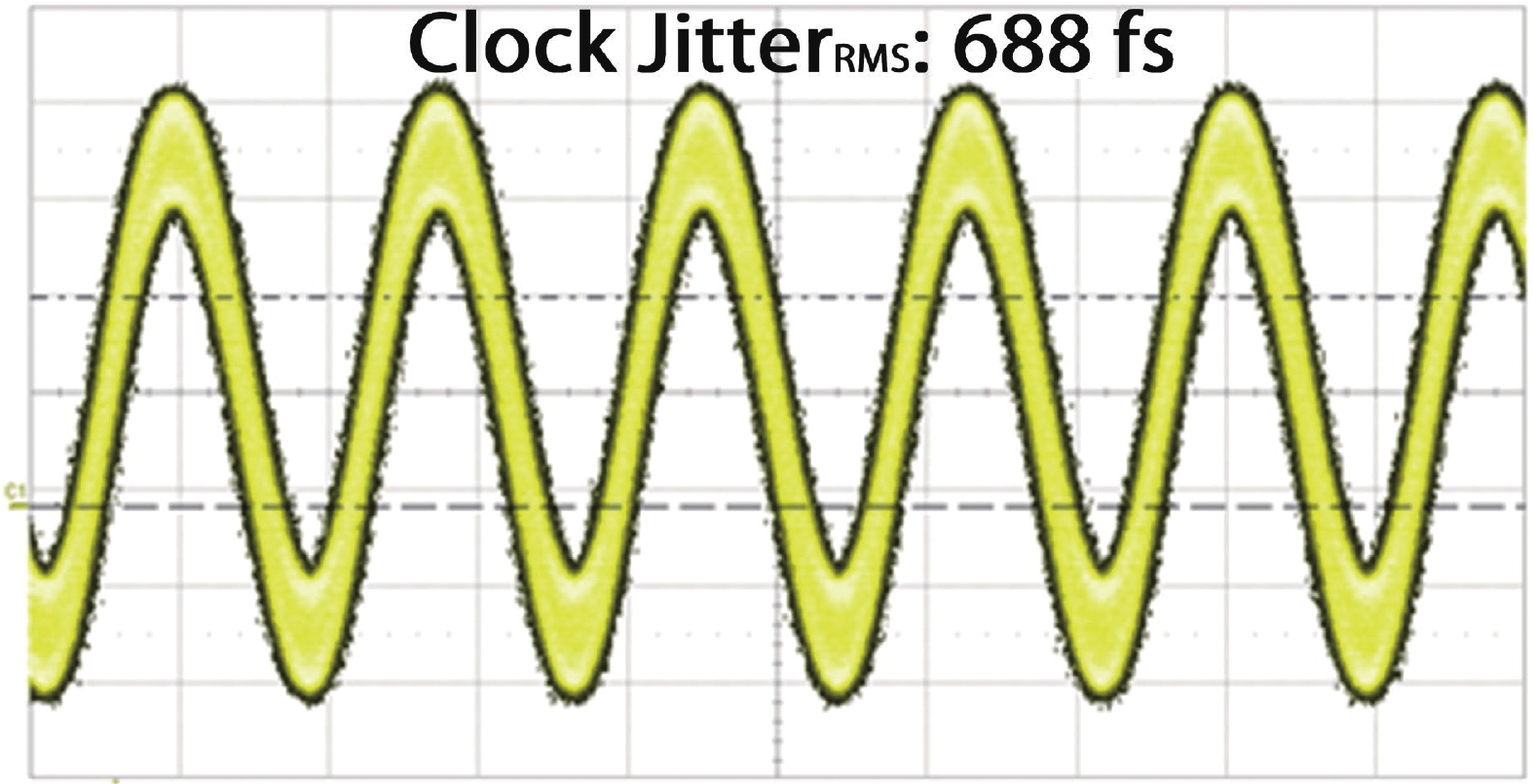

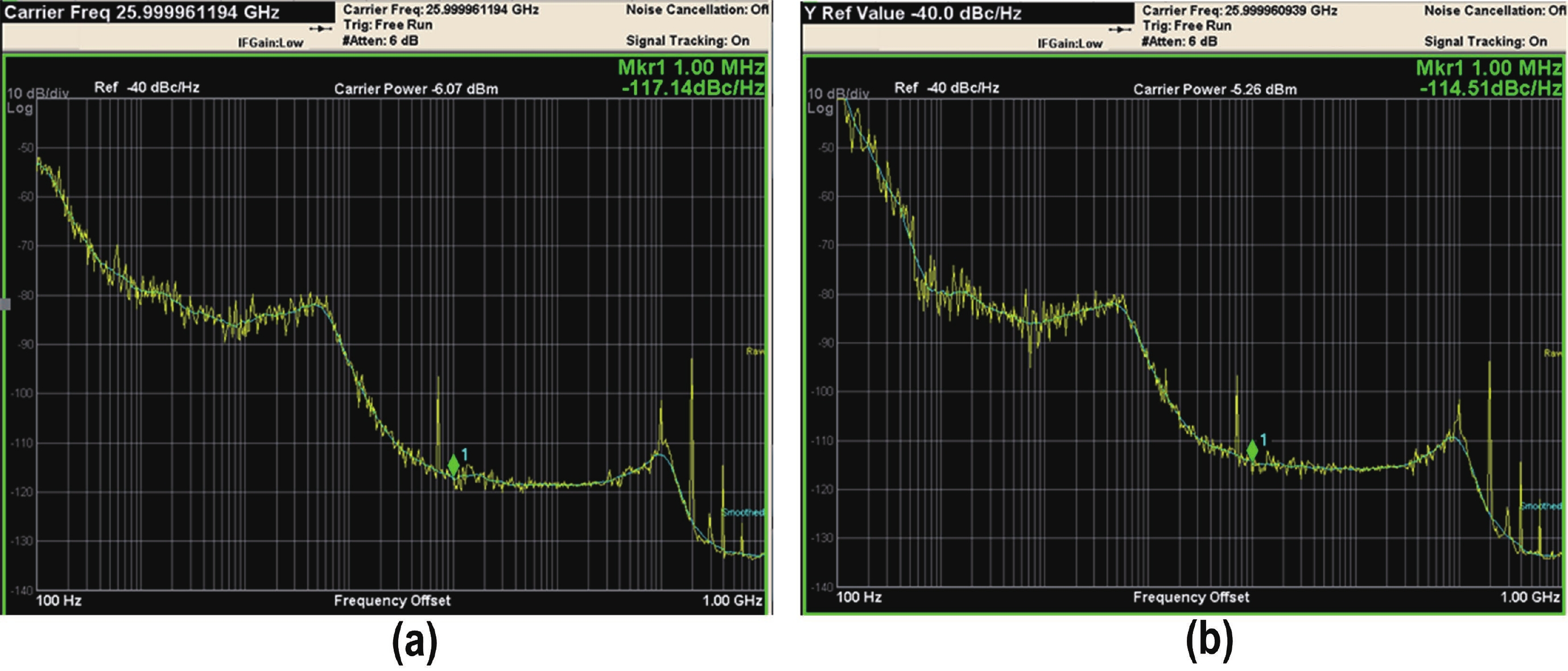

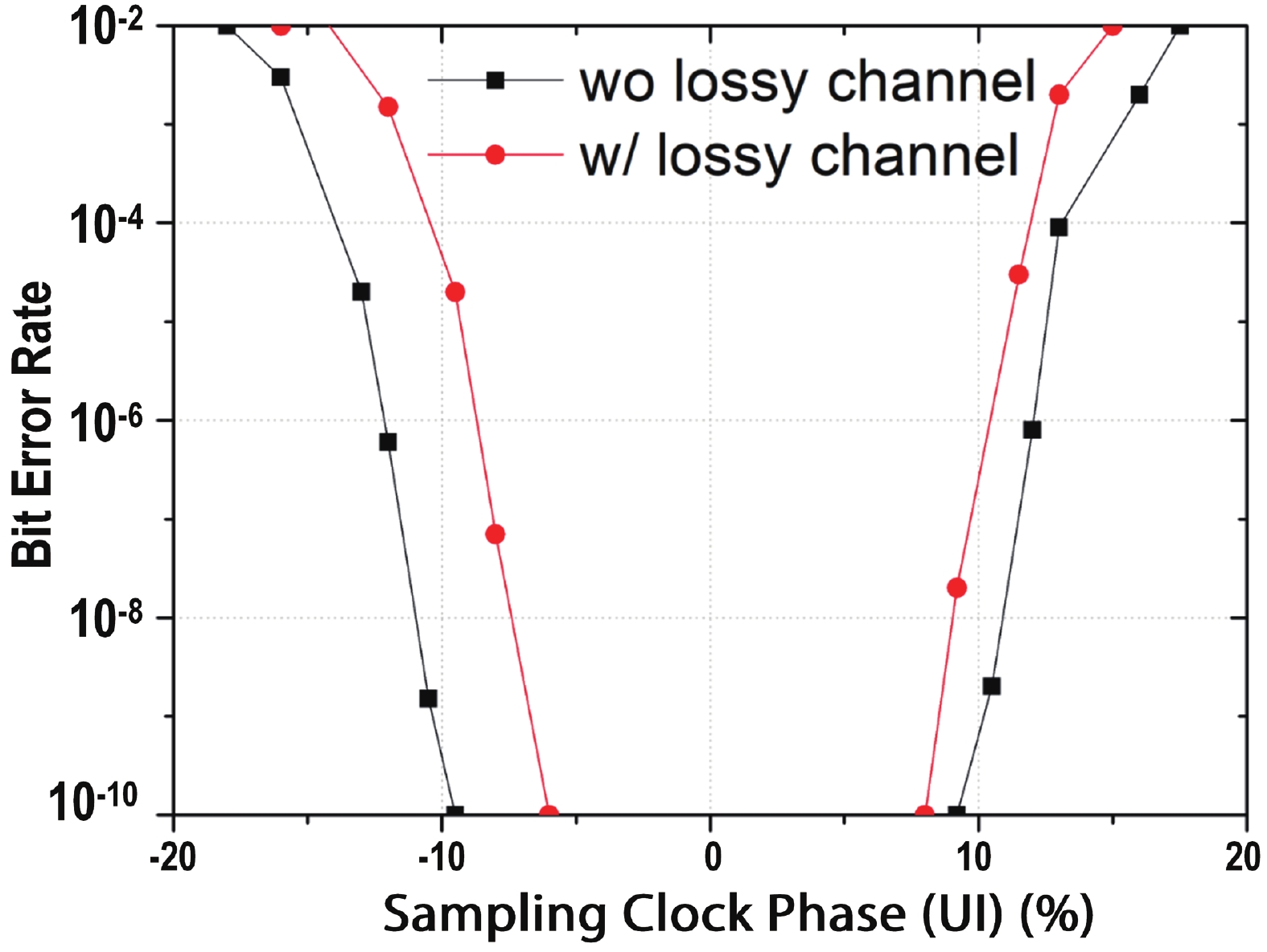

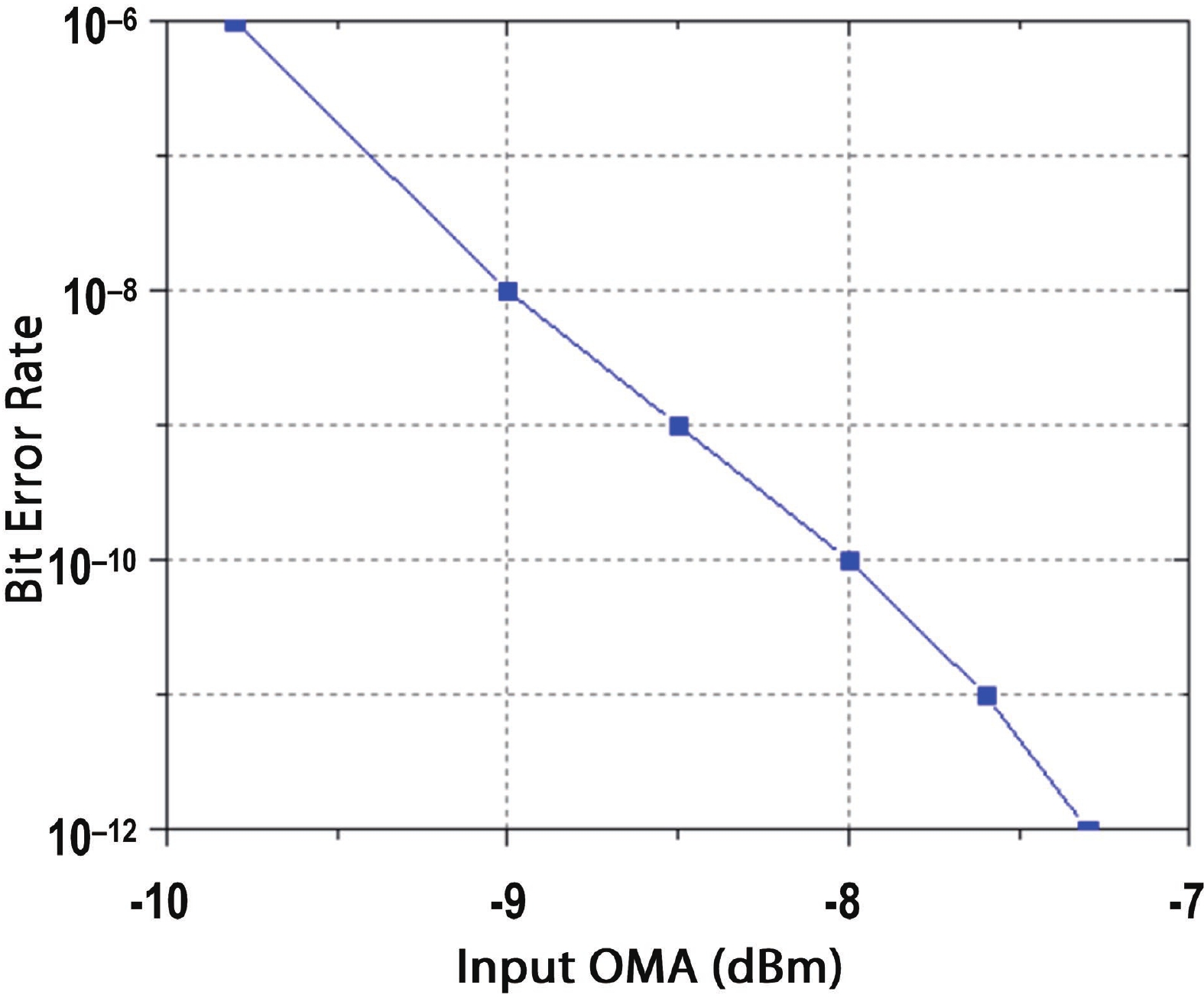

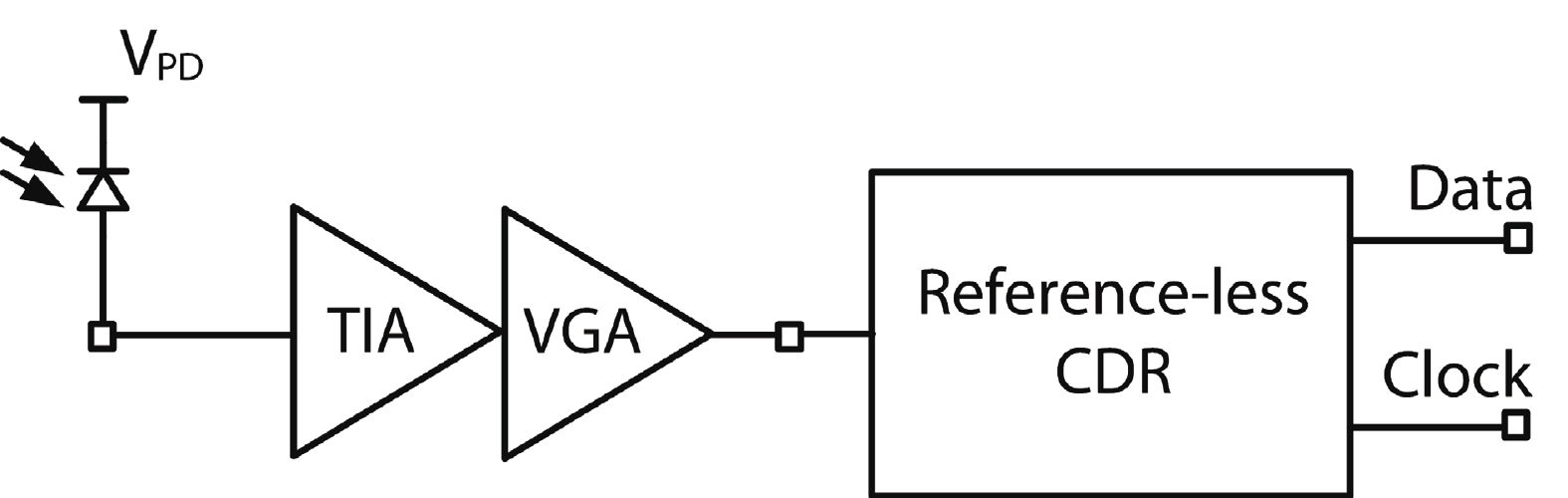

This paper presents a 26-Gb/s CMOS optical receiver that is fabricated in 65-nm technology. It consists of a triple-inductive transimpedance amplifier (TIA), direct current (DC) offset cancellation circuits, 3-stage gm-TIA variable-gain amplifiers (VGA), and a reference-less clock and data recovery (CDR) circuit with built-in equalization technique. The TIA/VGA front-end measurement results demonstrate 72-dBΩ transimpedance gain, 20.4-GHz −3-dB bandwidth, and 12-dB DC gain tuning range. The measurements of the VGA’s resistive networks also demonstrate its efficient capability of overcoming the voltage and temperature variations. The CDR adopts a full-rate topology with 12-dB imbedded equalization tuning range. Optical measurements of this chipset achieve a 10−12 BER at 26 Gb/s for a 215−1 PRBS input with a −7.3-dBm input sensitivity. The measurement results with a 10-dB @ 13 GHz attenuator also demonstrate the effectiveness of the gain tuning capability and the built-in equalization. The entire system consumes 140 mW from a 1/1.2-V supply. -

References

[1] Chiang P C, Jiang J Y, Hung H W, et al. 4 × 25 Gb/s transceiver with optical front-end for 100 GbE system in 65 nm CMOS technology. IEEE J Solid State Circuits, 2015, 50, 573 doi: 10.1109/JSSC.2014.2365700[2] Chu S H, Bae W, Jeong G S, et al. A 22 to 26.5 Gb/s optical receiver with all-digital clock and data recovery in a 65 nm CMOS process. IEEE J Solid State Circuits, 2015, 50, 2603 doi: 10.1109/JSSC.2015.2465843[3] Rahman W, Yoo D, Liang J, et al. A 22.5-to-32-Gb/s 3.2-pJ/b referenceless baud-rate digital CDR with DFE and CTLE in 28-nm CMOS. IEEE J Solid State Circuits, 2017, 52, 3517 doi: 10.1109/JSSC.2017.2744661[4] Ozkaya I, Cevrero A, Francese P A, et al. A 60-Gb/s 1.9-pJ/bit NRZ optical receiver with low-latency digital CDR in 14-nm CMOS FinFET. IEEE J Solid State Circuits, 2018, 53, 1227 doi: 10.1109/JSSC.2017.2778286[5] Tsunoda Y, Shibasaki T, Oku H, et al. 25.78-Gb/s VCSEL-based optical transceiver with retimer-embedded driver and receiver ICs. Optical Fiber Communication Conference, 2015 doi: 10.1364/OFC.2015.Tu3G.4[6] Lee Y S, Ho W H, Chen W Z. A 25-Gb/s, 2.1-pJ/bit, fully integrated optical receiver with a baud-rate clock and data recovery. IEEE J Solid State Circuits, 2019, 54, 2243 doi: 10.1109/JSSC.2019.2907804[7] Han J, Choi B, Seo M, et al. A 20-Gb/s transformer-based current-mode optical receiver in 0.13-μm CMOS. IEEE Trans Circuits Syst II, 2010, 57, 348 doi: 10.1109/TCSII.2010.2047309[8] Komatsu Y, Shinmyo A, Kato S, et al. A 0.25–27-Gb/s PAM4/NRZ transceiver with adaptive power CDR and jitter analysis. IEEE J Solid State Circuits, 2019, 54, 2802 doi: 10.1109/JSSC.2019.2920082[9] Moayedi Pour Fard M, Liboiron-Ladouceur O, Cowan G E R. 1.23-pJ/bit 25-Gb/s inductor-less optical receiver with low-voltage silicon photodetector. IEEE J Solid State Circuits, 2018, 53, 1793 doi: 10.1109/JSSC.2018.2804042[10] Wu K C, Jri L. A 2 × 25Gb/s receiver with 2:5 DMUX for 100Gb/s Ethernet. IEEE J Solid-State Circuits, 2010, 45, 2421 doi: 10.1109/JSSC.2010.2074291[11] Wang Y P, Lu Y, Pan Q, et al. A 3-mW 25-Gb/s CMOS transimpedance amplifier with fully integrated low-dropout regulator for 100GbE systems. 2014 IEEE Radio Freq Integr Circuits Symp, 2014, 275[12] Pan Q, Wang Y P, Lu Y, et al. An 18-Gb/s fully integrated optical receiver with adaptive cascaded equalizer. IEEE J Sel Top Quantum Electron, 2016, 22, 361 doi: 10.1109/JSTQE.2016.2574567[13] Sun L, Pan Q, Wang K C, et al. A 26–28-Gb/s full-rate clock and data recovery circuit with embedded equalizer in 65-nm CMOS. IEEE Trans Circuits Syst I, 2014, 61, 2139 doi: 10.1109/TCSI.2014.2304669[14] Liu L X, Zou J, En Y F, et al. A high gain wide dynamic range transimpedance amplifier for optical receivers. J Semicond, 2014, 35, 015001 doi: 10.1088/1674-4926/35/1/015001[15] Dong Y, Martin K W. A 4-Gbps POF receiver using linear equalizer with multi-shunt-shunt feedbacks in 65-nm CMOS. IEEE Trans Circuits Syst II, 2013, 60, 617 doi: 10.1109/TCSII.2013.2273839[16] Pan Q, Luo X S. A 58-dBΩ 20-Gb/s inverter-based cascode transimpedance amplifier for optical communications. J Semicond, 2022, 43, 012401 doi: 10.1088/1674-4926/43/1/012401[17] Chen Y, Mak P I, Boon C C, et al. A 36-Gb/s 1.3-mW/Gb/s duobinary-signal transmitter exploiting power-efficient cross-quadrature clocking multiplexers with maximized timing margin. IEEE Trans Circuits Syst I, 2018, 65, 3014 doi: 10.1109/TCSI.2018.2829725[18] Chen Y, Mak P I, Boon C C, et al. A 27-Gb/s time-interleaved duobinary transmitter achieving 1.44-mW/Gb/s FOM in 65-nm CMOS. IEEE Microwave Wirel Compon Lett, 2017, 27, 839 doi: 10.1109/LMWC.2017.2735548[19] Zhao X T, Chen Y, Mak P I, et al. A 0.0018-mm2 153% locking-range CML-based divider-by-2 with tunable self-resonant frequency using an auxiliary negative-gm cell. IEEE Trans Circuits Syst I, 2019, 66, 3330 doi: 10.1109/TCSI.2019.2925090[20] He J, Zhang Y G, Liu H, et al. A 56-Gb/s reconfigurable silicon-photonics transmitter using high-swing distributed driver and 2-tap in-segment feed-forward equalizer in 65-nm CMOS. IEEE Trans Circuits Syst I, 2022, 69, 1159 doi: 10.1109/TCSI.2021.3127723[21] Kong L S, Chen Y, Boon C C, et al. A wideband inductorless dB-linear automatic gain control amplifier using a single-branch negative exponential generator for wireline applications. IEEE Trans Circuits Syst I, 2018, 65, 3196 doi: 10.1109/TCSI.2018.2827065[22] Chen Y, Mak P, Yu H, et al. An area-efficient and tunable bandwidth- extension technique for a wideband CMOS amplifier handling 50+ Gb/s signaling. IEEE Trans Microwave Theory Tech, 2017, 65, 4960 doi: 10.1109/TMTT.2017.2720600[23] Wang J, Pan Q, Qin Y, et al. A fully integrated 25 Gb/s low-noise TIA+CDR optical receiver designed in 40-nm-CMOS. IEEE Trans Circuits Syst II, 2019, 66, 1698 doi: 10.1109/TCSII.2019.2925363[24] Zhao X T, Chen Y, Mak P I, et al. A 0.0285mm2 0.68pJ/bit single-loop full-rate bang-bang CDR without reference and separate frequency detector achieving an 8.2(Gb/s)/µs acquisition speed of PAM-4 data in 28nm CMOS. 2020 IEEE Custom Integrated Circuits Conference, 2020, 1 doi: 10.1109/CICC48029.2020.9075885[25] Zhao X T, Chen Y, Wang L, et al. A sub-0.25pJ/bit 47.6-to-58.8Gb/s reference-less FD-less single-loop PAM-4 Bang-Bang CDR with a deliberately-current-mismatch frequency acquisition technique in 28nm CMOS. 2021 IEEE Radio Frequency Integrated Circuits Symposium, 2021, 131 doi: 10.1109/RFIC51843.2021.9490486[26] Zhao X T, Chen Y, Mak P I, et al. A 0.14-to-0.29-pj/bit 14-GBaud/s trimodal (NRZ/PAM-4/PAM-8) half-rate bang-bang clock and data recovery (BBCDR) circuit in 28-nm CMOS. IEEE Trans Circuits Syst I, 2021, 68, 89 doi: 10.1109/TCSI.2020.3038865[27] Balachandran A, Chen Y, Boon C C. A 32-Gb/s 3.53-mW/Gb/s adaptive receiver AFE employing a hybrid CTLE, edge-DFE and merged data-DFE/CDR in 65-nm CMOS. 2019 IEEE Asia Pacific Conference on Circuits and Systems, 2019, 221 doi: 10.1109/APCCAS47518.2019.8953146[28] Liao Q W, Zhang Y G, Ma S Y, et al. A 50-Gb/s PAM-4 silicon-photonic transmitter incorporating lumped-segment MZM, distributed CMOS driver, and integrated CDR. IEEE J Solid State Circuits, 2022, 57, 767 doi: 10.1109/JSSC.2021.3134874[29] Zhong M, Wang Q W, Chen Y, et al. A 4 × 25-Gb/s serializer with integrated CDR and 3-tap FFE driver for NIC optical interconnects. 2021 IEEE International Conference on Integrated Circuits, Technologies and Applications, 2021, 255 doi: 10.1109/ICTA53157.2021.9661798 -

Proportional views

DownLoad:

DownLoad: