| Citation: |

Yuhao Xia, Shanglin Yang, Jiaqi Niu, Xin Fu, Lin Yang. Strict non-blocking four-port optical router for mesh photonic network-on-chip[J]. Journal of Semiconductors, 2022, 43(9): 092301. doi: 10.1088/1674-4926/43/9/092301

****

Y H Xia, S L Yang, J Q Niu, X Fu, L Yang. Strict non-blocking four-port optical router for mesh photonic network-on-chip[J]. J. Semicond, 2022, 43(9): 092301. doi: 10.1088/1674-4926/43/9/092301

|

Strict non-blocking four-port optical router for mesh photonic network-on-chip

DOI: 10.1088/1674-4926/43/9/092301

More Information

-

Abstract

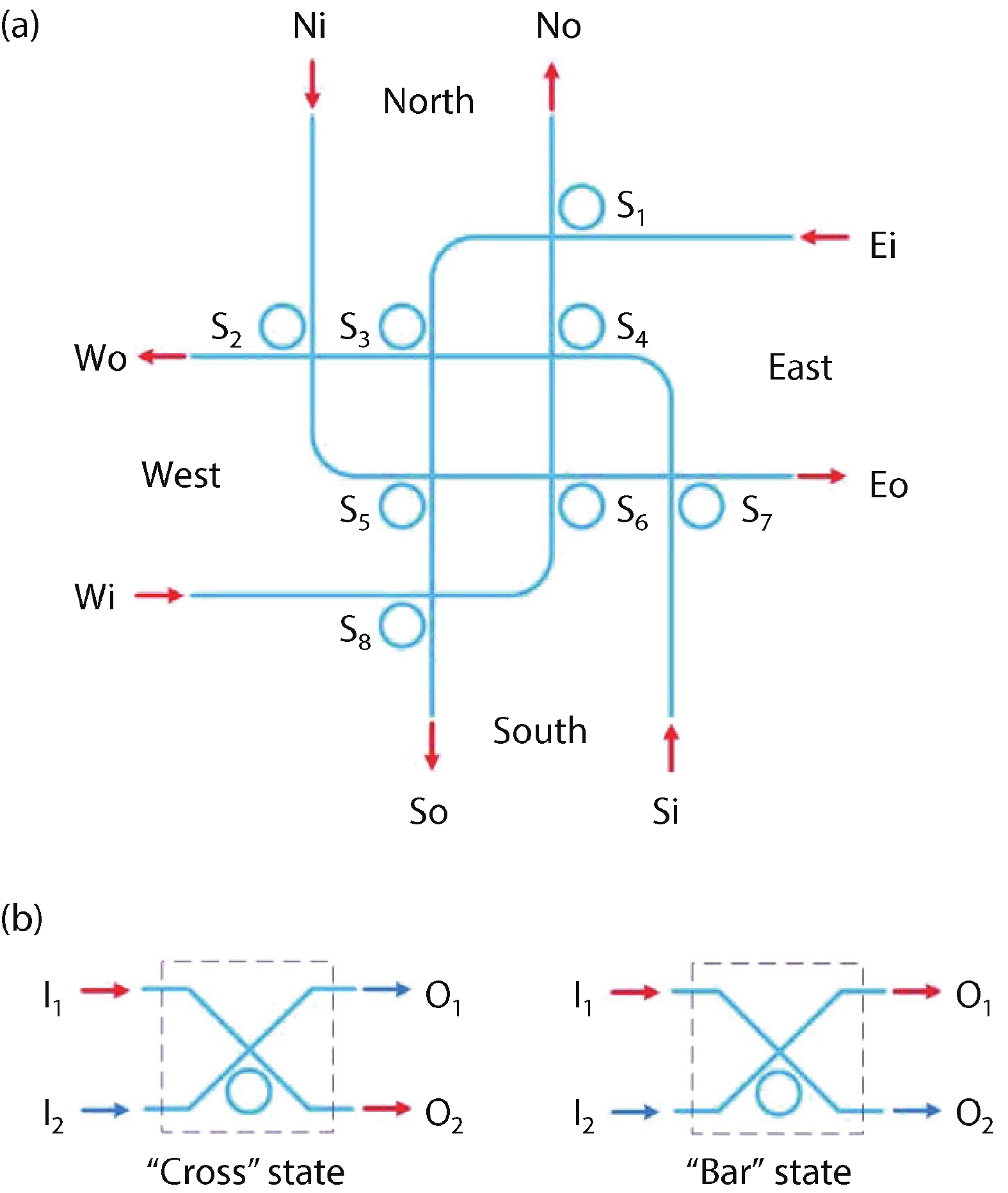

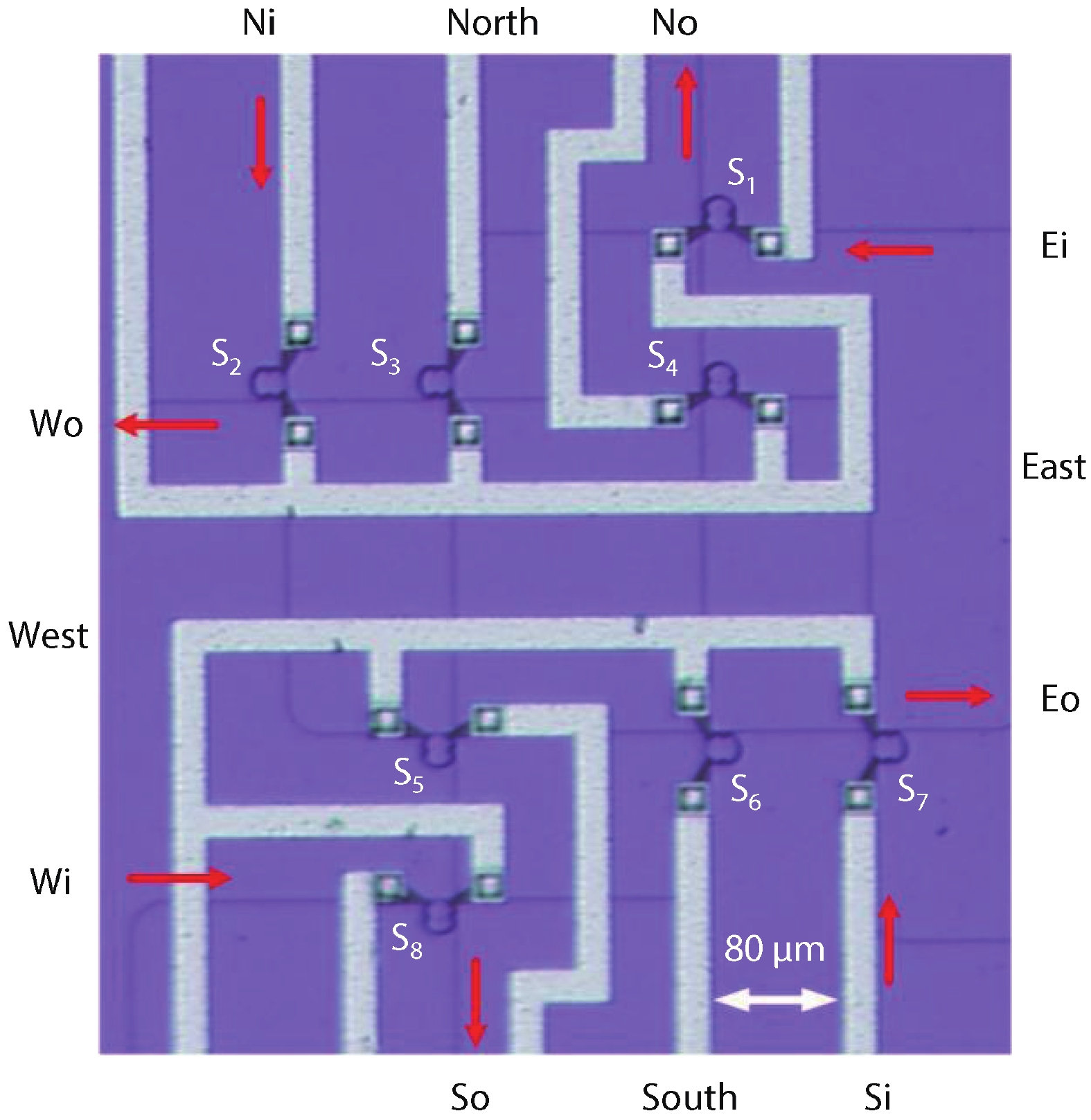

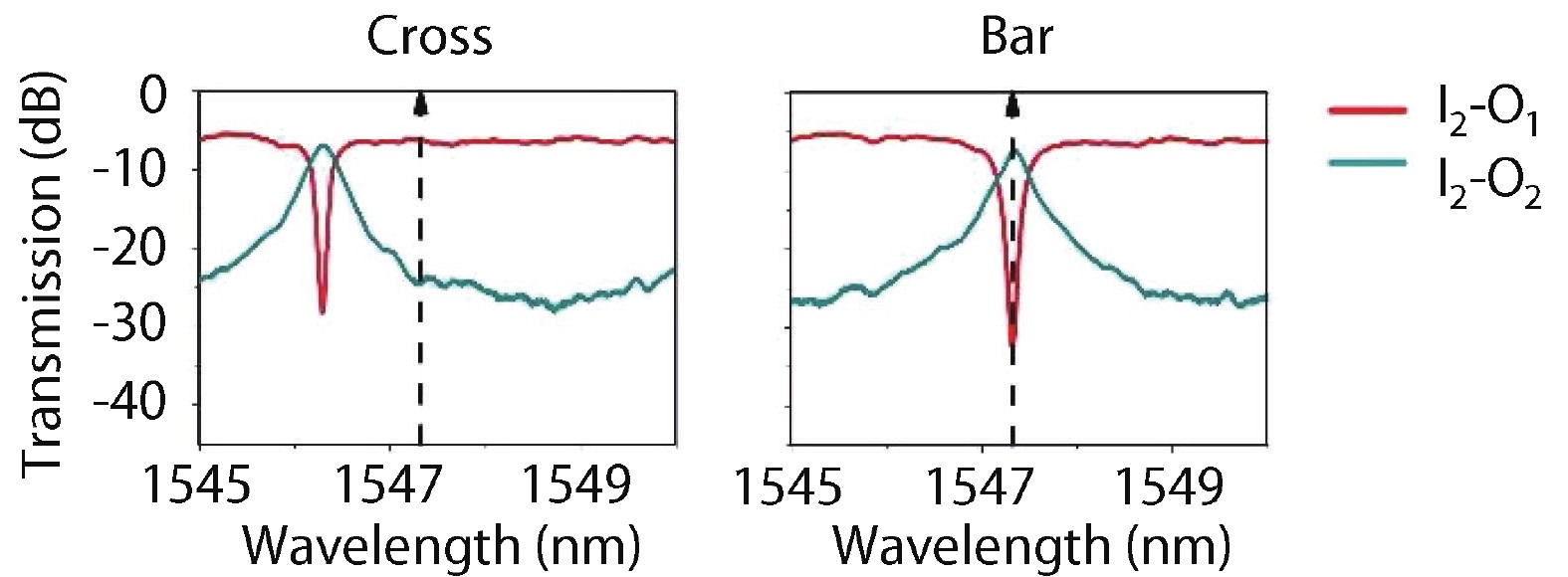

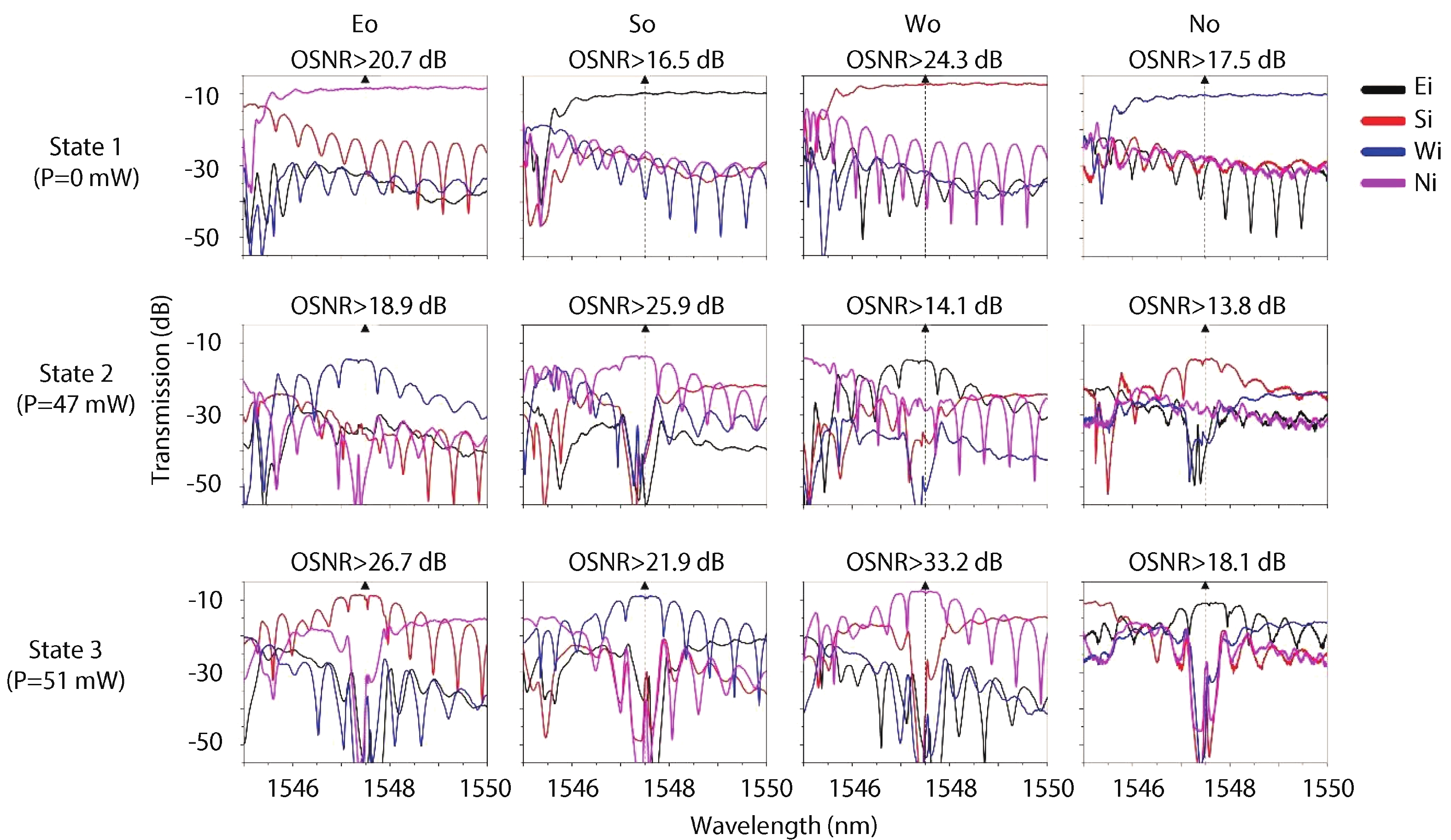

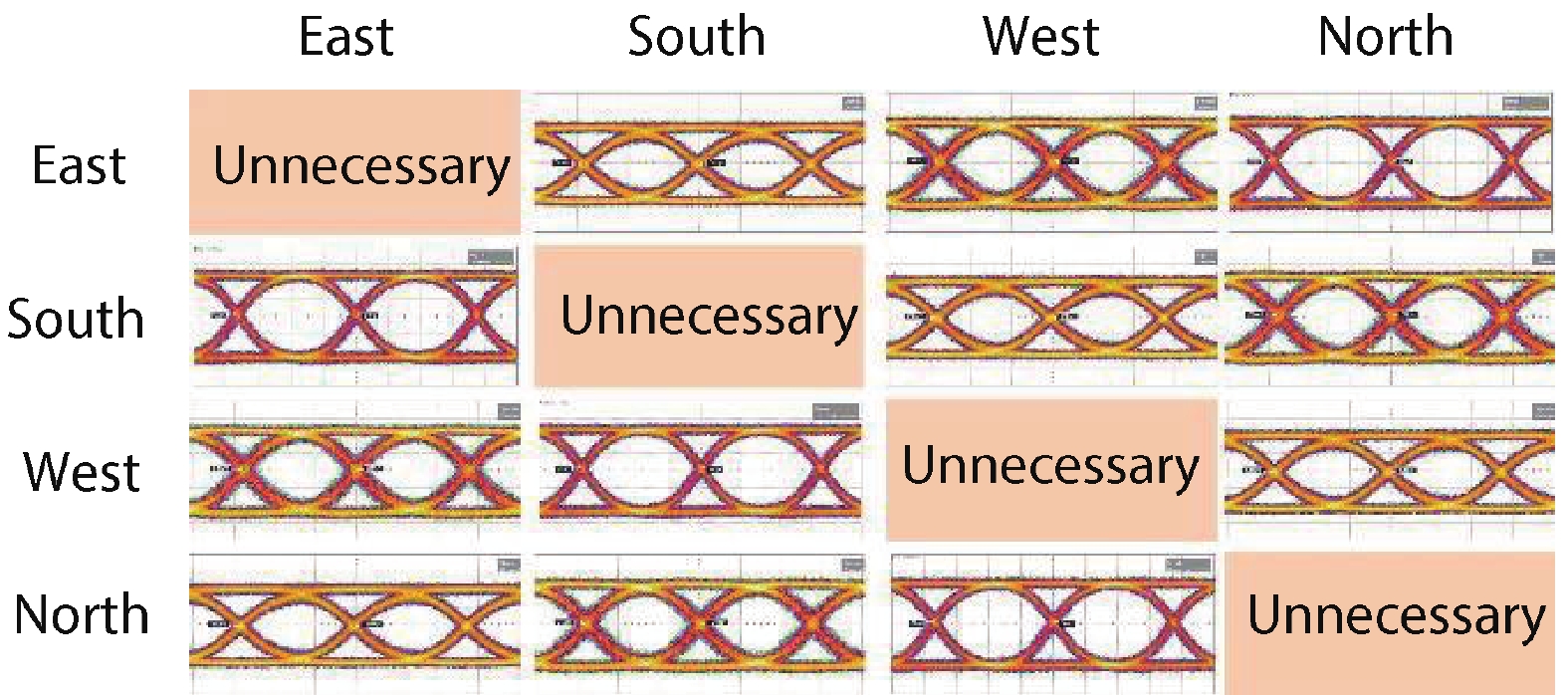

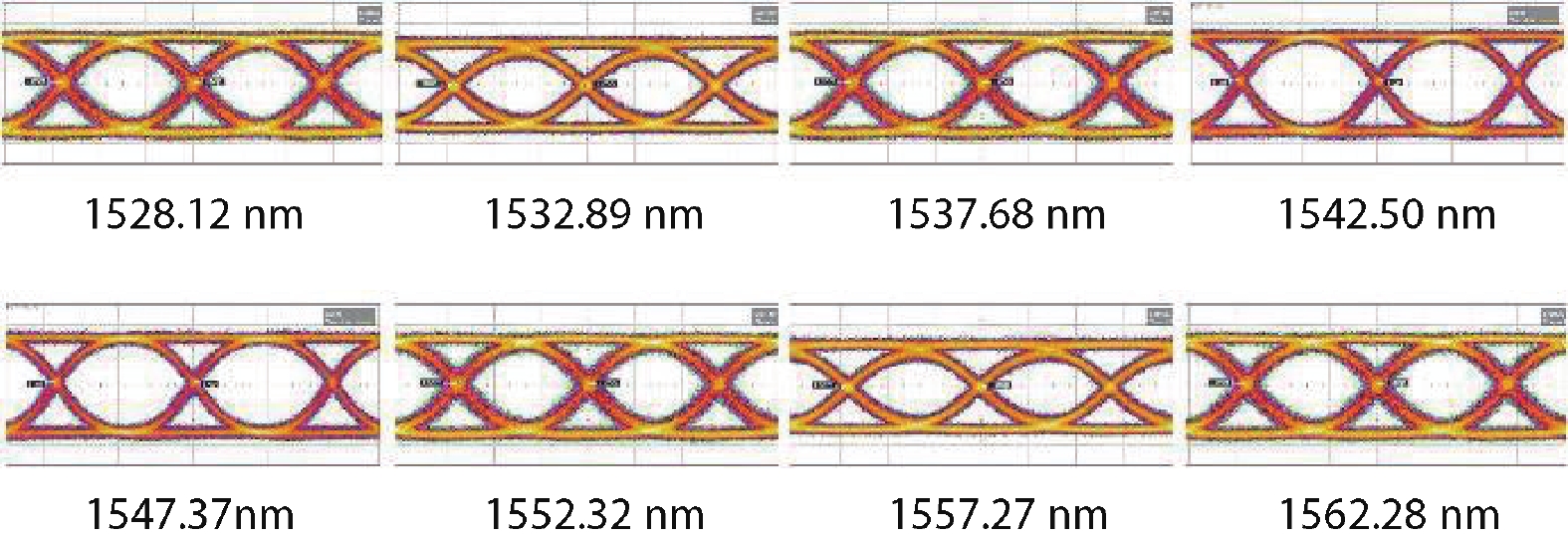

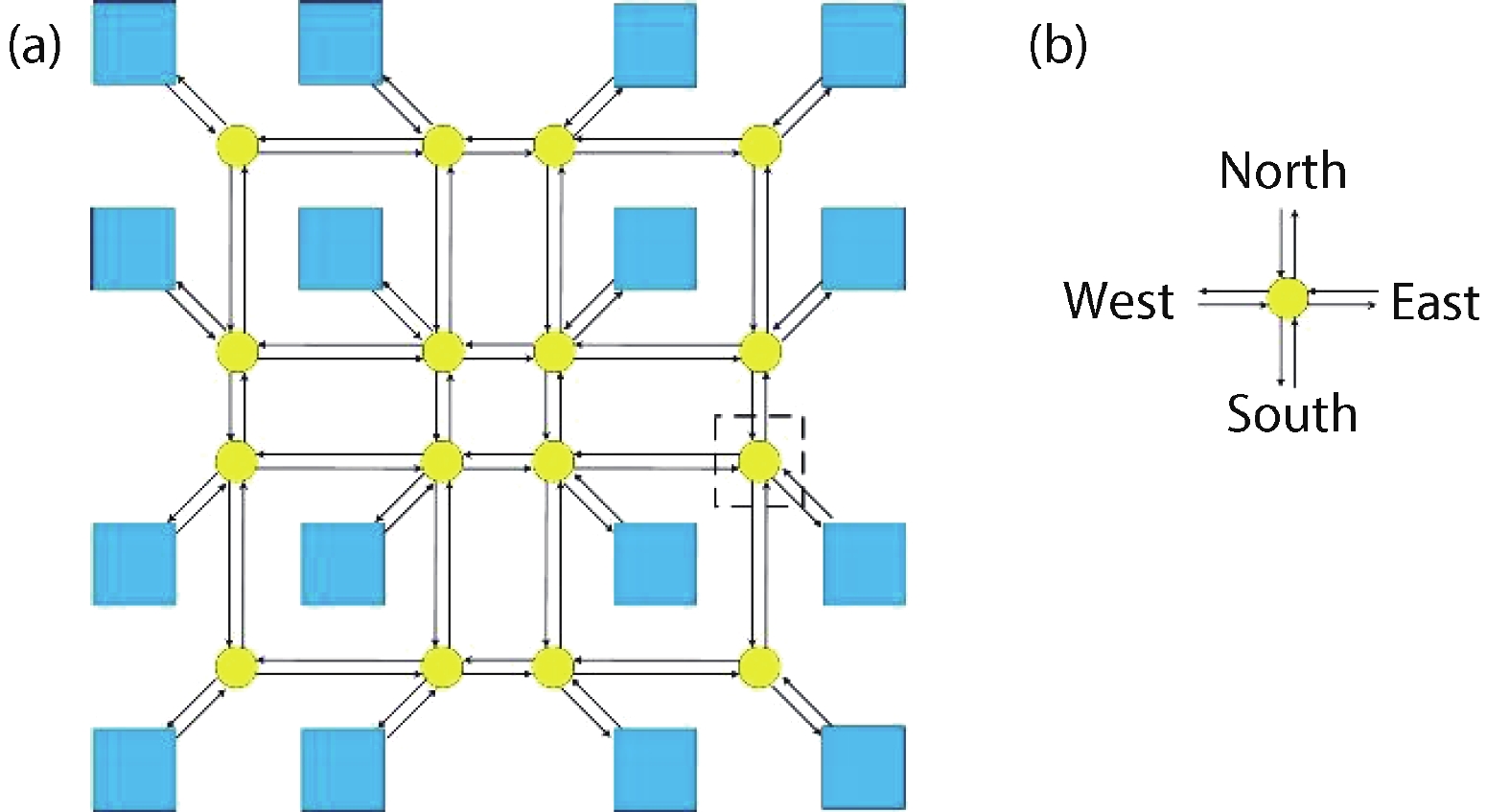

We report a strict non-blocking four-port optical router that is used for a mesh photonic network-on-chip on a silicon-on-insulator platform. The router consists of eight silicon microring switches that are tuned by the thermo-optic effect. For each tested rousting state, the signal-to-noise ratio of the optical router is larger than 13.8 dB at the working wavelength. The routing functionality of the device is verified. We perform 40 Gbps nonreturn to zero code data transmission on its 12 optical links. Meanwhile, data transmission using wavelength division multiplexing on eight channels in the C band (from 1525 to 1565 nm) has been adopted to increase the communication capacity. The optical router’s average energy efficiency is 25.52 fJ/bit. The rising times (10% to 90%) of the eight optical switch elements are less than 10 µs and the falling times (90%–10%) are less than 20 µs. -

References

[1] Beausoleil R G, Kuekes P J, Snider G S, et al. Nanoelectronic and nanophotonic interconnect. Proc IEEE, 2007, 96(2), 230 doi: 10.1109/JPROC.2007.911057[2] Miller D A B. Device requirements for optical interconnects to silicon chips. Proc IEEE, 2009, 97, 1166 doi: 10.1109/JPROC.2009.2014298[3] Batten C, Joshi A, Orcutt J, et al. Building manycore processor-to-DRAM networks with monolithic silicon photonics. 16th IEEE Symposium on High Performance Interconnects, 2008 doi: 10.1109/MM.2009.60[4] Gu H X, Xu J, Zhang W. A low-power fat tree-based optical network-on-chip for multiprocessor system-on-chip. Design, Automation & Test in Europe Conference & Exhibition, 2009 doi: 10.1109/DATE.2009.5090624[5] Joshi A, Batten C, Kwon Y J, et al. Silicon-photonic clos networks for global on-chip communication. 3rd ACM/IEEE International Symposium on Networks-on-Chip, 2009 doi: 10.1109/NOCS.2009.5071460[6] Gu H X, Mo K H, Xu J, et al. A low-power low-cost optical router for optical networks-on-chip in multiprocessor systems-on-chip. IEEE Computer Society Annual Symposium on VLSI, 2009 doi: 10.1109/ISVLSI.2009.19[7] Sherwood-Droz N, Wang H, Chen L, et al. Optical 4 × 4 hitless silicon router for optical Networks-on-Chip (NoC). Opt Express, 2008, 16(20), 15915 doi: 10.1364/OE.16.015915[8] Kamierczak A, Bogaerts W, Drouard E, et al. Highly integrated optical 4 × 4 crossbar in Silicon-on-Insulator technology. IEEE J Lightwave Technol, 2009, 27(16), 3317 doi: 10.1109/JLT.2008.2010462[9] Ji R Q, Yang L, Zhang L, et al. Five-port optical router for photonic networks-on-chip. Opt Express, 2011, 19(21), 20258 doi: 10.1364/OE.19.020258[10] Ye Y, Wu X W, Xu J, et al. Holistic comparison of optical routers for chip multiprocessors. IEEE International Conference on Anti-counterfeiting, Security, and Identification, 2012 doi: 10.1109/ICASID.2012.6325348[11] Chan J, Biberman A, Lee B G, et al. Insertion loss analysis in a photonic interconnection network for on-chip and off-chip communications. 21st Annual Meeting of the IEEE Lasers and Electro-Optics Society (LEOS 2008), 2008 doi: 10.1109/LEOS.2008.4688609[12] Renani N B, Yaghoubi E, Sadehnezhad N, et al. NLR-OP: a high-performance optical router based on North-Last turning model for multicore processors. J Supercomput, 2022, 78(6), 2442 doi: 10.1007/s11227-021-03920-3[13] Dang P P, Li C T, Zheng W X, et al. Non-blocking four-port optical router based on thermooptic silicon microrings. Optoelectron Lett, 2016, 12(4), 268 doi: 10.1007/s11801-016-6105-3[14] Rhee H W, You J B, Yoon H, et al. 32 Gbps data transmission with 2D beam-steering using a silicon optical phased array. IEEE Photonics Technol Lett, 2020, 32(13), 803 doi: 10.1109/LPT.2020.2998162[15] Jia H, Zhou T, Yang S, et al. Five-port non-blocking silicon optical router based on mode-selective property. 18th International Conference on Optical Communications and Networks (ICOCN), 2019, 1 doi: 10.1109/ICOCN.2019.8934430[16] Geng M, Tang Z, Chang K, et al. N-port strictly non-blocking optical router based on Mach-Zehnder optical switch for photonic networks-on-chip. Opt Commun, 2017, 383, 472 doi: 10.1016/j.optcom.2016.09.023[17] Xia L I, Jiang X Q, Wang X F. A 4 × 4 non-blocking wavelength selective router based on cascaded two-ring resonators. J Optoelectron Laser, 2019, 30(7), 678[18] Surenkhorol T, Kishikawa H, Goto N. Integrated-optic circuit for optical 8QAM coded label recognition in photonic router. Integrated Photonics Research, Silicon & Nanophotonics, 2017 doi: 10.1364/IPRSN.2017.JTu4A.26[19] Mohamed S, Shahada L, Swillam M. Vertical silicon nanowires based directional coupler optical router. IEEE Photonics Technol Lett, 2018, 30(9), 789 doi: 10.1109/LPT.2018.2815040[20] Kalange O A, Ladniya B B, Kothari R R, et al. Design and analysis of five port optical router for optical NoC. 2018 International Conference on Inventive Research in Computing Applications (ICIRCA), 2018 doi: 10.1109/ICIRCA.2018.8597198[21] Cheng Q, Liang Y D, Bahadori M, et al. Si/SiN microring-based optical router in switch-and-select topology. 2018 European Conference on Optical Communication (ECOC), 2018 doi: 10.1109/ECOC.2018.8535403[22] Ge Z, Zhang L, Wang G, et al. On-chip router elements based on silicon hybrid plasmonic waveguide. IEEE Photonics Technol Lett, 2017, 29(12), 952 doi: 10.1109/LPT.2017.2695081 -

Proportional views

DownLoad:

DownLoad: