| Citation: |

Chao Cao, Zhangming Zhu. High-resolution 1 MS/s sub-2 radix split-capacitor SAR ADC[J]. Journal of Semiconductors, 2017, 38(10): 105008. doi: 10.1088/1674-4926/38/10/105008

****

C Cao, Z M Zhu. High-resolution 1 MS/s sub-2 radix split-capacitor SAR ADC[J]. J. Semicond., 2017, 38(10): 105008. doi: 10.1088/1674-4926/38/10/105008.

|

High-resolution 1 MS/s sub-2 radix split-capacitor SAR ADC

DOI: 10.1088/1674-4926/38/10/105008

More Information

-

Abstract

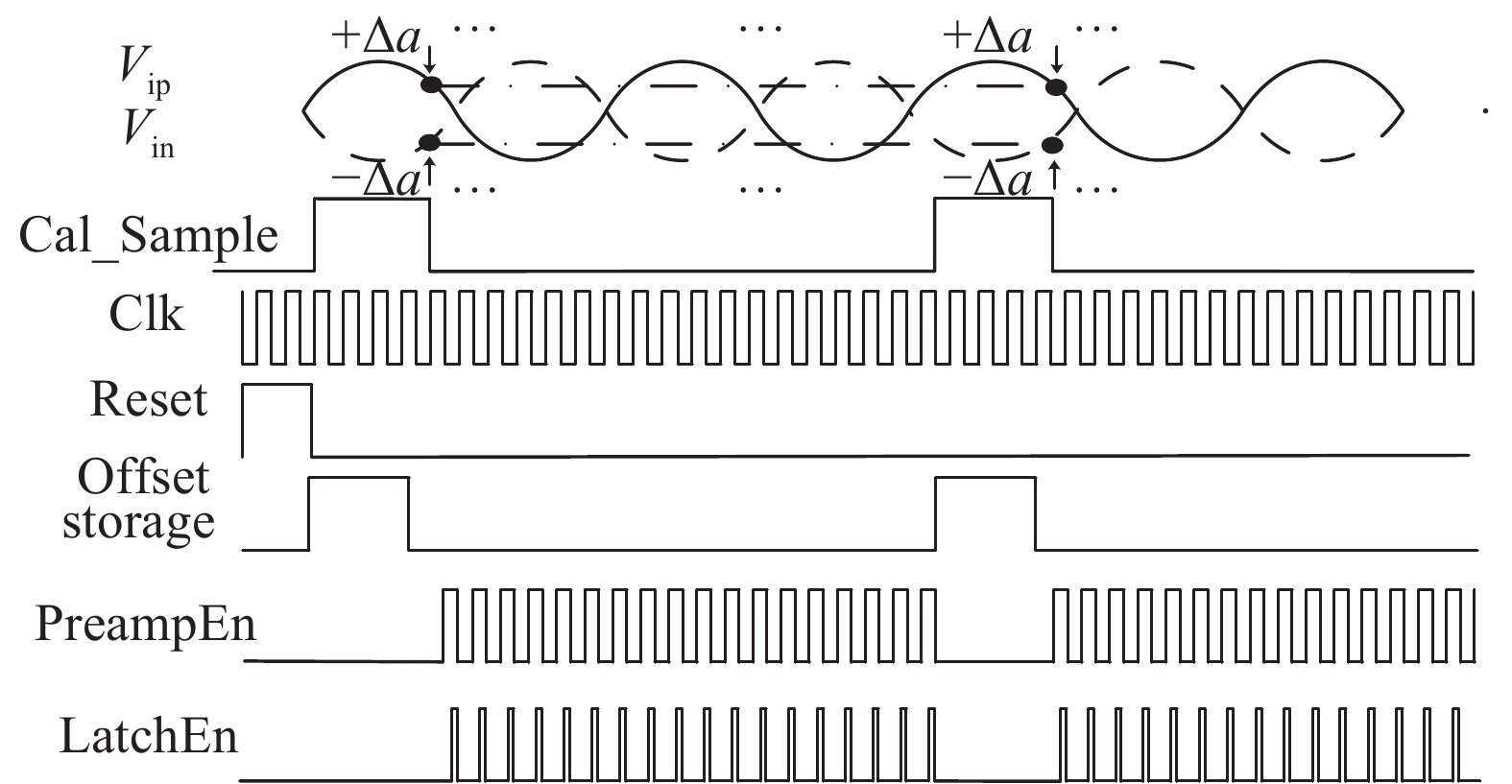

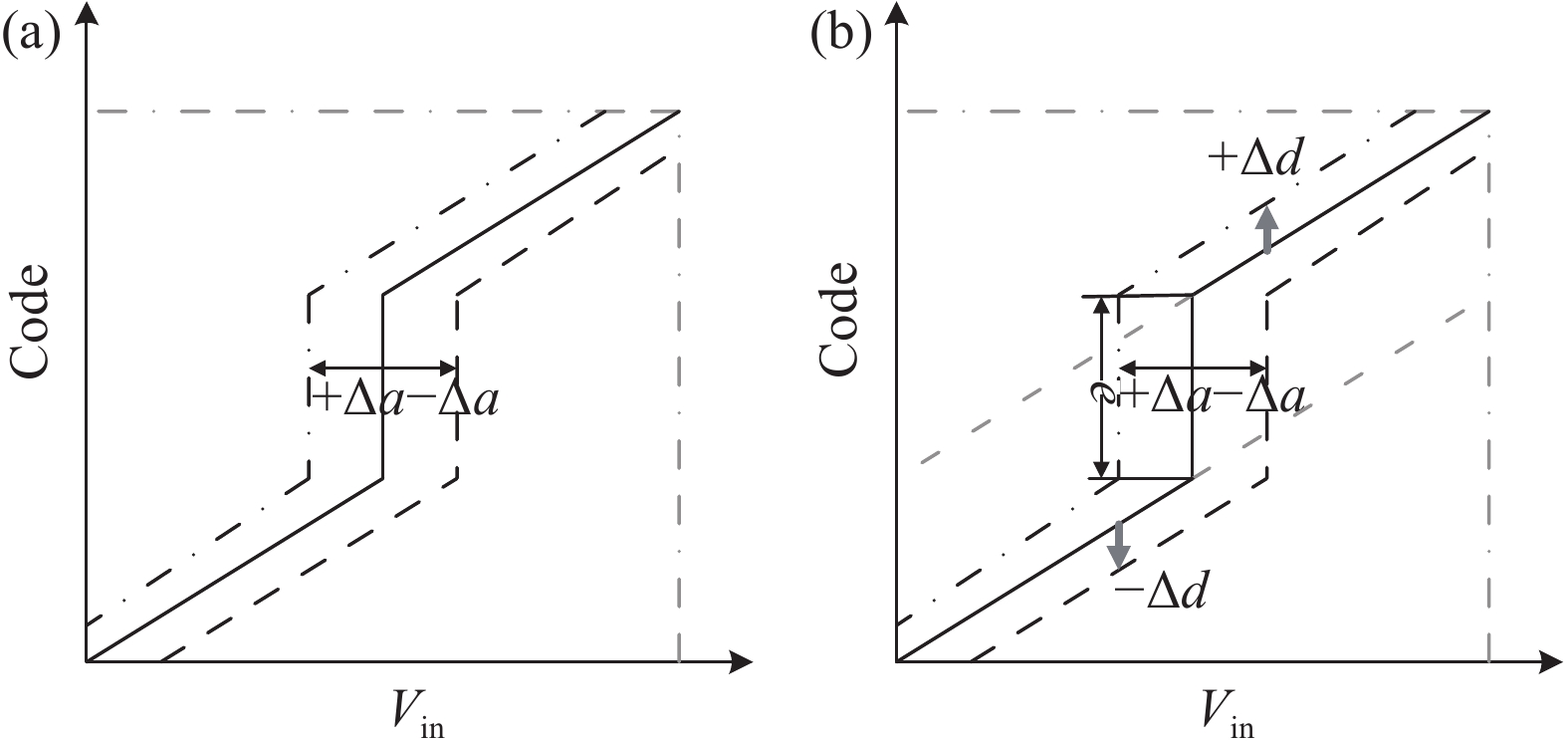

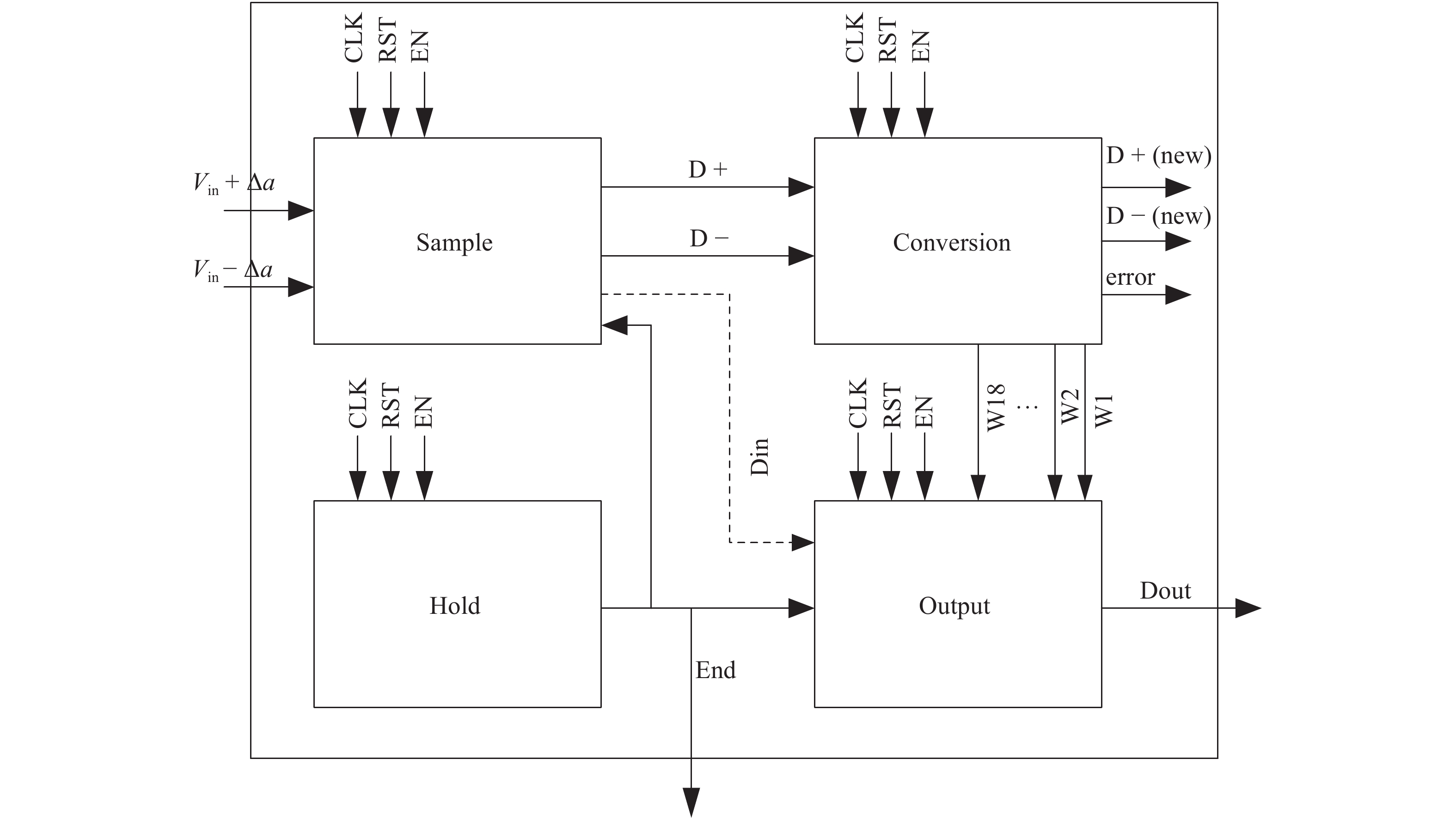

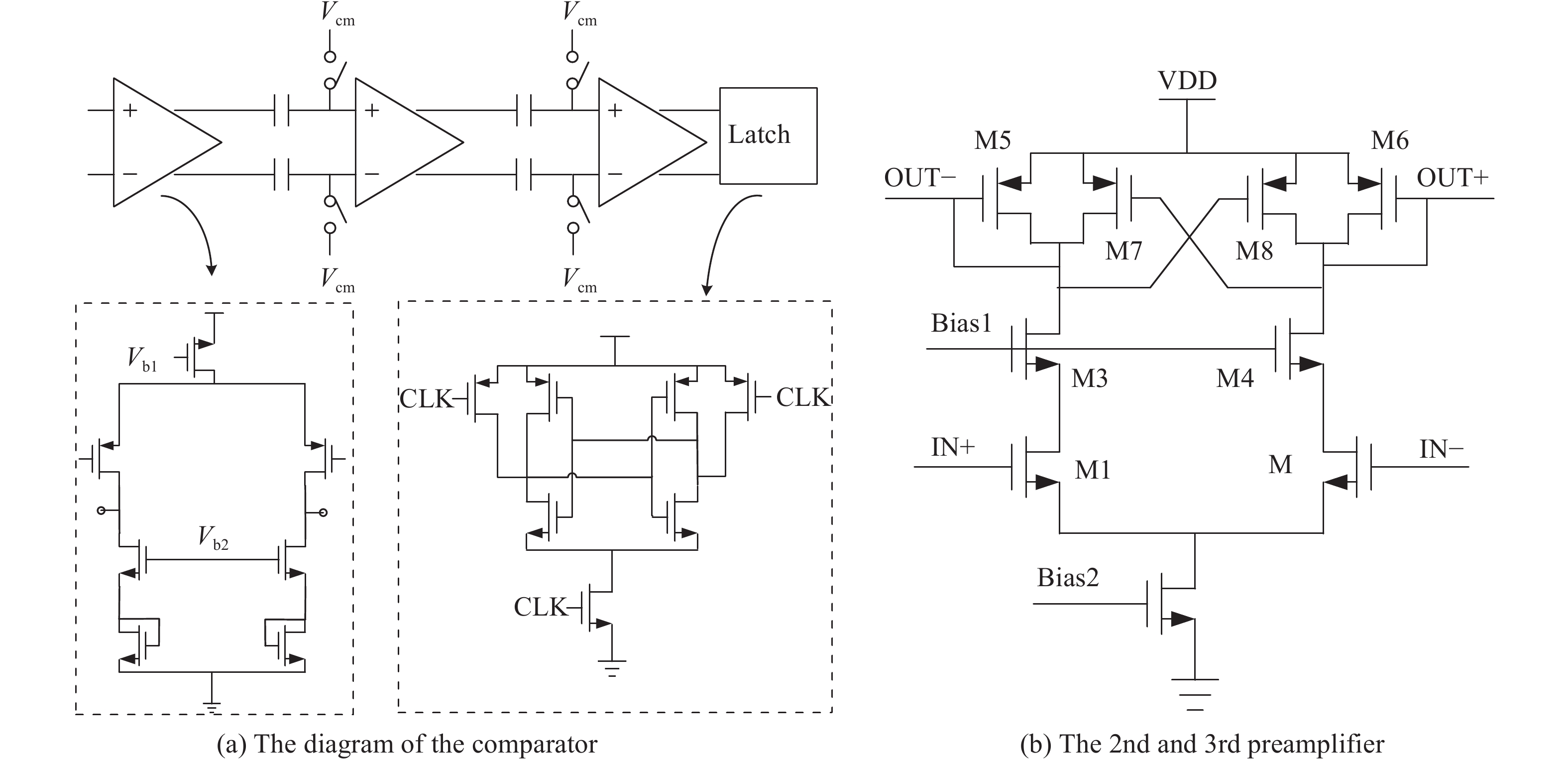

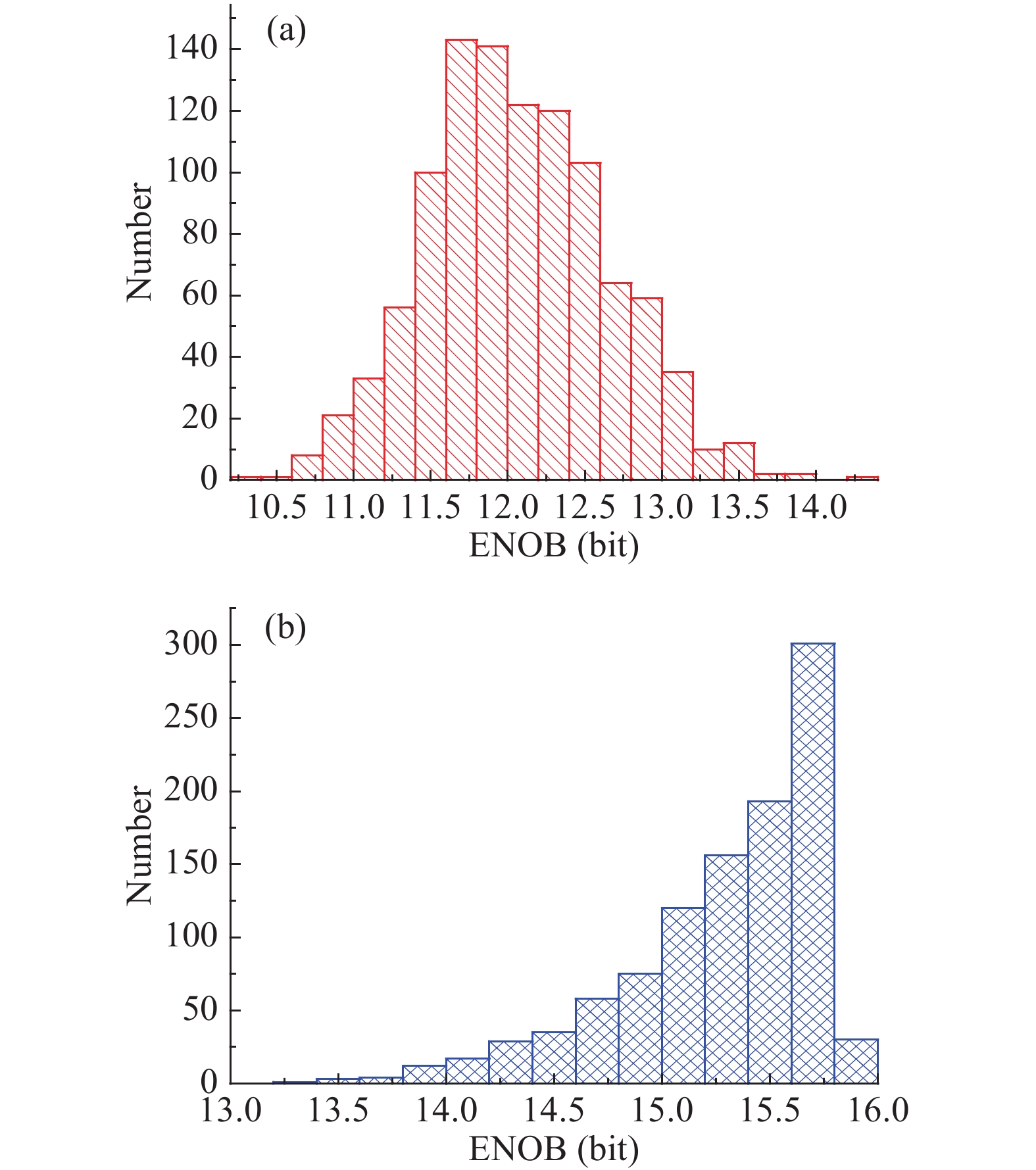

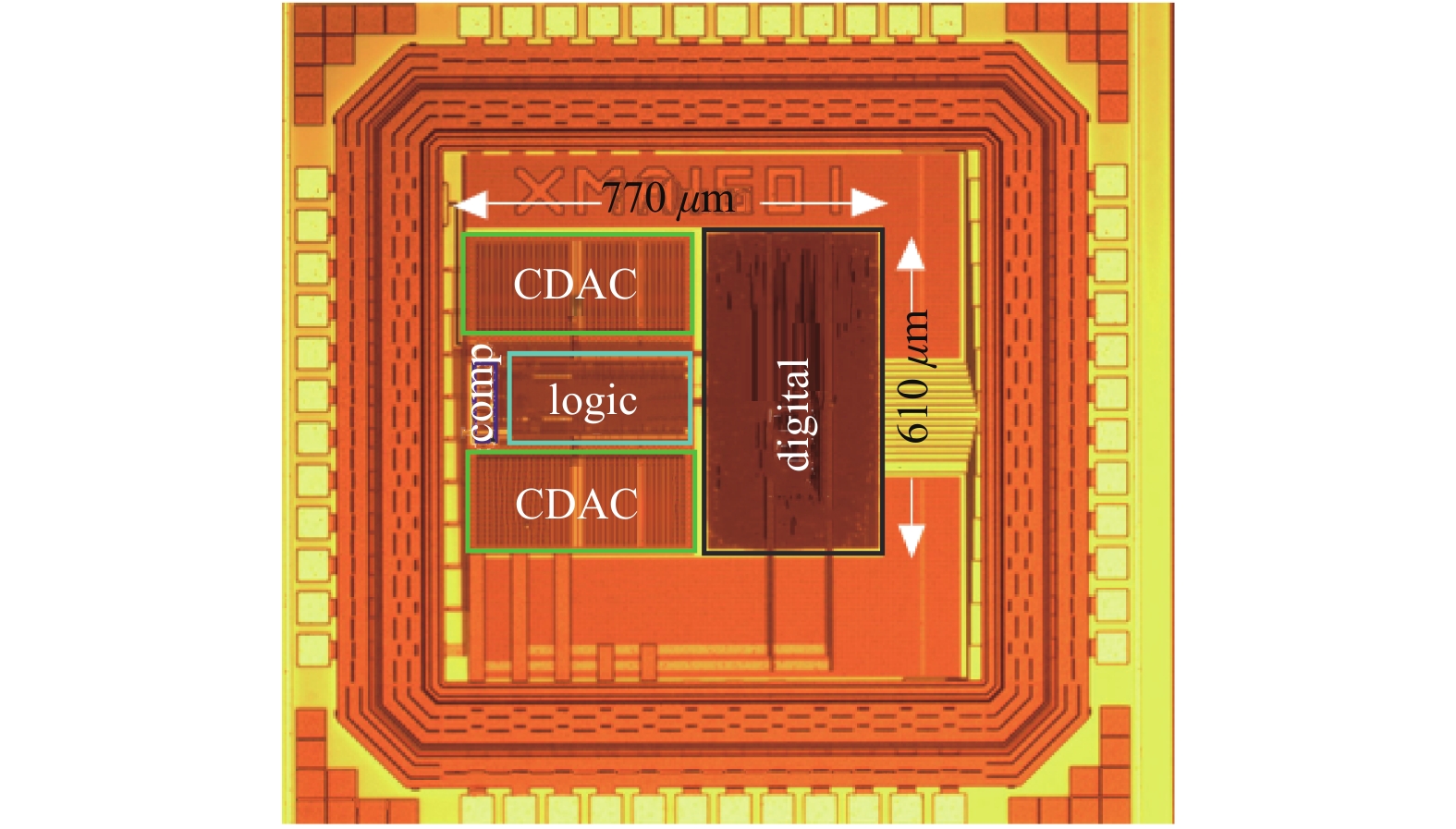

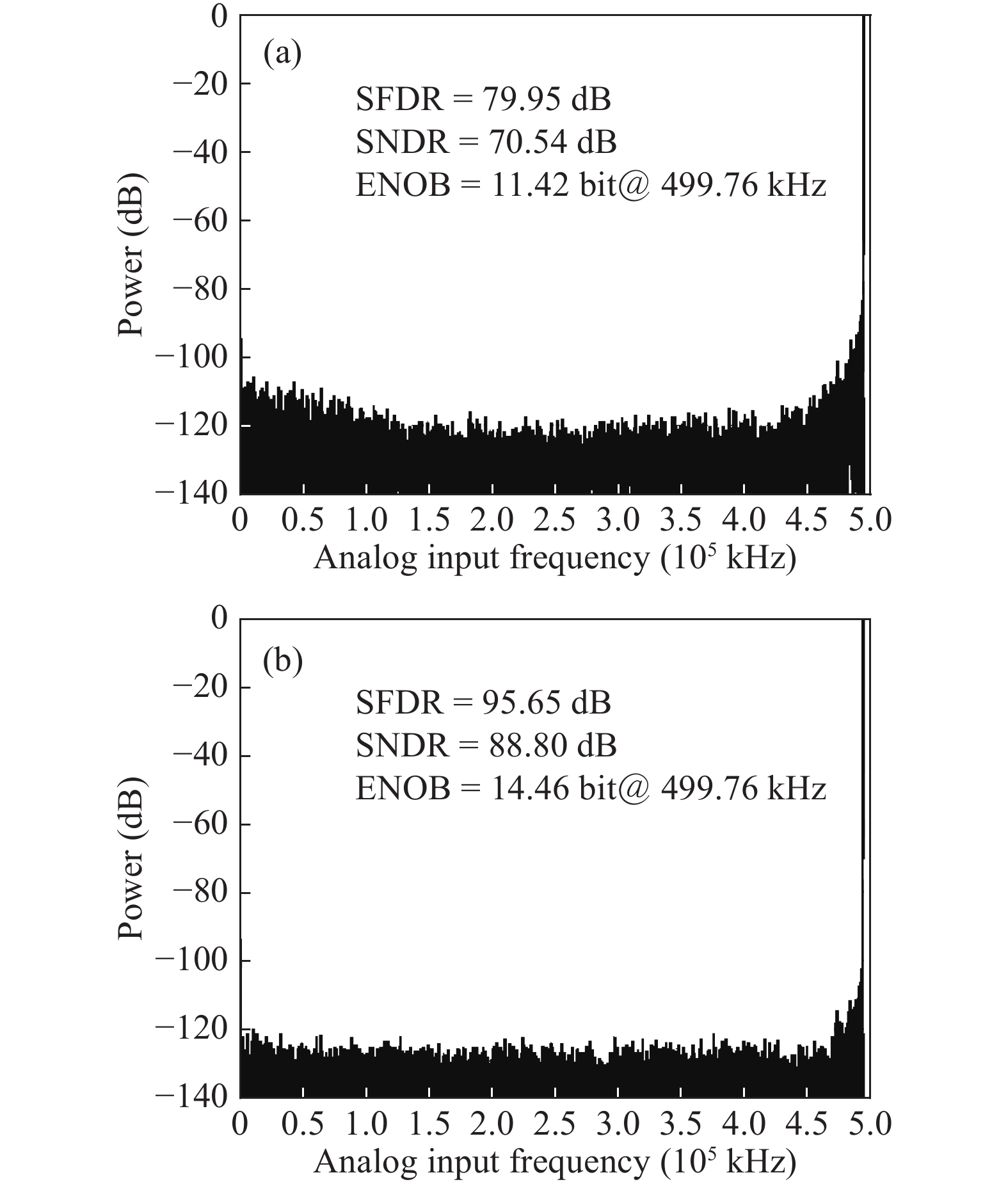

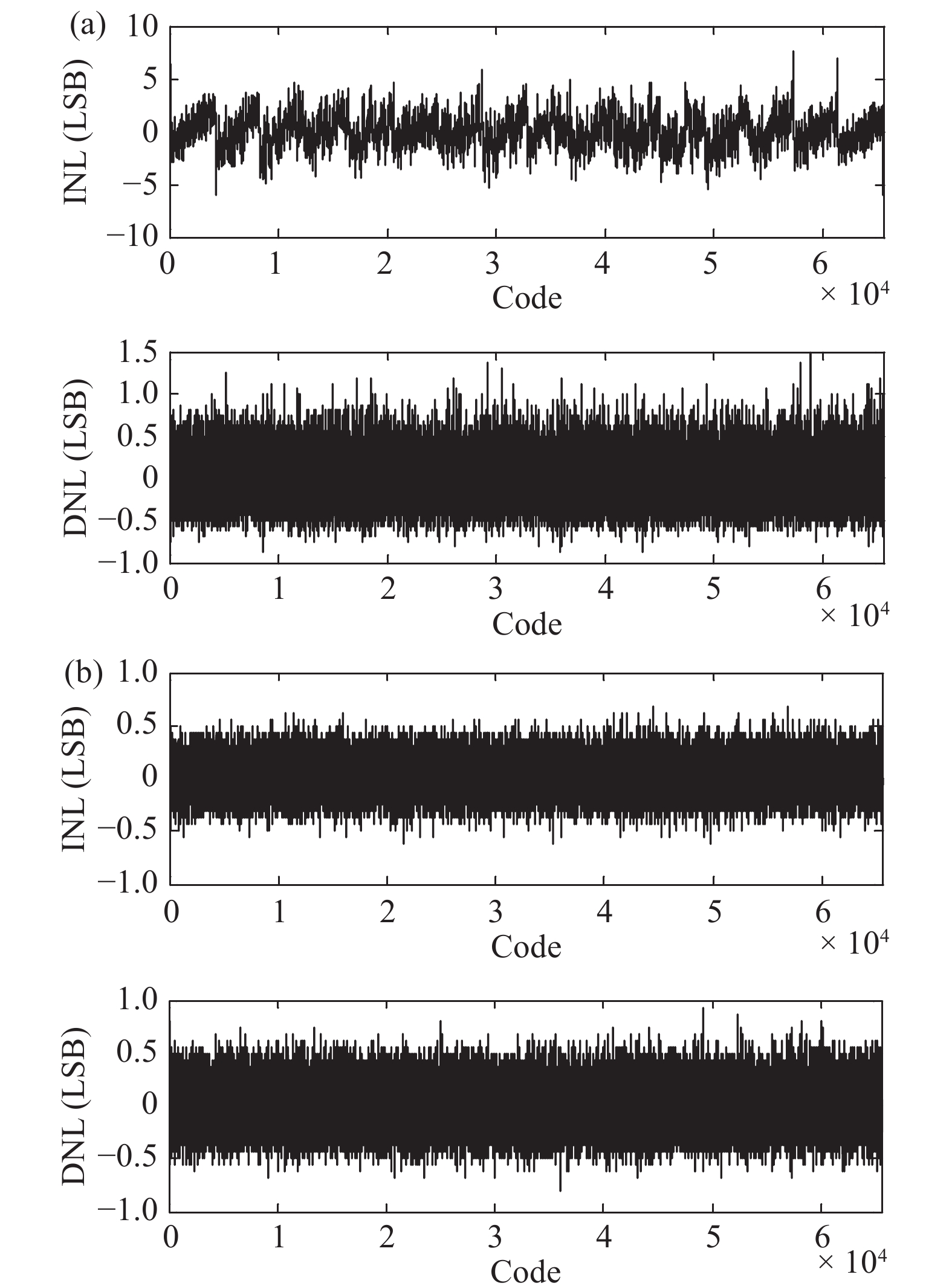

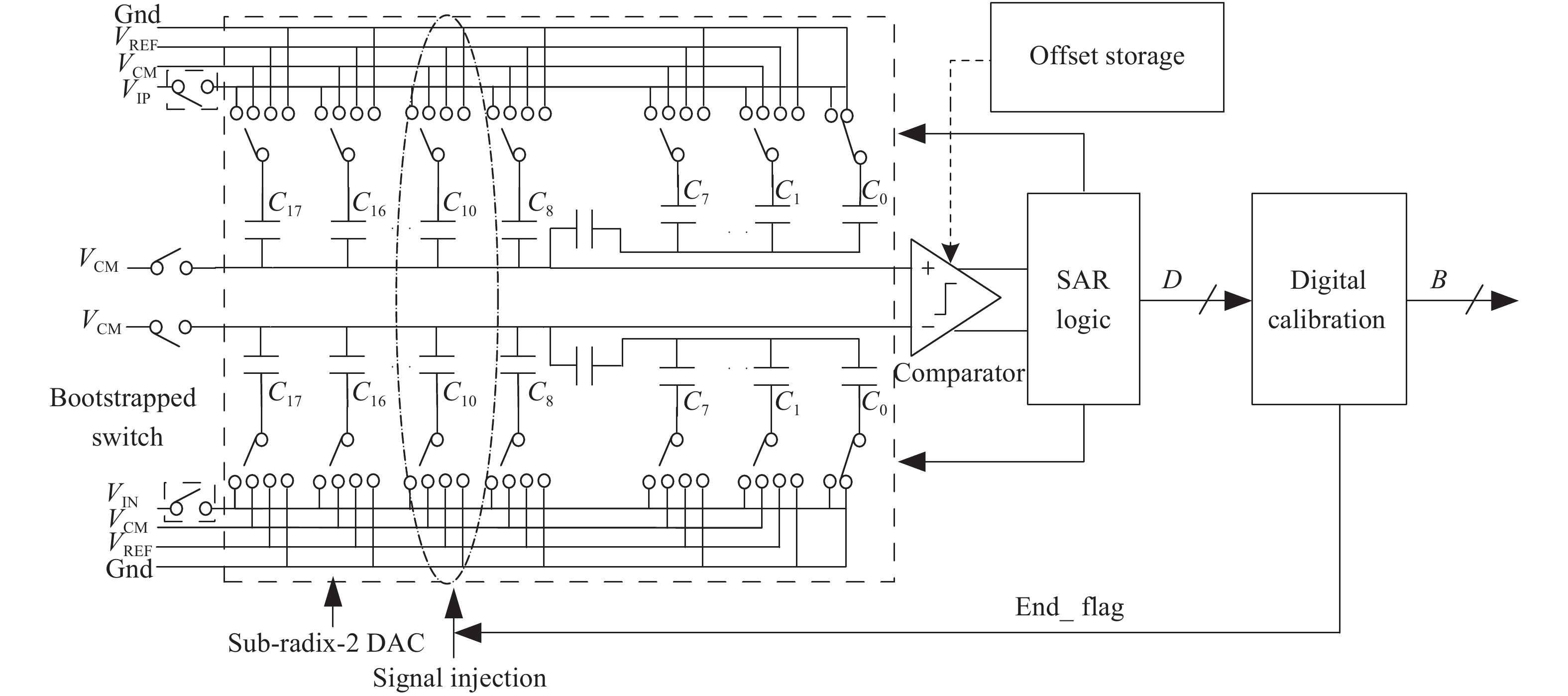

This paper proposes a high-resolution successive-approximation register (SAR) analog-to-digital converter (ADC) with sub-2 radix split-capacitor array architecture. The built-in redundancy of sub-2 radix architecture provides additional information in the digital calibration based on offset double injection. The calibration method is simple in structure and fast in convergence. The correction of errors in each bit is independent of those in the previous bit. A split-capacitor array is used to reduce the total capacitance especially in a high-resolution SAR ADC. An offset signal is injected by the switching scheme of capacitor array to minimize the hardware overhead. The prototype of 0.18 μm CMOS process obtains 14.46 bit ENOB and 95.65 dB SFDR after calibration. With calibration, the INL and DNL are −0.813/0.938 and −0.625/0.688, respectively. -

References

[1] Baker R. CMOS: circuit design, layout, and simulation. Piscataway: IEEE Press, 1998[2] Mcneill J, David C, Coln M, et al. Split ADC background self-calibration of a 16-b successive approximation ADC in 180 nm CMOS. IEEE International Instrumentation and Measurement Technology Conference, 2013: 310 doi: 10.1109/I2MTC.2013.6555430[3] Xu R, Liu B, Yuan J. Digitally calibrated 768-kS/s 10-b minimum-size SAR ADC array with dithering. IEEE J Solid-state Circuits, 2012, 47(9): 2129 doi: 10.1109/JSSC.2012.2198350[4] Chen L, Ma J, Sun N. Capacitor mismatch calibration for SAR ADCs based on comparator metastability detection. IEEE International Symposium on Circuits and Systems, 2014: 2357[5] Zhu Y, Chan C, Wong S, et al. Histogram-based ratio mismatch calibration for bridge-DAC in 12-bit 120 MS/s SAR ADC. IEEE Trans Very Large Scale Integr Syst, 2016, 24(3): 1203 doi: 10.1109/TVLSI.2015.2442258[6] Liu W, Huang P, Chiu Y. A 12-bit, 45-MS/s, 3-mW redundant successive approximation-register analog-to-digital converter with digital calibration. IEEE J Solid-State Circuits, 2011, 46(11): 2661 doi: 10.1109/JSSC.2011.2163556[7] Cao C, Ye Q, Zhu Z, et al. A background digital calibration of split-capacitor 16-bit SAR ADC with radix-2 architecture. Microelectron J, 2015, 46(9): 795 doi: 10.1016/j.mejo.2015.06.013[8] Zhu Y, Chan C, Chio U, et al. Split-SAR ADCs: improved linearity with power and speed optimization. IEEE Trans Very Large Scale Integr Syst, 2014, 22(2): 372 doi: 10.1109/TVLSI.2013.2242501[9] Ogawa T, Kobayashi H, Tan Y, et al. SAR ADC that is configurable to optimize yield. IEEE Asia Pacific Conference on Circuits and Systems, 2010: 374[10] Razavi B, Wooley B. Design techniques for high-speed, high-resolution comparators. IEEE J Solid-State Circuits, 1992, 27(12): 1916 doi: 10.1109/4.173122[11] Wang L, Ren J, Yin W, et al. A high-speed high-resolution low-distortion CMOS bootstrapped switch. IEEE International Symposium on Circuits and Systems, 2007: 721[12] Tille T, Sauerbrey J, Mauthe M, et al. Design of low-voltage MOSFET-only ΣΔ modulators in standard digital CMOS technology. IEEE Trans Circuits Syst I, 2004, 51(1): 96 doi: 10.1109/TCSI.2003.821296[13] Mahmoud A, Nazzal B. Sample and hold circuits for low-frequency signals in analog-to-digital converter. International Conference on Information and Communication Technology Research, 2015: 36[14] Leung Y, Leung K, Holberg D. A dual low power 1/2 LSB NL 16 b/1 Msample/s SAR A/D Converter with on-chip microcontroller. IEEE Asian Solid-State Circuits Conference, 2006: 51[15] Huang X, Zhang J, Gao W, et al. A 16-bit, 250 ksps successive approximation register ADC based on the charge-redistribution technique. International Conference of Electron Devices and Solid-State Circuits, 2011: 1[16] Chi Y, Li D, Wang Z. A 16-bit 1 MS/s 44 mW successive approximation registers analog-to-digital converter achieving signal-to-noise-and-distortion-ratio of 94.3 dB. IEEE International Conference of Electron Devices and Solid-State Circuits, 2013: 1[17] Wang G, Foti K, Yun C. IRD digital background calibration of SAR ADC with coarse reference ADC acceleration. IEEE Trans Circuits Syst II, 2014, 61(1): 11 doi: 10.1109/TCSII.2013.2291051 -

Proportional views

DownLoad:

DownLoad: