| Citation: |

Yang Min, Nan Qi, Yihan Chen, Minye Zhu, Guike Li, Yonghui Lin, Zhao Zhang, Jian Liu, Nanjian Wu, Jingbo Shi, Frank F. Shi, Liyuan Liu. A 32Gb/s digital-assisted PAM-4 DFB laser driver in 28-nm CMOS[J]. Journal of Semiconductors, 2025, 46(10): 102202. doi: 10.1088/1674-4926/25020011

****

Y Min, N Qi, Y H Chen, M Y Zhu, G K Li, Y H Lin, Z Zhang, J Liu, N J Wu, J B Shi, F F Shi, and L Y Liu, A 32Gb/s digital-assisted PAM-4 DFB laser driver in 28-nm CMOS[J]. J. Semicond., 2025, 46(10), 102202 doi: 10.1088/1674-4926/25020011

|

A 32Gb/s digital-assisted PAM-4 DFB laser driver in 28-nm CMOS

DOI: 10.1088/1674-4926/25020011

CSTR: 32376.14.1674-4926.25020011

More Information-

Abstract

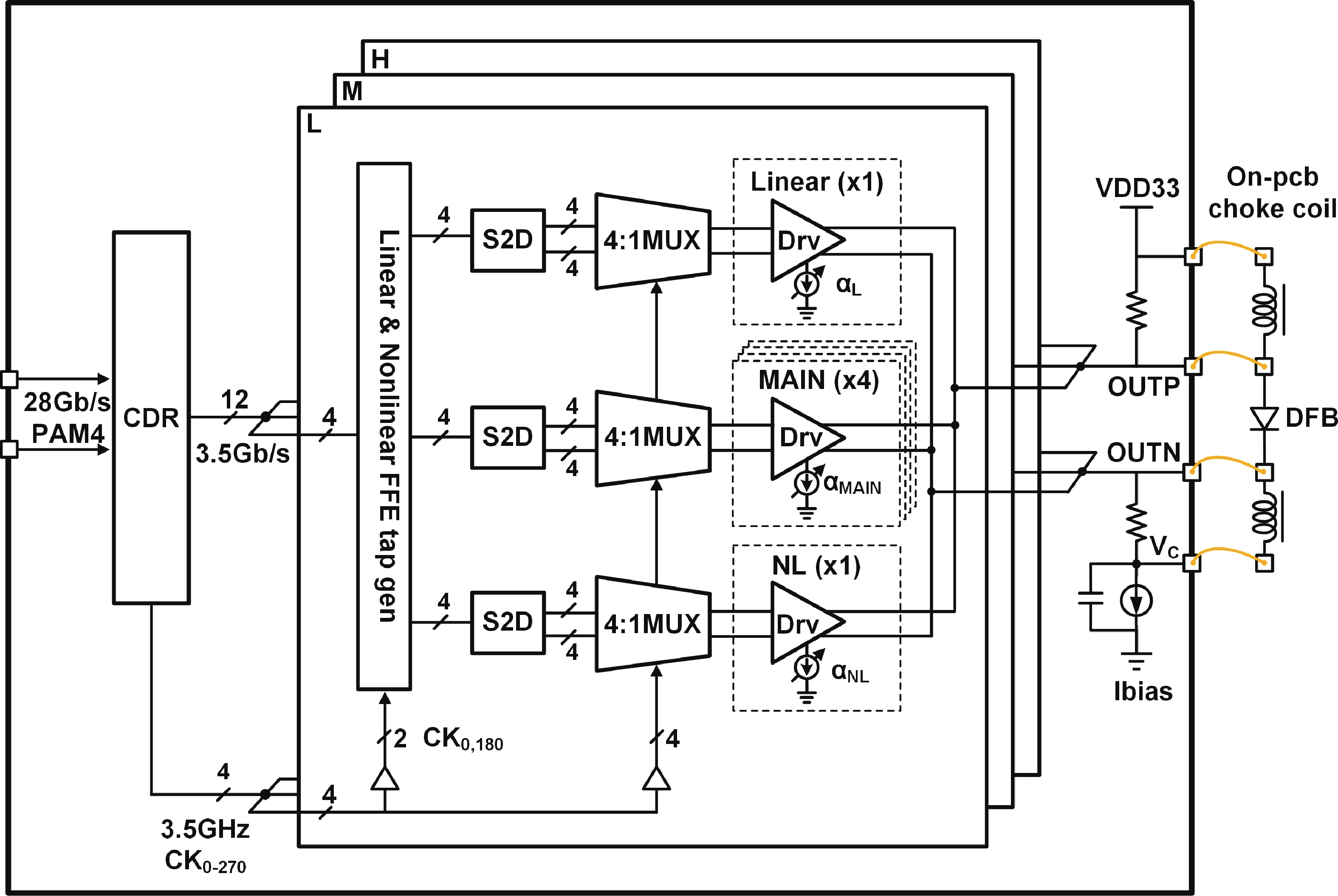

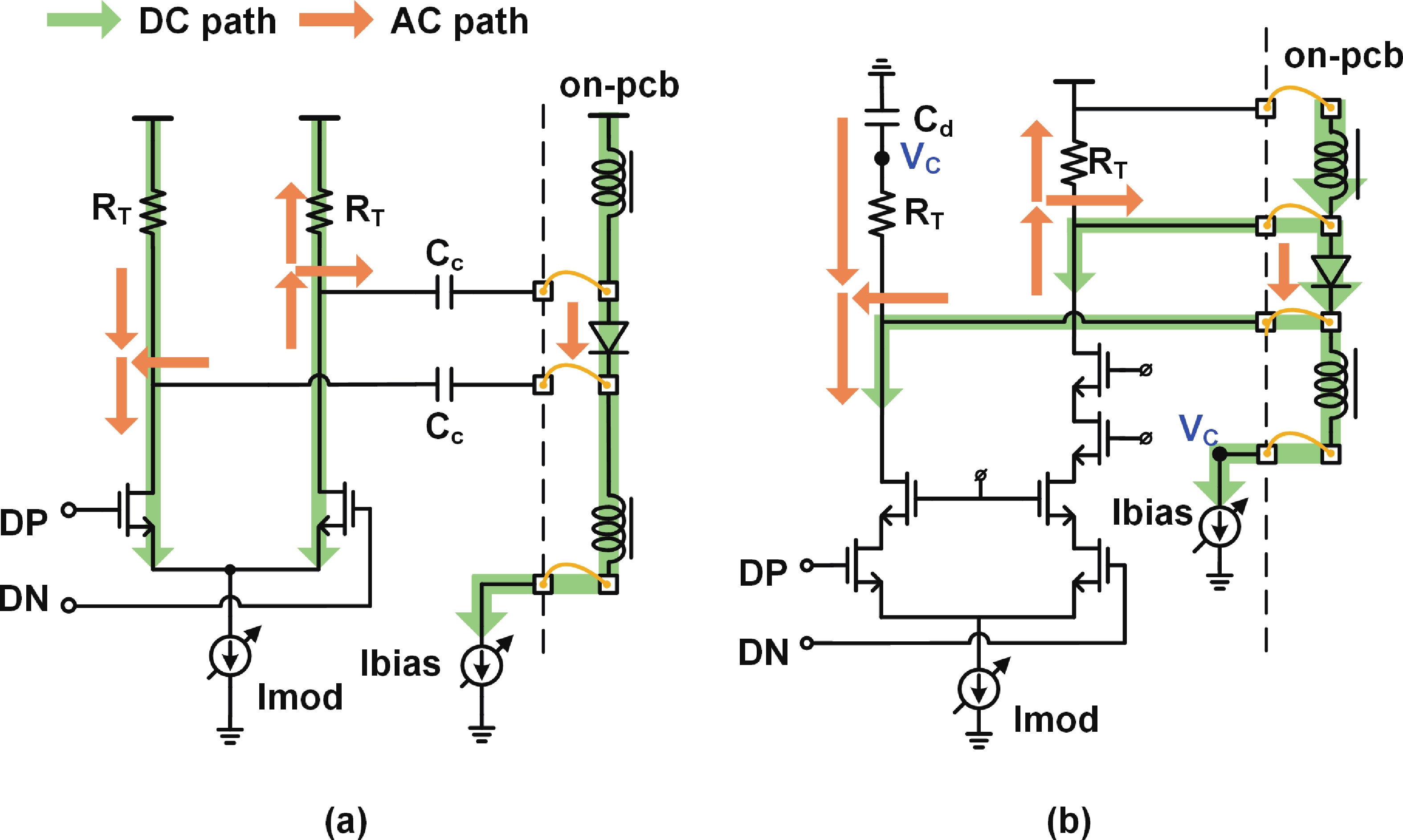

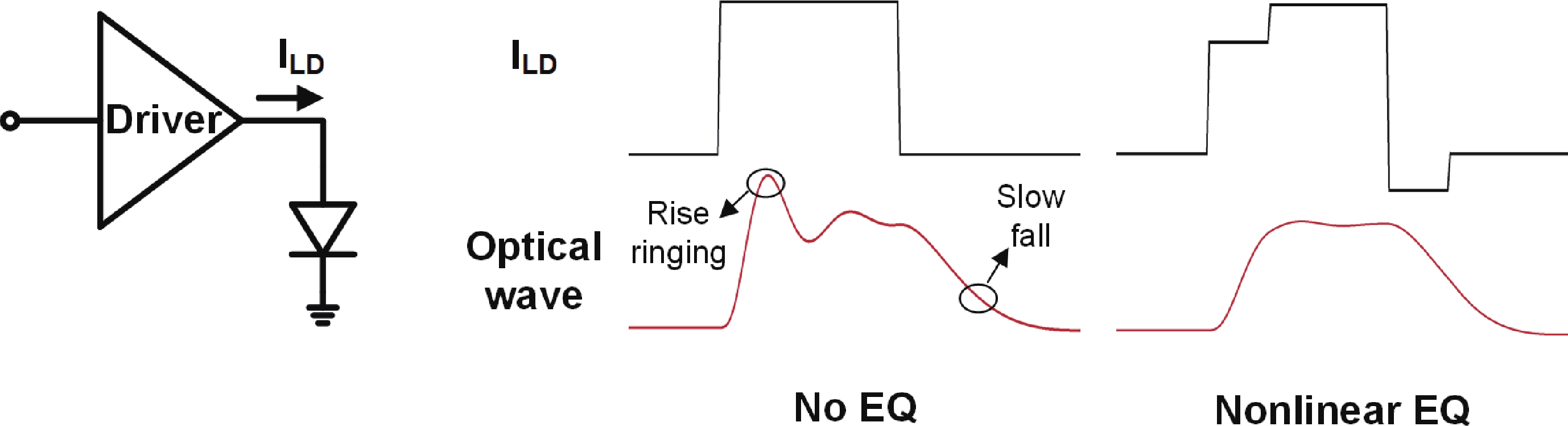

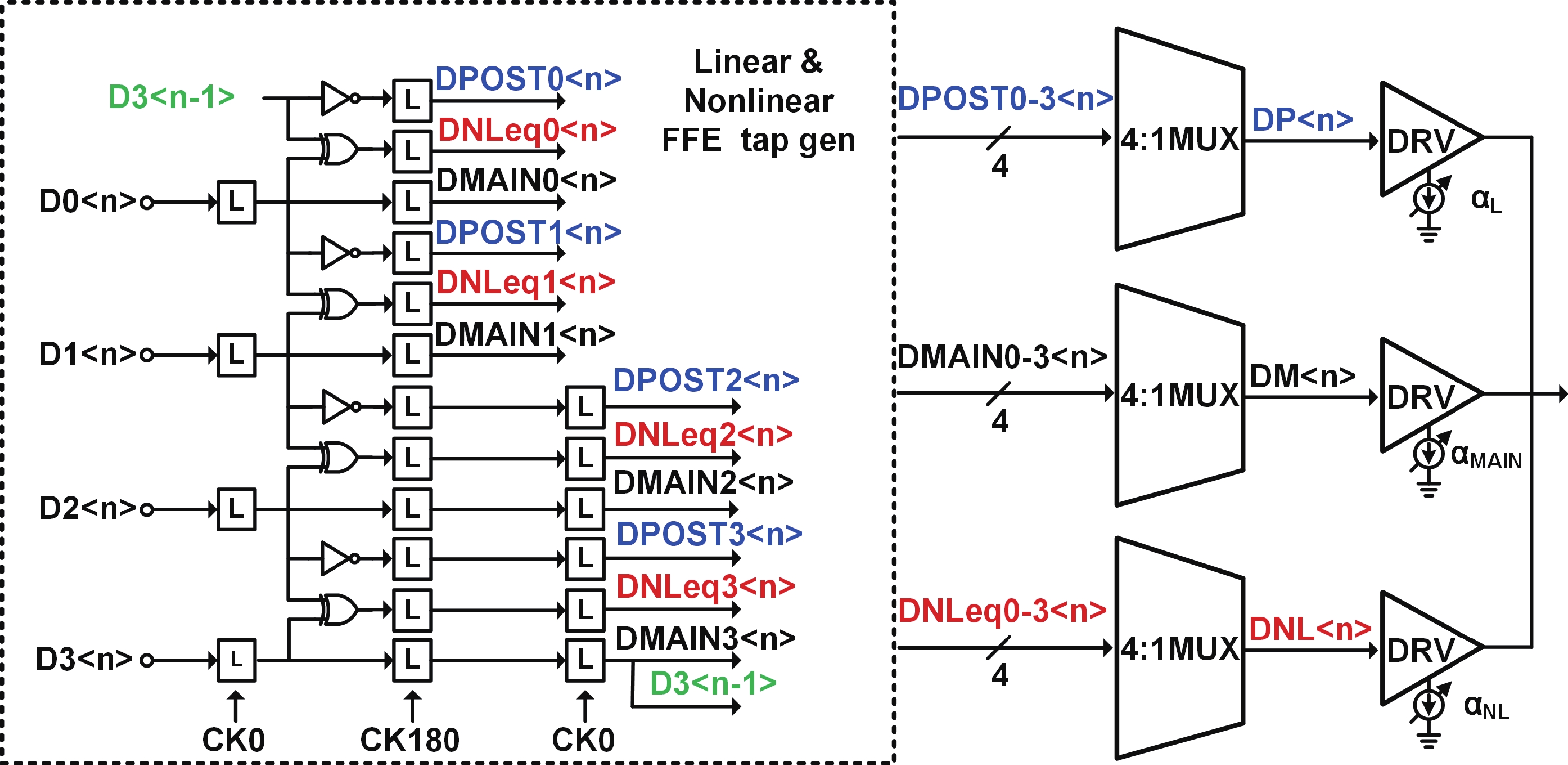

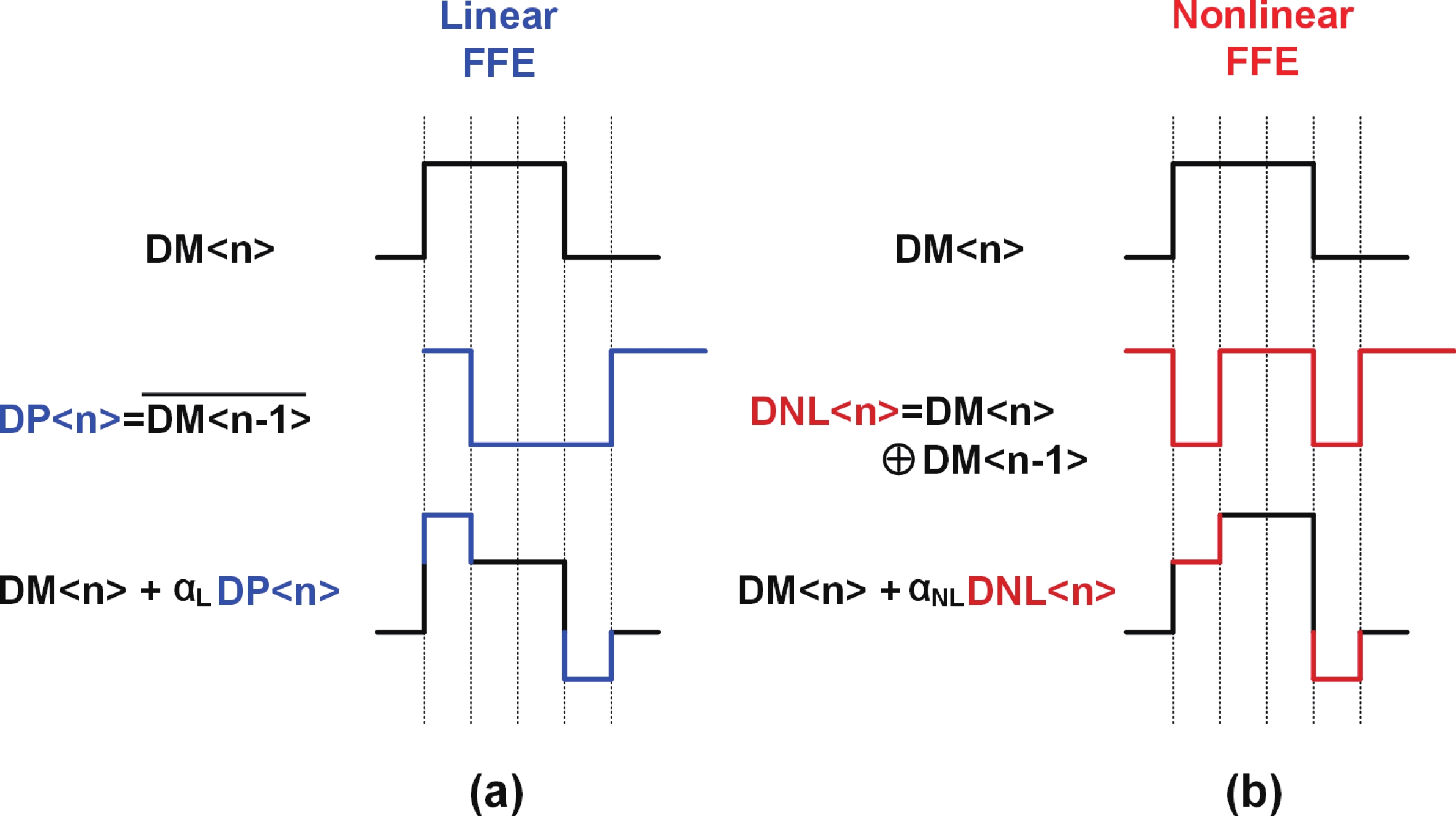

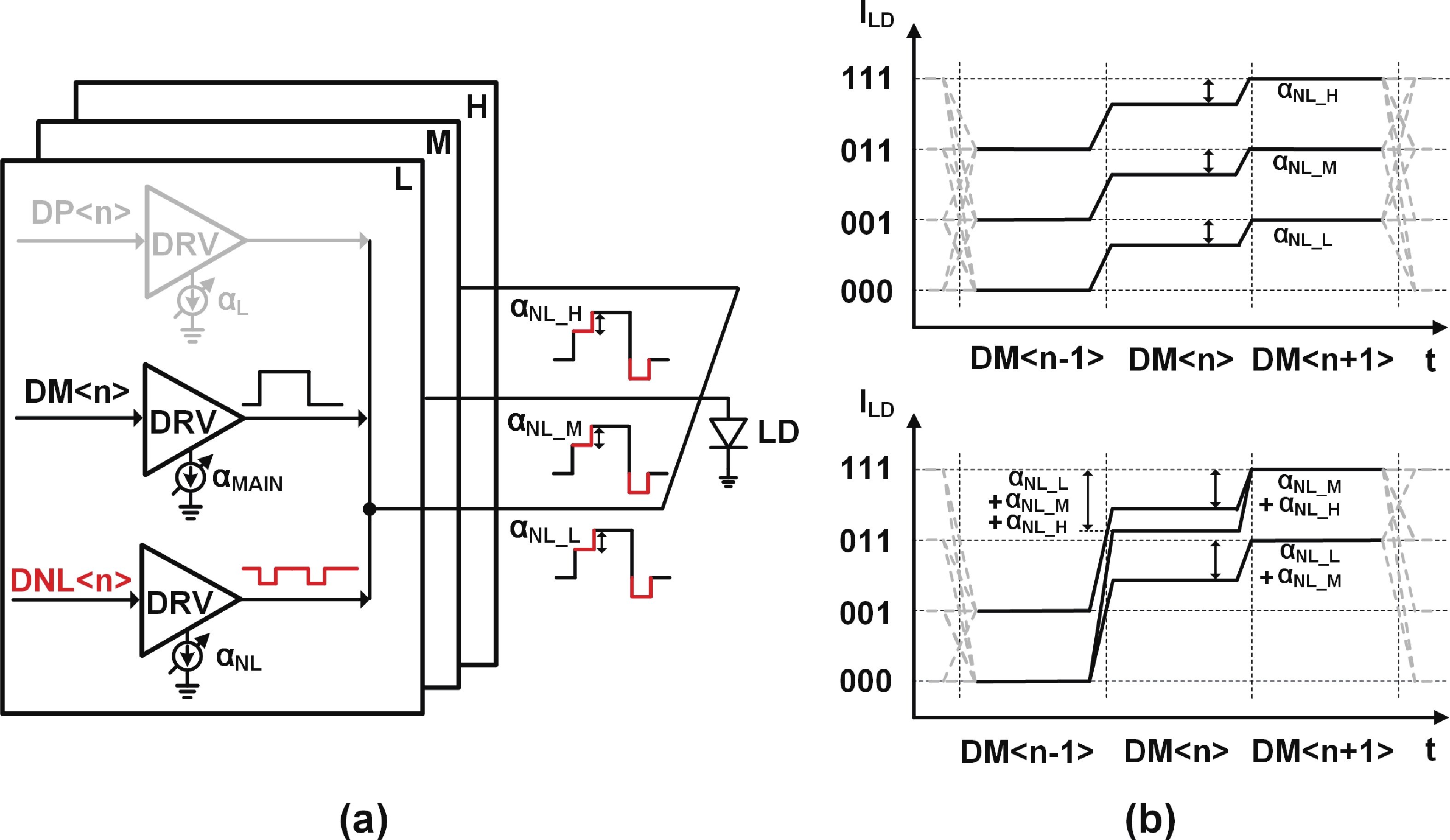

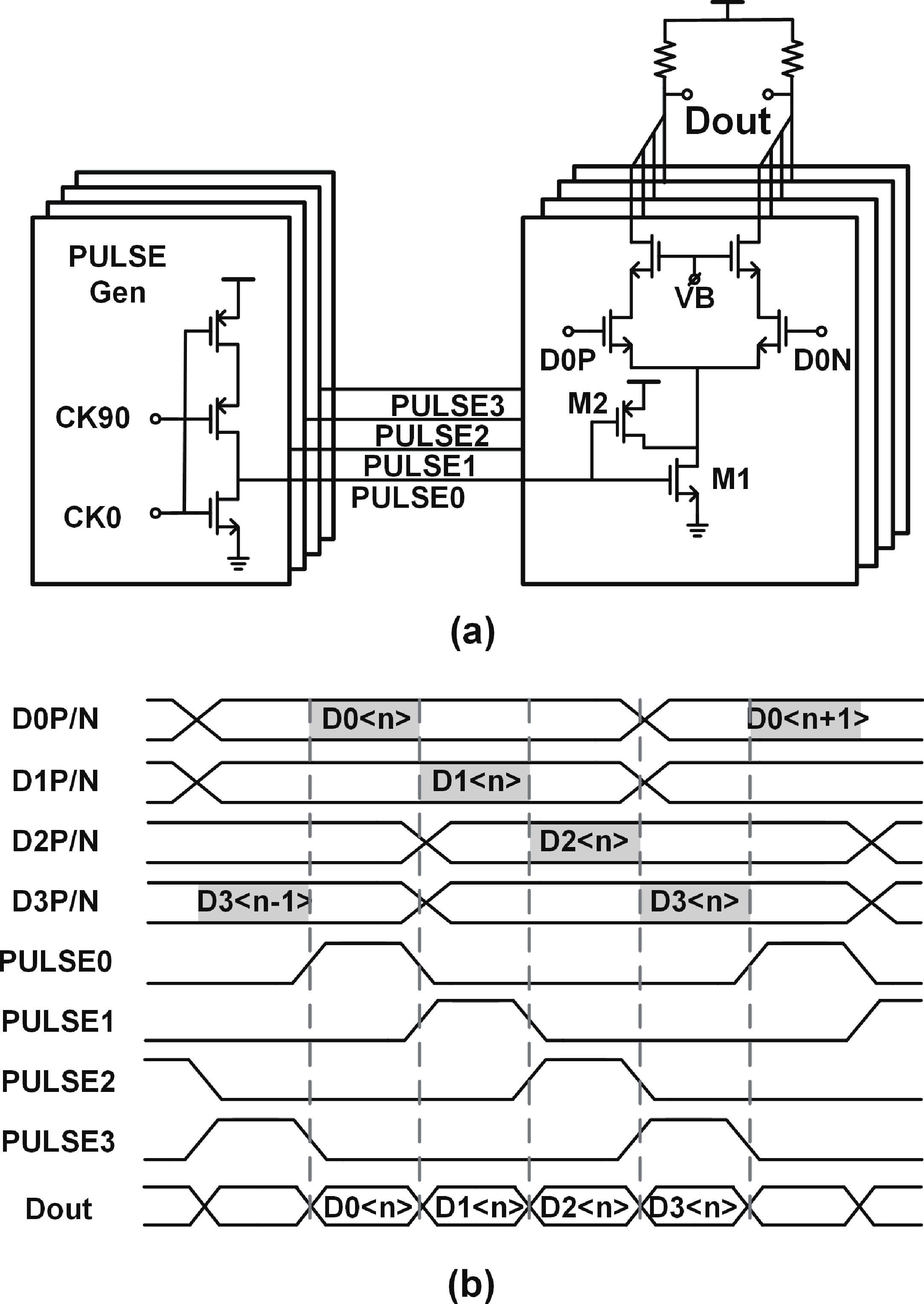

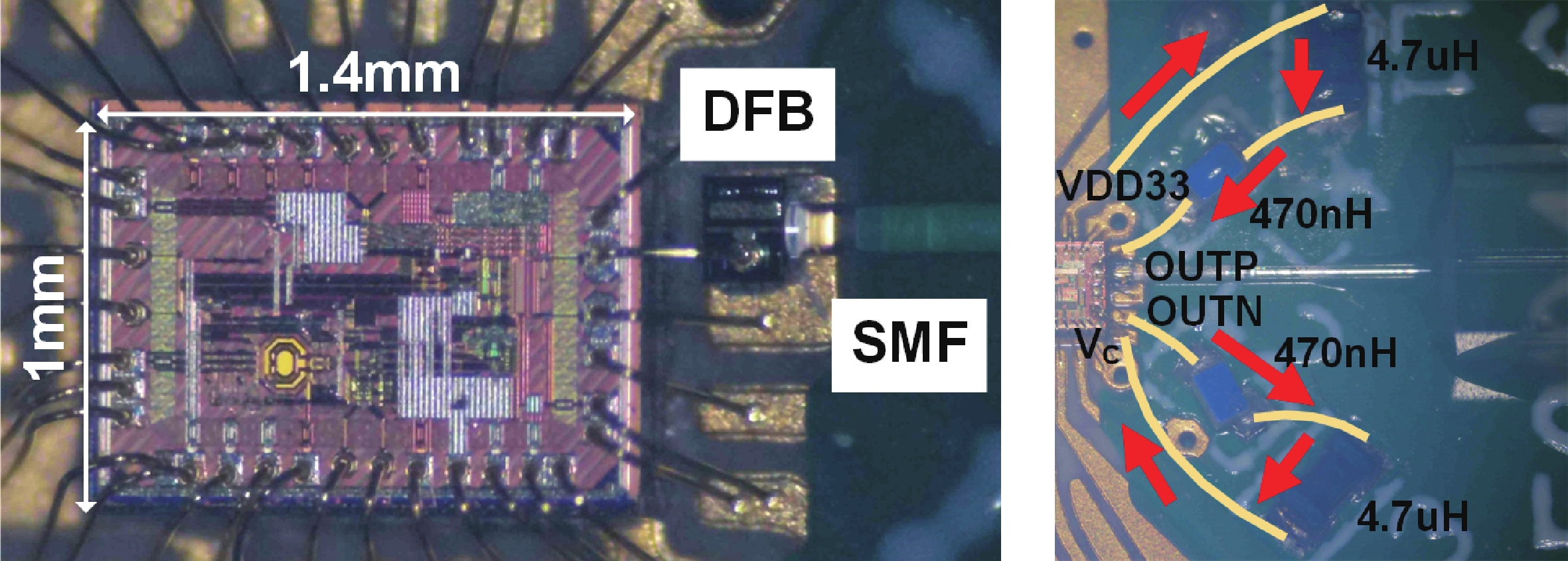

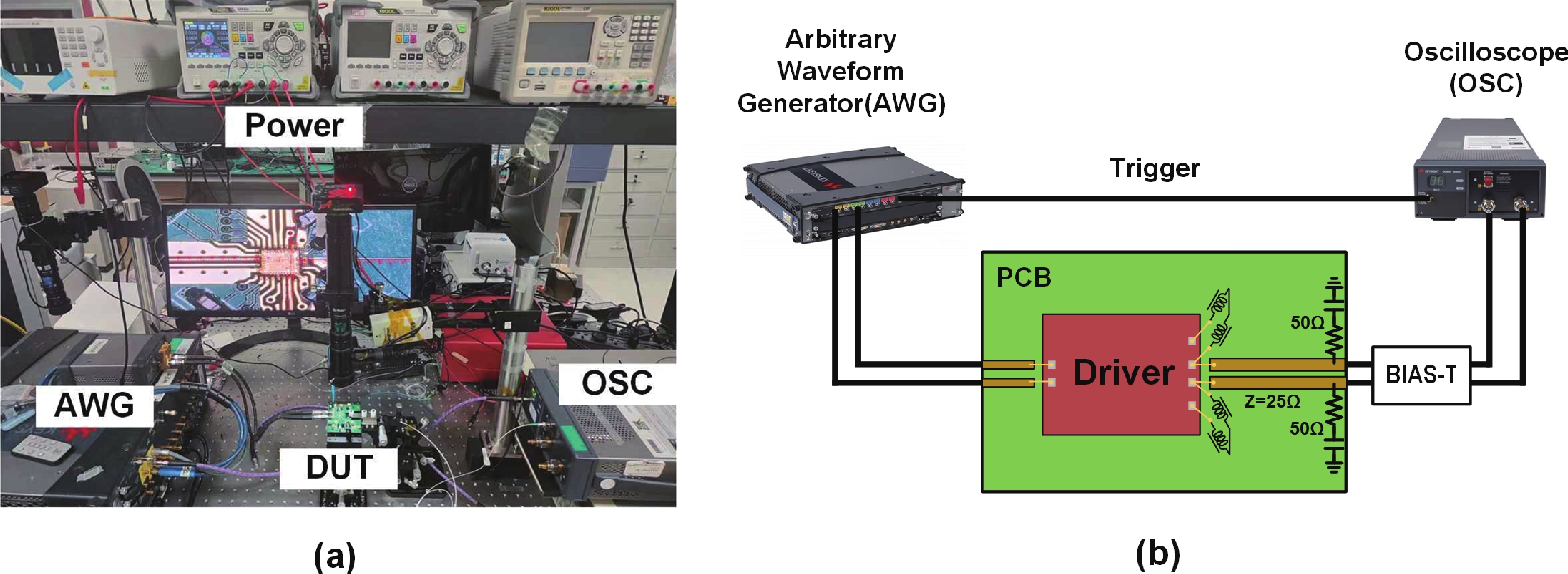

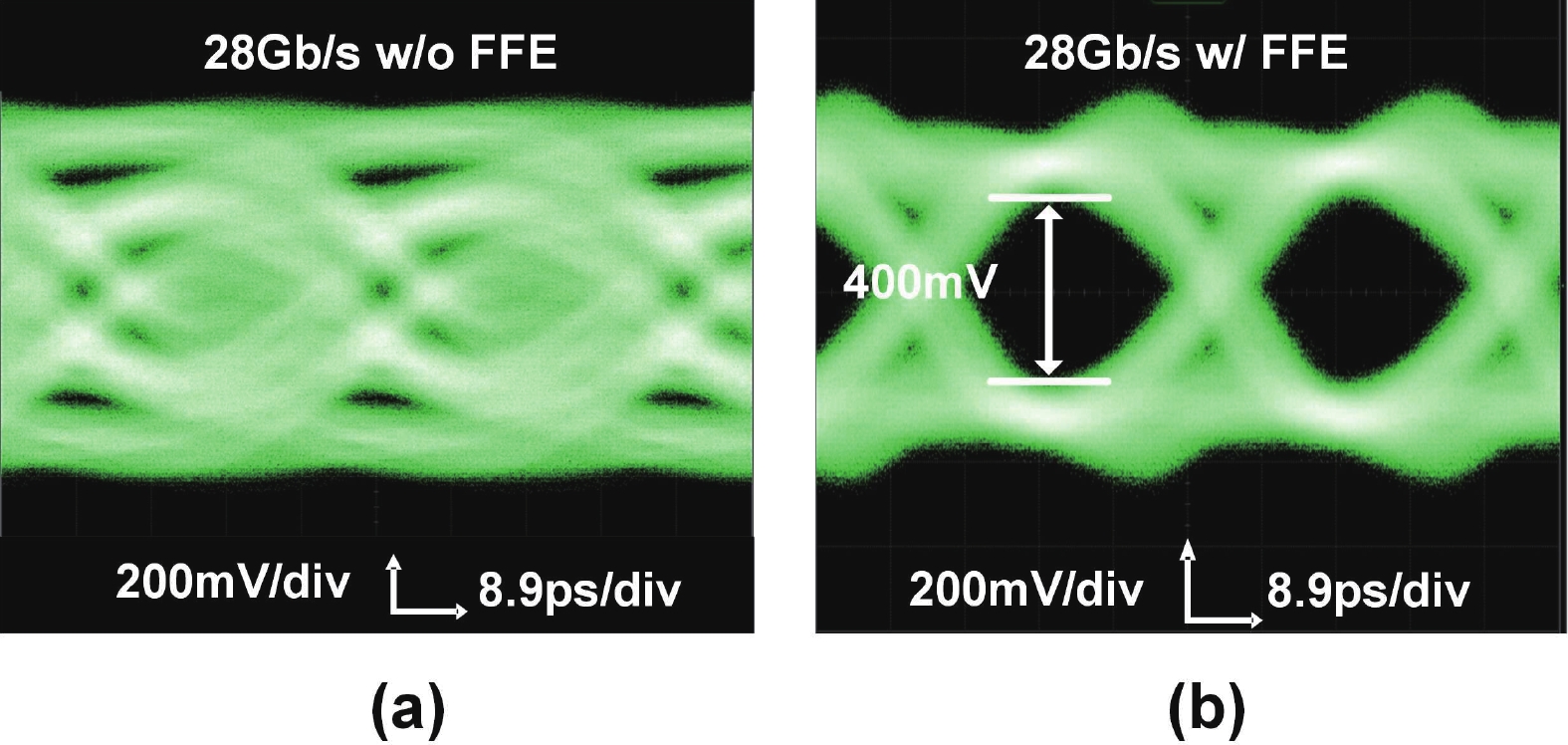

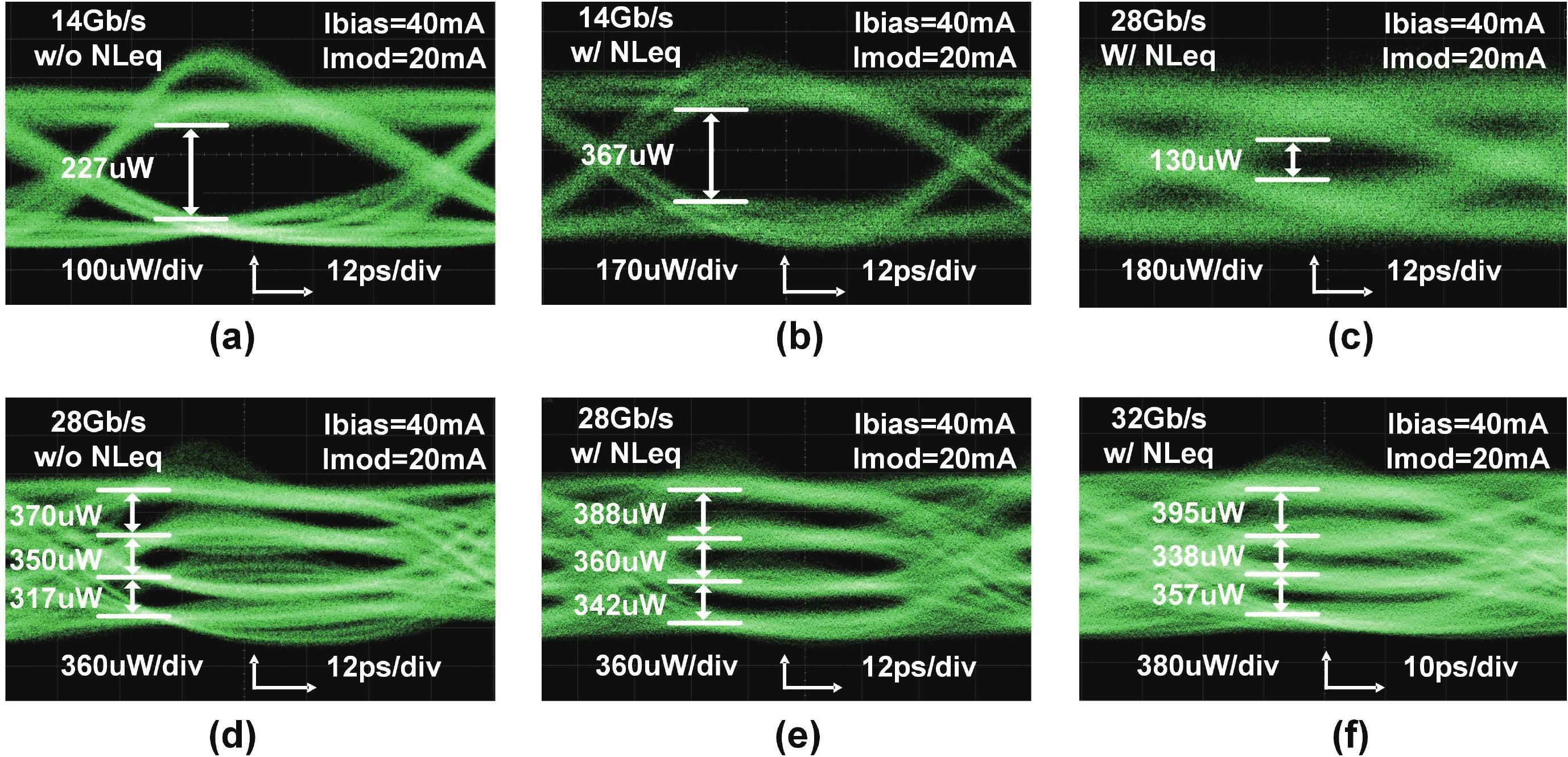

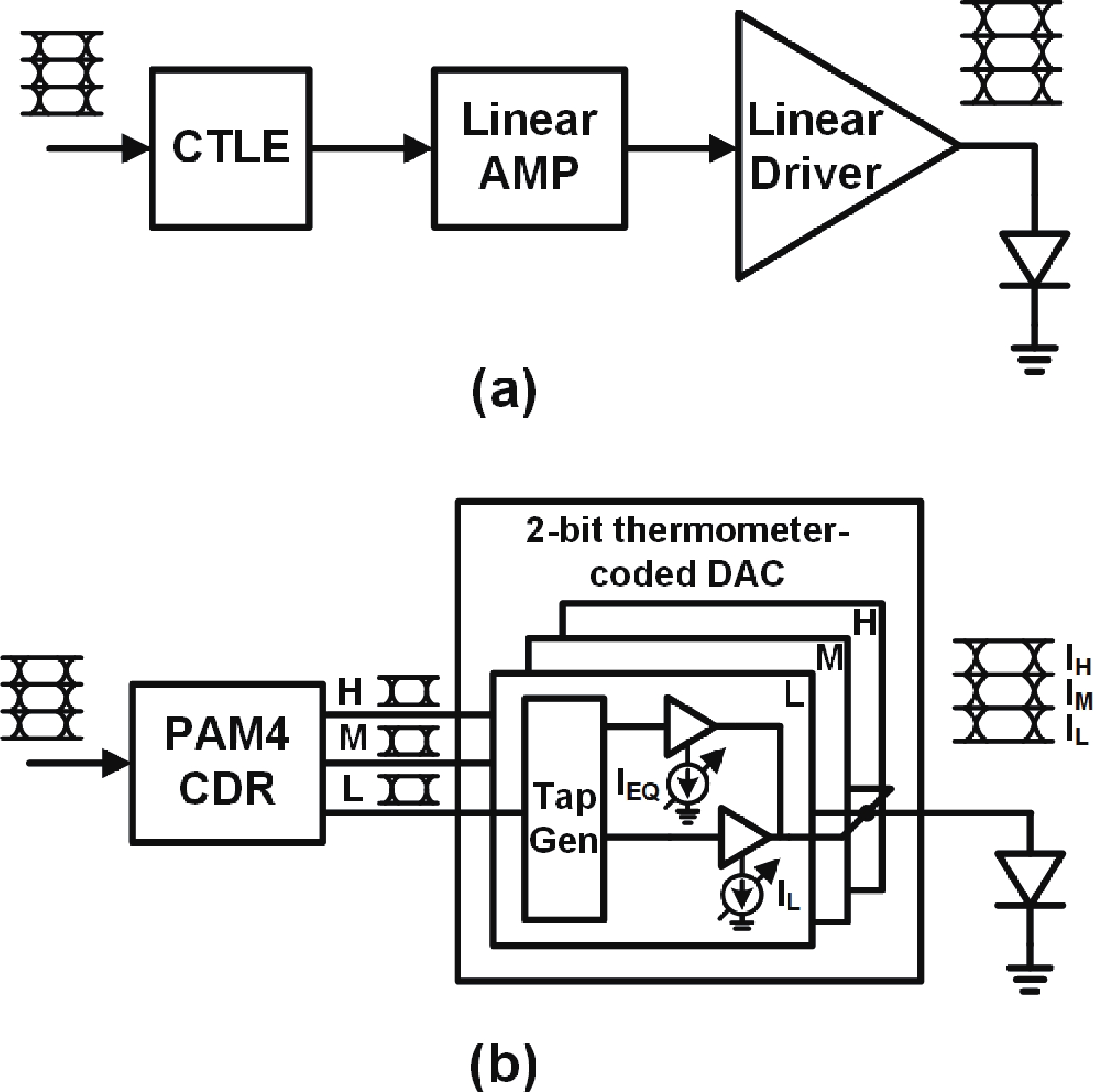

This paper presents a 4-level pulse amplitude modulation (PAM-4) distributed feedback (DFB) laser driver. The driver adopts a digital slicing architecture to achieve high linearity by adjusting the weights of three thermometer-coded main paths. An efficient-biased output stage structure is proposed to reduce power consumption while avoiding the degradation of output node bandwidth typically induced by parasitic capacitance in high-current bias path. A two-tap linear and nonlinear feed-forward equalizer (FFE) is implemented in the digital domain to extend bandwidth limitations and compensate for the dynamic nonlinearity of the DFB laser. The nonlinear FFE is realized at the cost of lower power consumption and smaller area by utilizing the simultaneity of low-speed parallel data. The chip is fabricated in 28 nm CMOS process. Measurement results indicate that, with a laser bias current of 40 mA, a modulation current of 20 mApp, and an operating rate of 32 Gb/s PAM-4, the overall power consumption of the chip is 372 mW, corresponding to an energy efficiency of 11.6 pJ/b. -

References

[1] Cheng Q X, Glick M, Bergman K. Optical interconnection networks for high-performance systems. Optical Fiber Telecommunications VII. Amsterdam: Elsevier, 2020, 785 doi: 10.1109/JLT.2011.2172989[2] Pitwon R, Reddy A, Jain A, et al. Evolution of system embedded optical interconnect in sub-top-of-rack data center systems. Appl Sci, 2022, 12(3), 1565 doi: 10.3390/app12031565[3] Chen G Y, Yu Y, Shi Y, et al. High-speed photodetectors on silicon photonics platform for optical interconnect. Laser & Photonics Rev, 2022, 16(12), 2200117 doi: 10.1002/lpor.202200117[4] Akulova Y, Fathololoumi S, Nguyen K, et al. Silicon photonics integrated circuit for co-packaged optical-IO. 2022 Conference on Lasers and Electro-Optics Pacific Rim (CLEO-PR), 2022, 1 doi: 10.1109/CLEO-PR62338.2022.10432157[5] Takemoto T, Matsuoka Y, Sugiyama Y, et al. A 50-Gb/s NRZ-modulated optical transmitter based on a DFB-LD and a 0.18-µm SiGe BiCMOS LD driver. 2015 Optical Fiber Communications Conference and Exhibition (OFC), 2015, 1[6] Wahba A, Cheng L, Lin F J. A 15 Gbps-NRZ, 30 Gbps-PAM4, 120 mA laser diode driver implemented in 0.15-µm GaAs E-mode pHEMT technology. J Semicond, 2021, 42(7), 072401 doi: 10.1088/1674-4926/42/7/072401[7] Chujo N, Takai T, Sugawara T, et al. A 25 Gb/s 65-nm CMOS low-power laser diode driver with mutually coupled peaking inductors for optical interconnects. IEEE Trans Circuits Syst I Regul Pap, 2011, 58(9), 2061 doi: 10.1109/TCSI.2011.2163982[8] Yin B Z, Qi N, Shi J B, et al. A 32Gb/s-NRZ, 15GBaud/s-PAM4 DFB laser driver with active back-termination in 65nm CMOS. 2017 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), 2017, 264 doi: 10.1109/RFIC.2017.7969068[9] Liu X W, Zhang Y H, Zhou C J, et al. A 16Gb/s triple-mode driver in 0.18μm CMOS technology. 2020 IEEE International Conference on Integrated Circuits, Technologies and Applications (ICTA), 2020, 96 doi: 10.1109/ICTA50426.2020.9332001[10] Belfiore G, Khafaji M, Henker R, et al. A compact electro-optical VCSEL model for high-speed IC design. 2016 12th Conference on Ph. D. Research in Microelectronics and Electronics (PRIME), 2016, 1 doi: 10.1109/PRIME.2016.7519508[11] Raj M, Monge M, Emami A. A modelling and nonlinear equalization technique for a 20 Gb/s 0.77 pJ/b VCSEL transmitter in 32 nm SOI CMOS. IEEE J Solid State Circuits, 2016, 51(8), 1734 doi: 10.1109/JSSC.2016.2553040[12] Sun Z, Wang Y, Xiao R, et al. Directly modulated 25 Gbaud/s tunable in-series DFB laser array for WDM systems. Chin Opt Lett, 2023, 21(1), 90 doi: 10.3788/COL202321.011403[13] Hecht U, Ordouei H, Ledentsov N, et al. True voltage-mode NRZ VCSEL transmitter enabling 60 Gbit/s at 0.37 pJ/bit in 22 nm FDSOI. ESSCIRC 2023-IEEE 49th European Solid State Circuits Conference (ESSCIRC), 2023, 365 doi: 10.1109/ESSCIRC59616.2023.10268797[14] Raj M, Monge M, Emami A. A 20Gb/s 0.77pJ/b VCSEL transmitter with nonlinear equalization in 32nm SOI CMOS. 2015 IEEE Custom Integrated Circuits Conference (CICC), 2015, 1 doi: 10.1109/CICC.2015.7338415[15] Chen F Z, Zhang C Y, Wang L, et al. A 2.05-pJ/b 56-Gb/s PAM-4 VCSEL transmitter with piecewise nonlinearity compensation and asymmetric equalization in 40-nm CMOS. ESSCIRC 2023-IEEE 49th European Solid State Circuits Conference (ESSCIRC), 2023, 373 doi: 10.1109/ESSCIRC59616.2023.10268794[16] Li H, Balamurugan G, Kim T, et al. A 3-D-integrated silicon photonic microring-based 112-Gb/s PAM-4 transmitter with nonlinear equalization and thermal control. IEEE J Solid State Circuits, 2021, 56(1), 19 doi: 10.1109/JSSC.2020.3022851[17] Peng P J, Lee P L, Huang H E, et al. A 56-Gb/s PAM-4 transmitter/receiver chipset with nonlinear FFE for VCSEL-based optical links in 40-nm CMOS. IEEE J Solid State Circuits, 2022, 57(10), 3025 doi: 10.1109/JSSC.2022.3192711[18] Hu S, Yao T Y, Yin B Z, et al. A 50Gb/s PAM-4 retimer-CDR + VCSEL driver with asymmetric pulsed pre-emphasis integrated into a single CMOS die. 2019 Optical Fiber Communications Conference and Exhibition (OFC), 2019, 1[19] Ho W H, Hsieh Y H, Murmann B, et al. A 32 Gb/s PAM-4 optical transceiver with active back termination in 40 nm CMOS technology. IEEE Open J Circuits Syst, 2021, 2, 56 doi: 10.1109/OJCAS.2020.3036531 -

Proportional views

Yang Min is currently pursuing the master’s degree in electronic information with the University of Chinese Academy of Sciences, Beijing, China. His research interests include IC design of radio frequency and mixed signal specific to silicon photonics and electrical/optical transceivers.

Yang Min is currently pursuing the master’s degree in electronic information with the University of Chinese Academy of Sciences, Beijing, China. His research interests include IC design of radio frequency and mixed signal specific to silicon photonics and electrical/optical transceivers. Nan Qi is now a Full Professor of electrical circuits and systems at the Institute of Semiconductors, Chinese Academy of Sciences, Beijing. His research interests include the design of integrated circuits for high-speed wireline/optical and wireless transceivers.

Nan Qi is now a Full Professor of electrical circuits and systems at the Institute of Semiconductors, Chinese Academy of Sciences, Beijing. His research interests include the design of integrated circuits for high-speed wireline/optical and wireless transceivers. Yihan Chen received the B.S. degree in electronic and information engineering from University of Chinese Academy of Sciences, Beijing, China, in 2024. He is currently pursuing the M.S. in circuits and systems with the Institute of Semiconductors, Chinese Academy of Sciences. His main research direction is mixed-signal transceiver and analog-to-digital converter.

Yihan Chen received the B.S. degree in electronic and information engineering from University of Chinese Academy of Sciences, Beijing, China, in 2024. He is currently pursuing the M.S. in circuits and systems with the Institute of Semiconductors, Chinese Academy of Sciences. His main research direction is mixed-signal transceiver and analog-to-digital converter. Minye Zhu received the B.S. degree in electronic and information engineering from University of Chinese Academy of Sciences, Beijing, China, in 2022. He is currently pursuing the M.S. degree in circuits and systems with the University of Chinese Academy of Sciences, Beijing, China. His current research interests include high-speed receiver IC design for silicon photonics and micro-ring thermo-optical modulation.

Minye Zhu received the B.S. degree in electronic and information engineering from University of Chinese Academy of Sciences, Beijing, China, in 2022. He is currently pursuing the M.S. degree in circuits and systems with the University of Chinese Academy of Sciences, Beijing, China. His current research interests include high-speed receiver IC design for silicon photonics and micro-ring thermo-optical modulation. Guike Li is an Assistant Professor of microelectronics and solid-state electronics with the State Key Laboratory of Semiconductor Physics and Chip Technologies, Institute of Semiconductors, Chinese Academy of Sciences. His current research interests include CMOS image sensors and integrated silicon photonics.

Guike Li is an Assistant Professor of microelectronics and solid-state electronics with the State Key Laboratory of Semiconductor Physics and Chip Technologies, Institute of Semiconductors, Chinese Academy of Sciences. His current research interests include CMOS image sensors and integrated silicon photonics. Zhao Zhang is a Full Professor at Institute of Semiconductors, Chinese Academy of Sciences. His research interests include the design of low-jitter and low-power PLLs, RF/mm-wave frequency synthesizers, and wireline transceivers.

Zhao Zhang is a Full Professor at Institute of Semiconductors, Chinese Academy of Sciences. His research interests include the design of low-jitter and low-power PLLs, RF/mm-wave frequency synthesizers, and wireline transceivers. Jian Liu is a Full Professor in microelectronics and solid-state electronics with the State Key Laboratory of Super-lattices and Microstructures, Institute of Semiconductors, Chinese Academy of Sciences, Beijing, China, since 2005. His research interests include semiconductor optoelectronic detectors, terahertz imagers, and metamaterials.

Jian Liu is a Full Professor in microelectronics and solid-state electronics with the State Key Laboratory of Super-lattices and Microstructures, Institute of Semiconductors, Chinese Academy of Sciences, Beijing, China, since 2005. His research interests include semiconductor optoelectronic detectors, terahertz imagers, and metamaterials. Nanjian Wu has been a Professor with the State Key Laboratory of Super-lattices and Microstructures, Institute of Semiconductors, Chinese Academy of Sciences, Beijing, China, since 2000. His research includes the field of mixed-signal VLSI and vision chip design.

Nanjian Wu has been a Professor with the State Key Laboratory of Super-lattices and Microstructures, Institute of Semiconductors, Chinese Academy of Sciences, Beijing, China, since 2000. His research includes the field of mixed-signal VLSI and vision chip design. Jingbo Shi is now a Full Professor with the State Key Laboratory of Information Photonics and Optical Communications, Beijing University of Posts and Telecommunications. His research interests include co-designed photonic integrated circuits (PICs) and electrical integrated circuits (EICs) for high-performance computing, optical-IOs and integrated microwave photonics (MWP).

Jingbo Shi is now a Full Professor with the State Key Laboratory of Information Photonics and Optical Communications, Beijing University of Posts and Telecommunications. His research interests include co-designed photonic integrated circuits (PICs) and electrical integrated circuits (EICs) for high-performance computing, optical-IOs and integrated microwave photonics (MWP). Frank F. Shi received Master Degree of Science from Stanford University, USA, in 1996 and PhD degree from University of Illinois at Urbana-Champaign, USA, in 2004. He was with Micron Technology, USA, as Senior Manager, Corporate Development from January 2004 to January 2007, with Nantronics Semiconductor Co. as Co-founder, CEO & President, China, from January 2007 to April 2015 and with PhotonIC Technologies Co. as Co-founder, China, from September 2015 to now. He is dedicated in developing and commercializing low-power high-speed optoelectronic integrated IC solutions to serve the fast-growing optical/data-com, and 3D sensing markets.

Frank F. Shi received Master Degree of Science from Stanford University, USA, in 1996 and PhD degree from University of Illinois at Urbana-Champaign, USA, in 2004. He was with Micron Technology, USA, as Senior Manager, Corporate Development from January 2004 to January 2007, with Nantronics Semiconductor Co. as Co-founder, CEO & President, China, from January 2007 to April 2015 and with PhotonIC Technologies Co. as Co-founder, China, from September 2015 to now. He is dedicated in developing and commercializing low-power high-speed optoelectronic integrated IC solutions to serve the fast-growing optical/data-com, and 3D sensing markets. Liyuan Liu joined the State Key Laboratory of Super-lattices and Microstructures, Institute of Semiconductors, Chinese Academy of Sciences, Beijing, as an Associate Professor in 2012, where he became a Professor in 2018. His research interests include mixed-signal IC design, CMOS image sensors design, terahertz image sensors design, and monolithic vision chip design.

Liyuan Liu joined the State Key Laboratory of Super-lattices and Microstructures, Institute of Semiconductors, Chinese Academy of Sciences, Beijing, as an Associate Professor in 2012, where he became a Professor in 2018. His research interests include mixed-signal IC design, CMOS image sensors design, terahertz image sensors design, and monolithic vision chip design.

DownLoad:

DownLoad: