| Citation: |

Huanan Guo, Yufeng Yao, Jiazhen Ni, Xiang Gao. A 112 Gbps DSP-based PAM4 SerDes receiver with a wide band equalization tuning AFE in 7 nm FinFET[J]. Journal of Semiconductors, 2025, 46(6): 062204. doi: 10.1088/1674-4926/25030001

****

H N Guo, Y F Yao, J Z Ni, and X Gao, A 112 Gbps DSP-based PAM4 SerDes receiver with a wide band equalization tuning AFE in 7 nm FinFET[J]. J. Semicond., 2025, 46(6), 062204 doi: 10.1088/1674-4926/25030001

|

A 112 Gbps DSP-based PAM4 SerDes receiver with a wide band equalization tuning AFE in 7 nm FinFET

DOI: 10.1088/1674-4926/25030001

CSTR: 32376.14.1674-4926.25030001

More Information-

Abstract

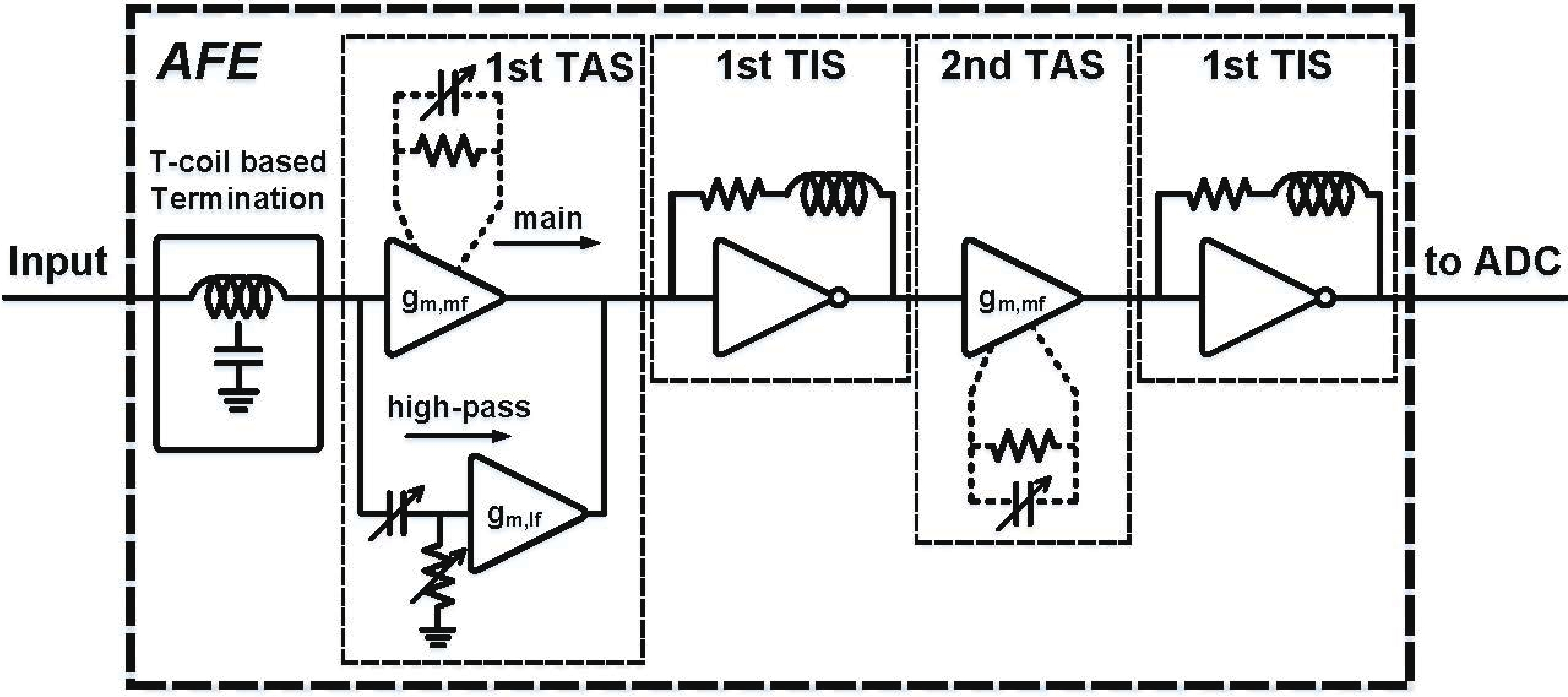

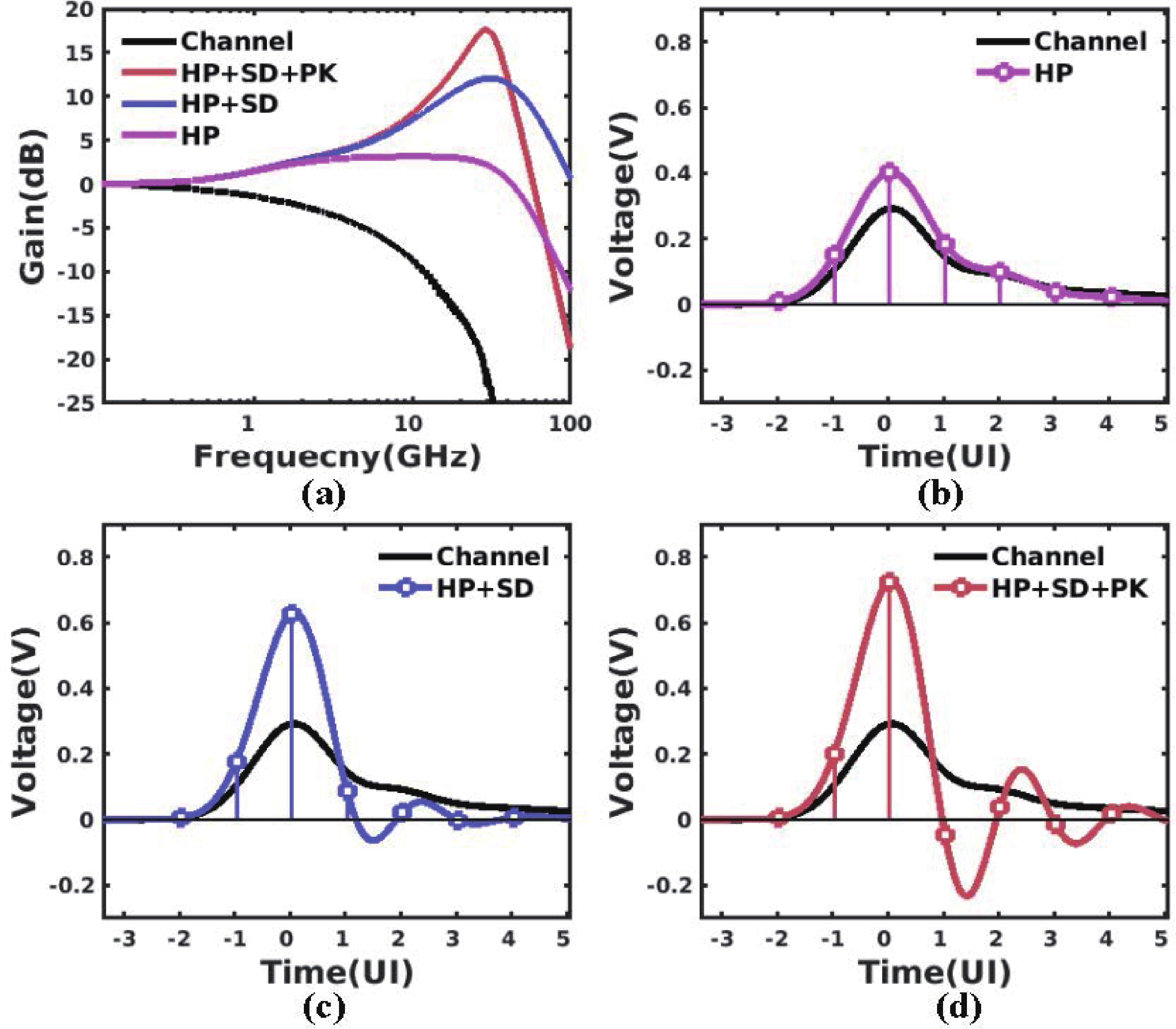

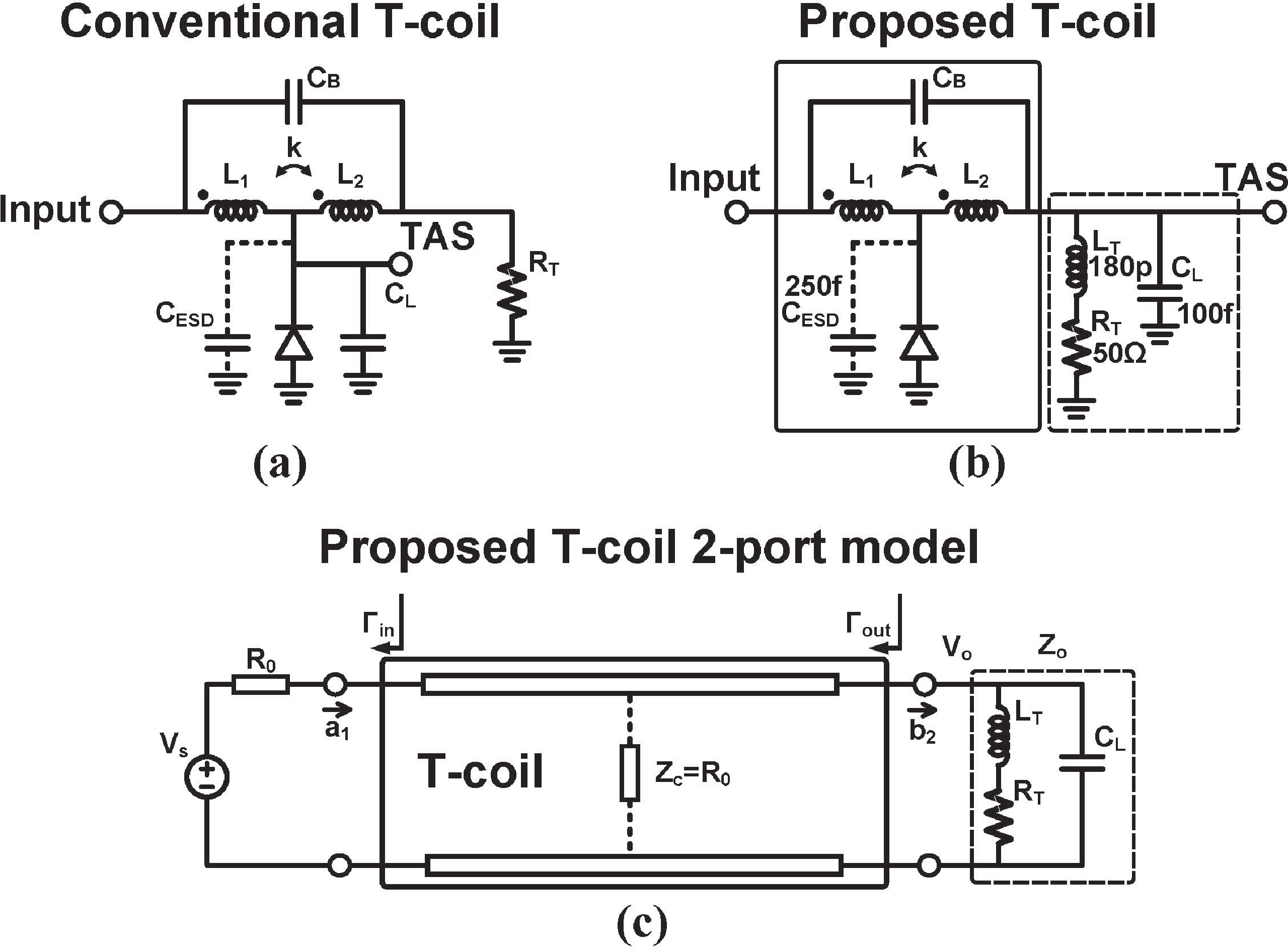

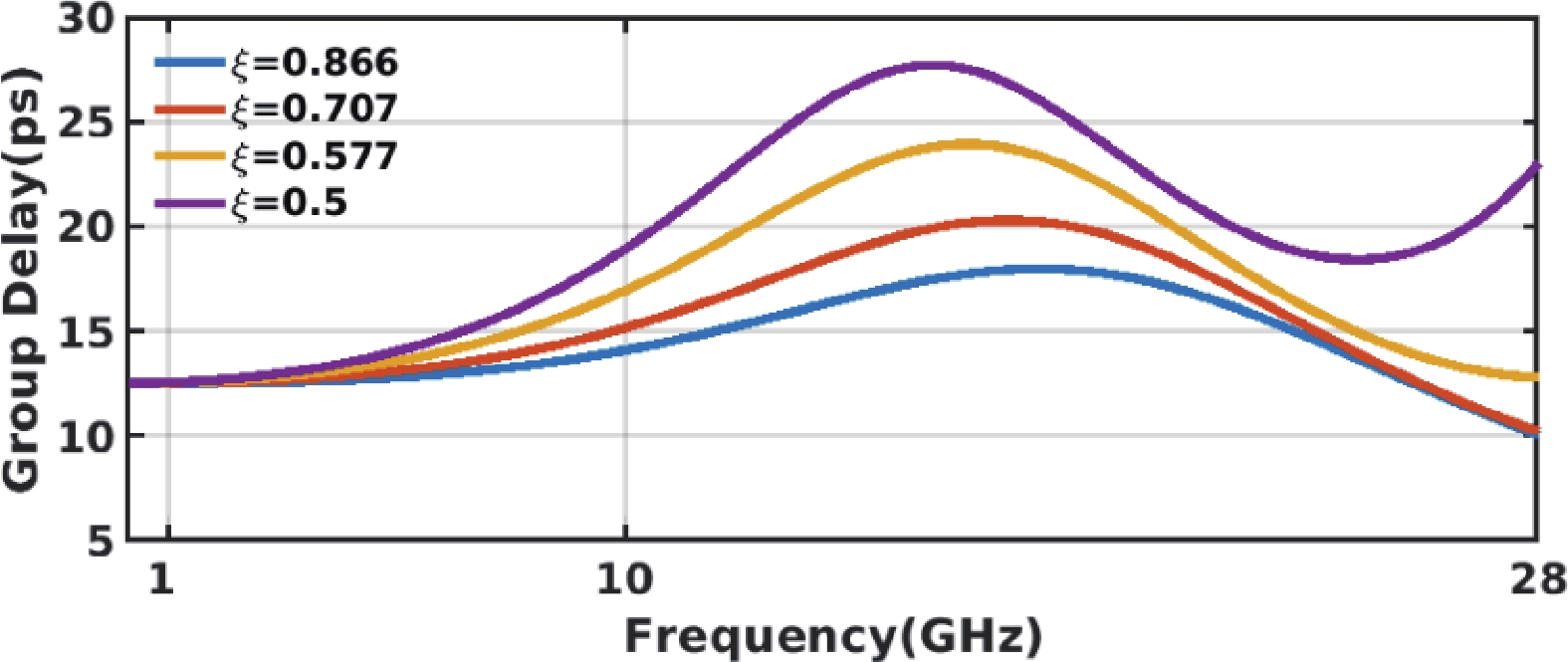

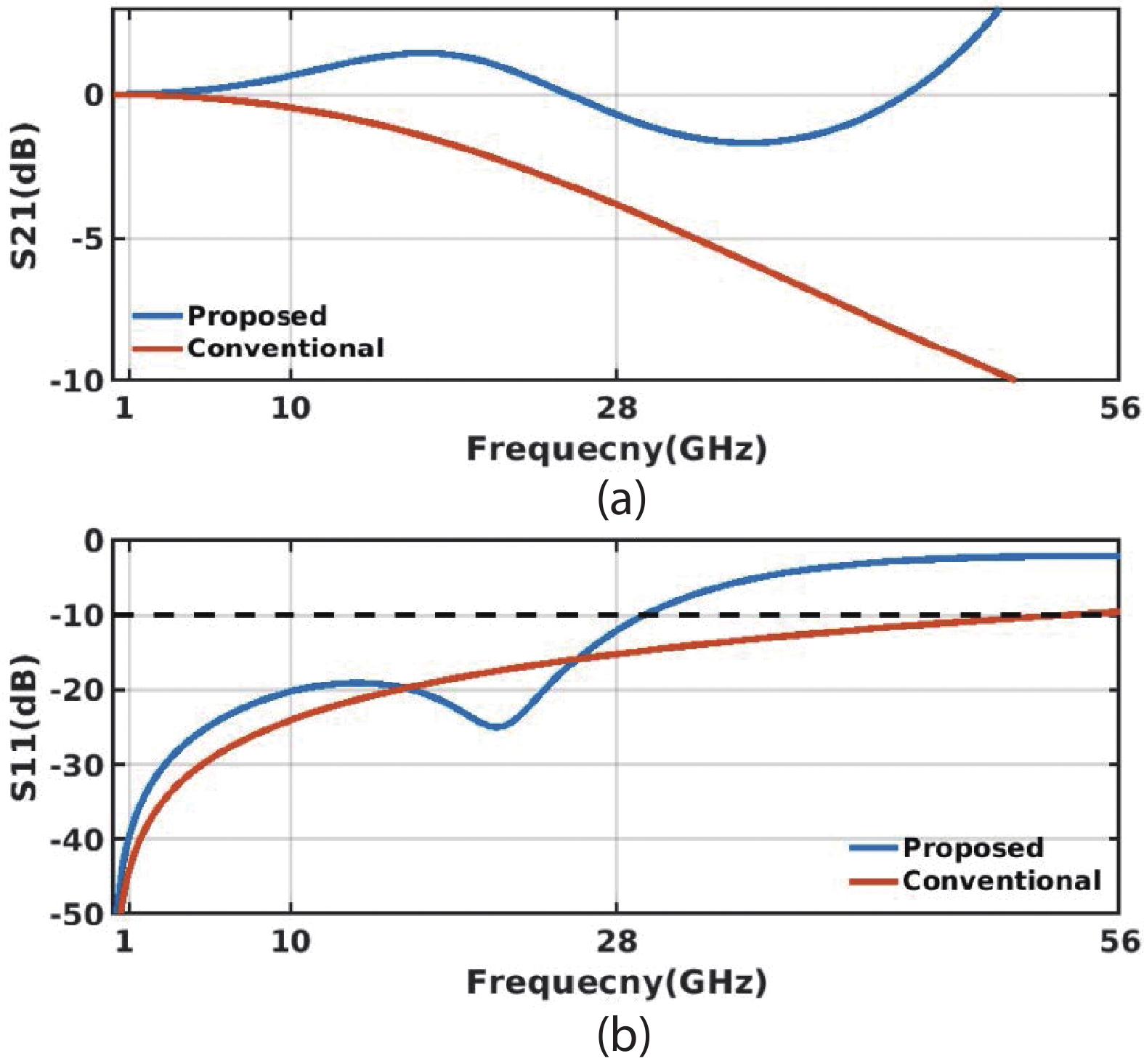

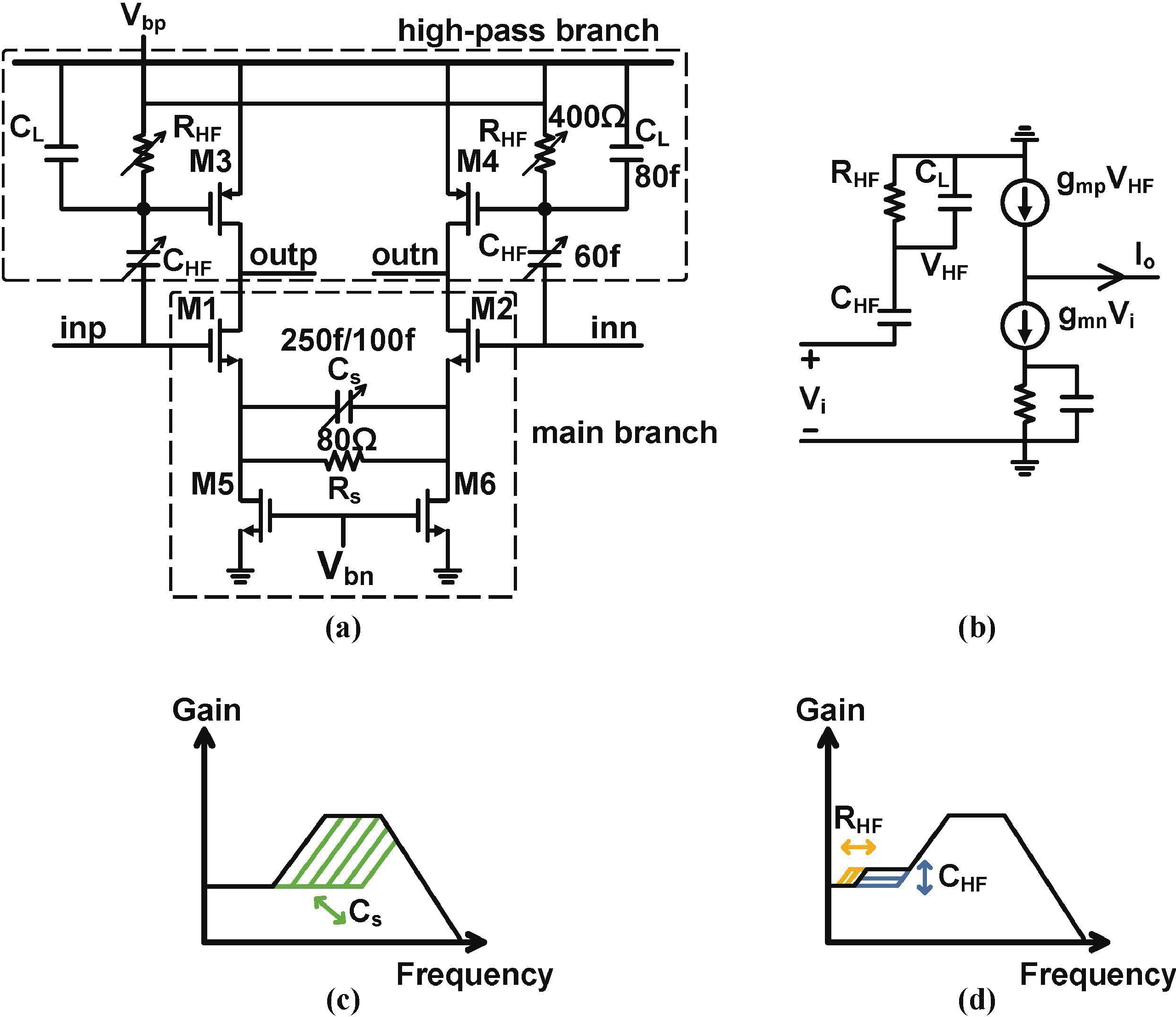

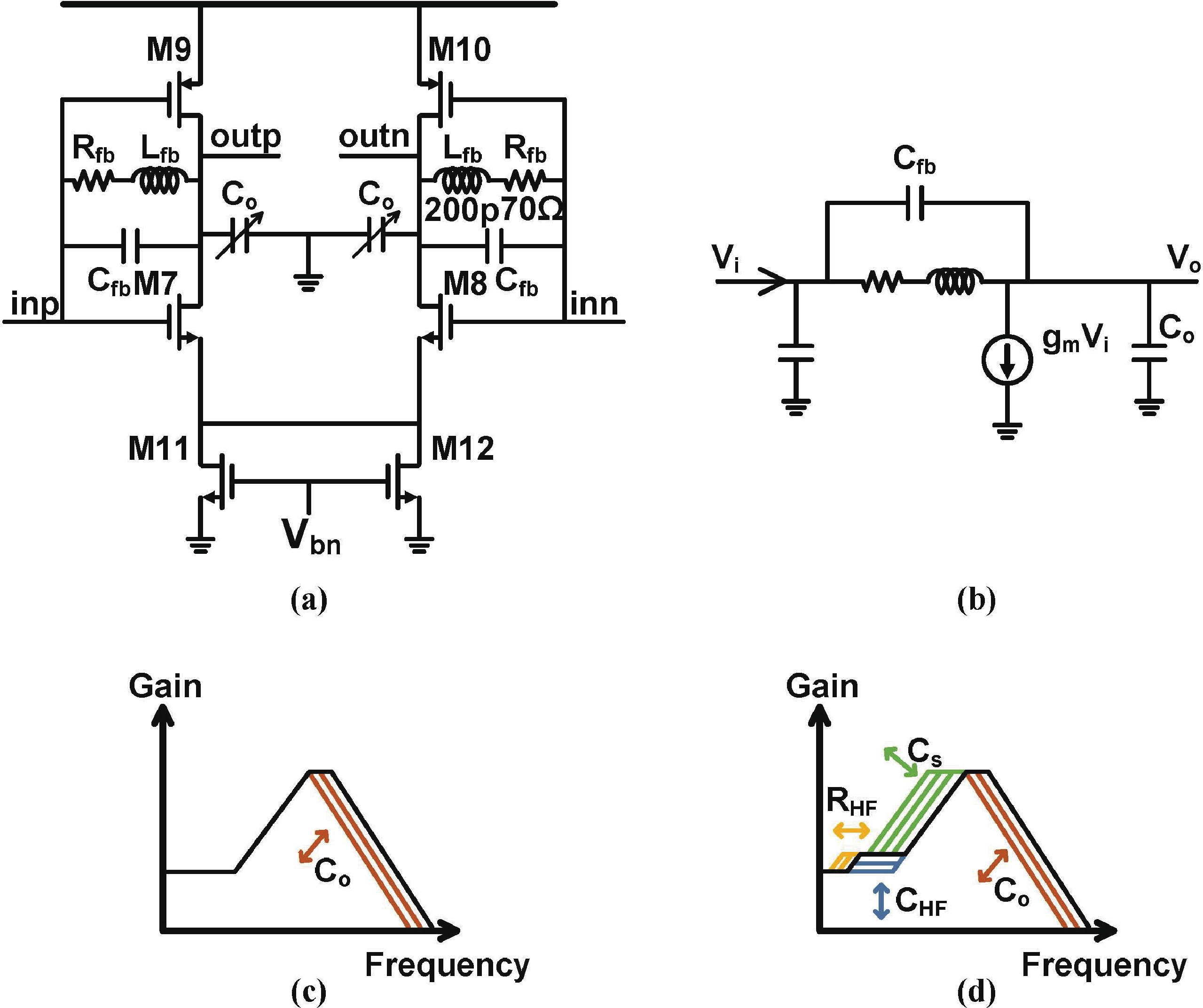

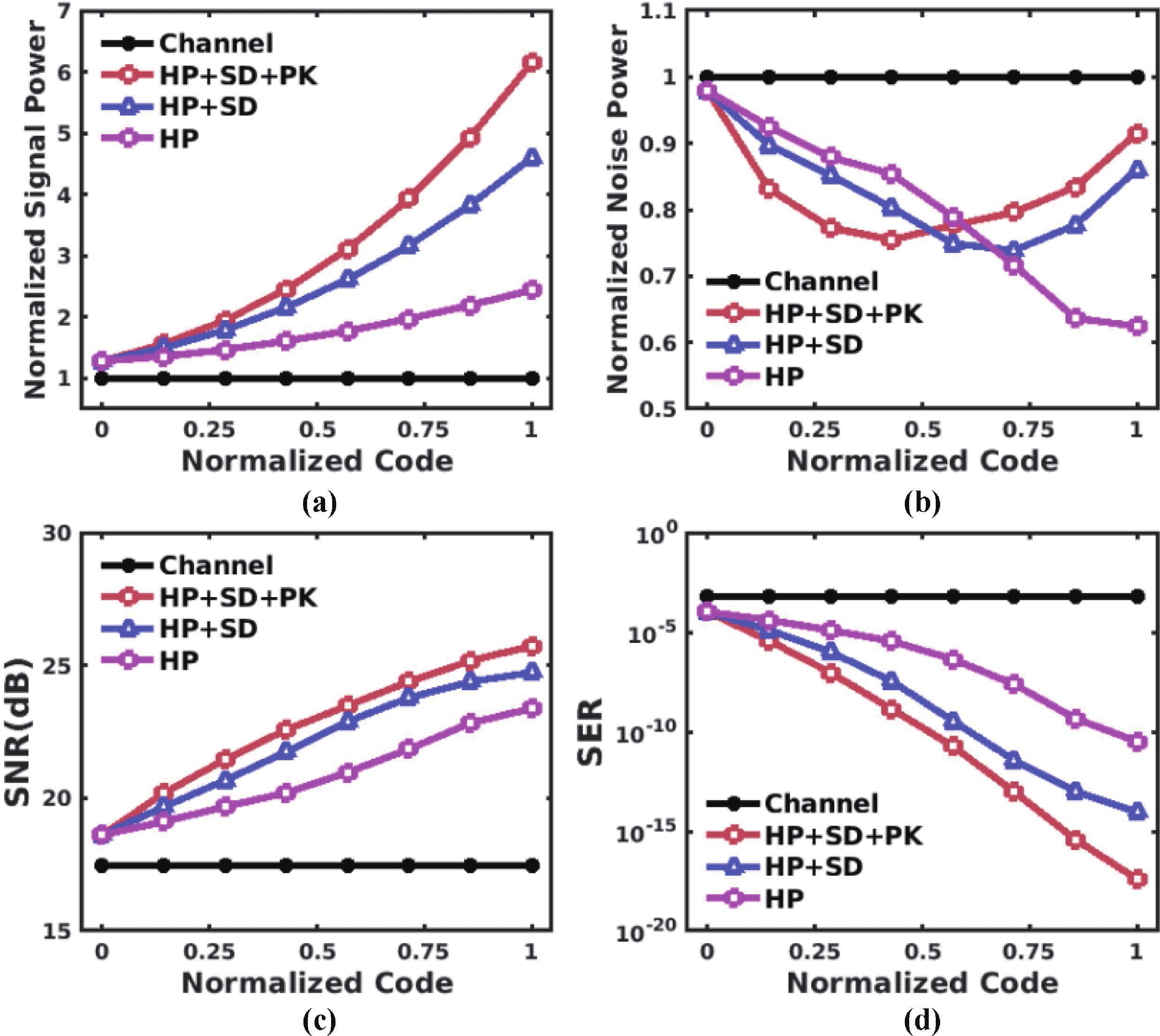

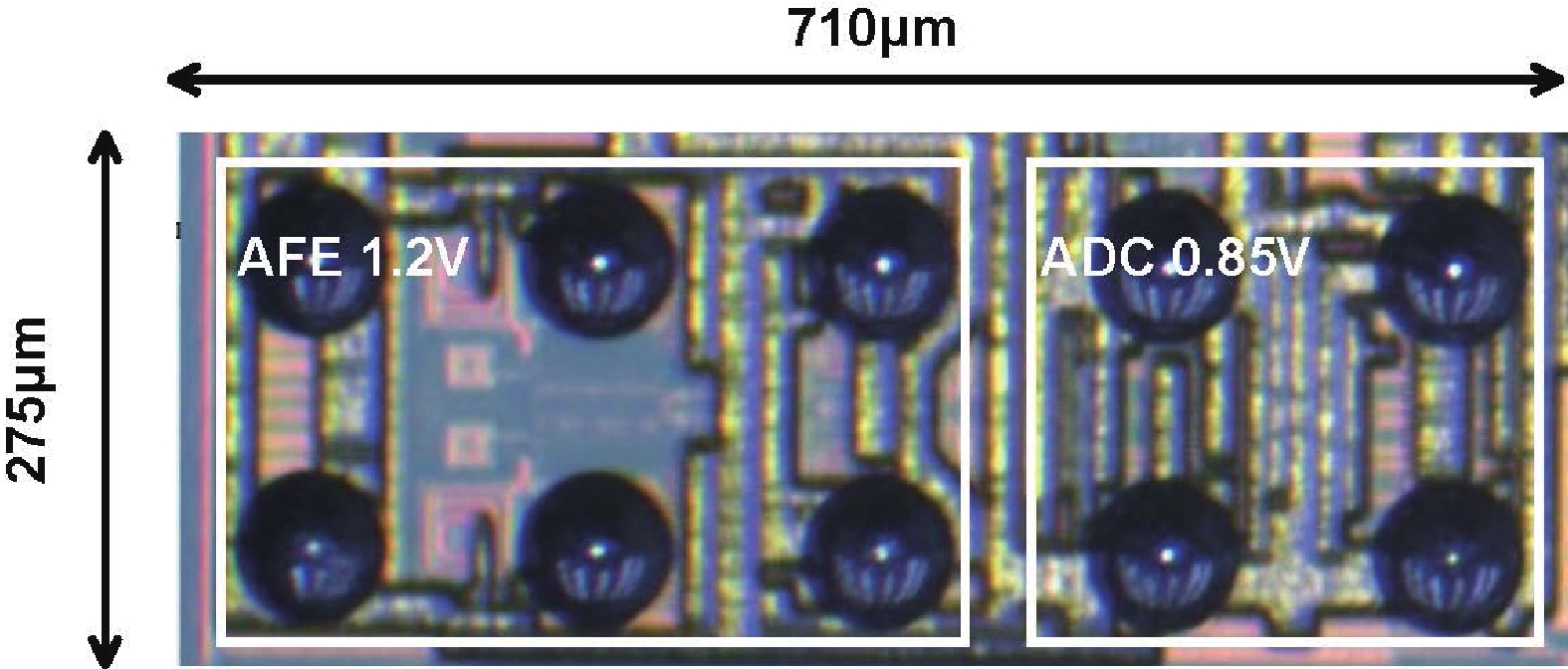

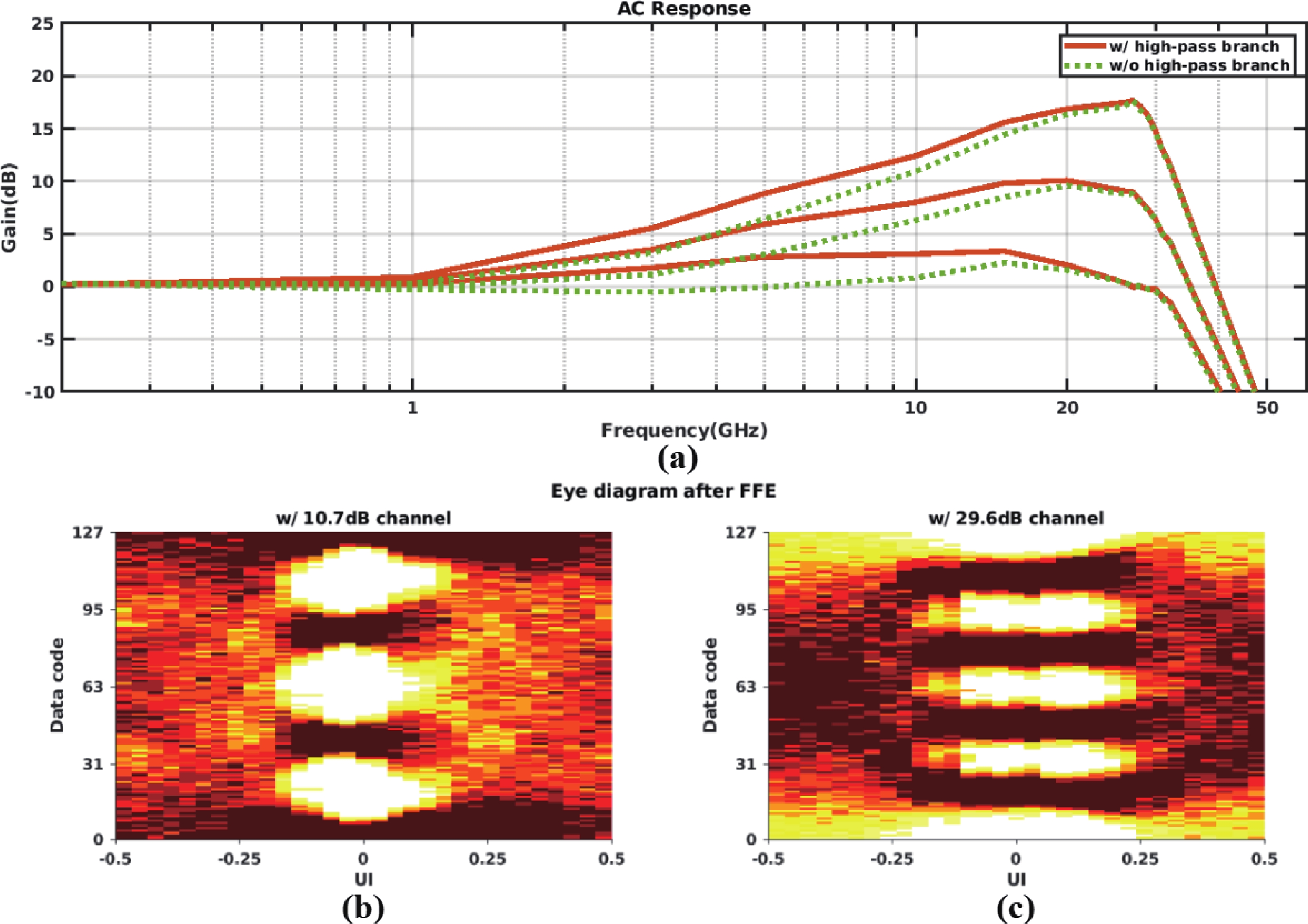

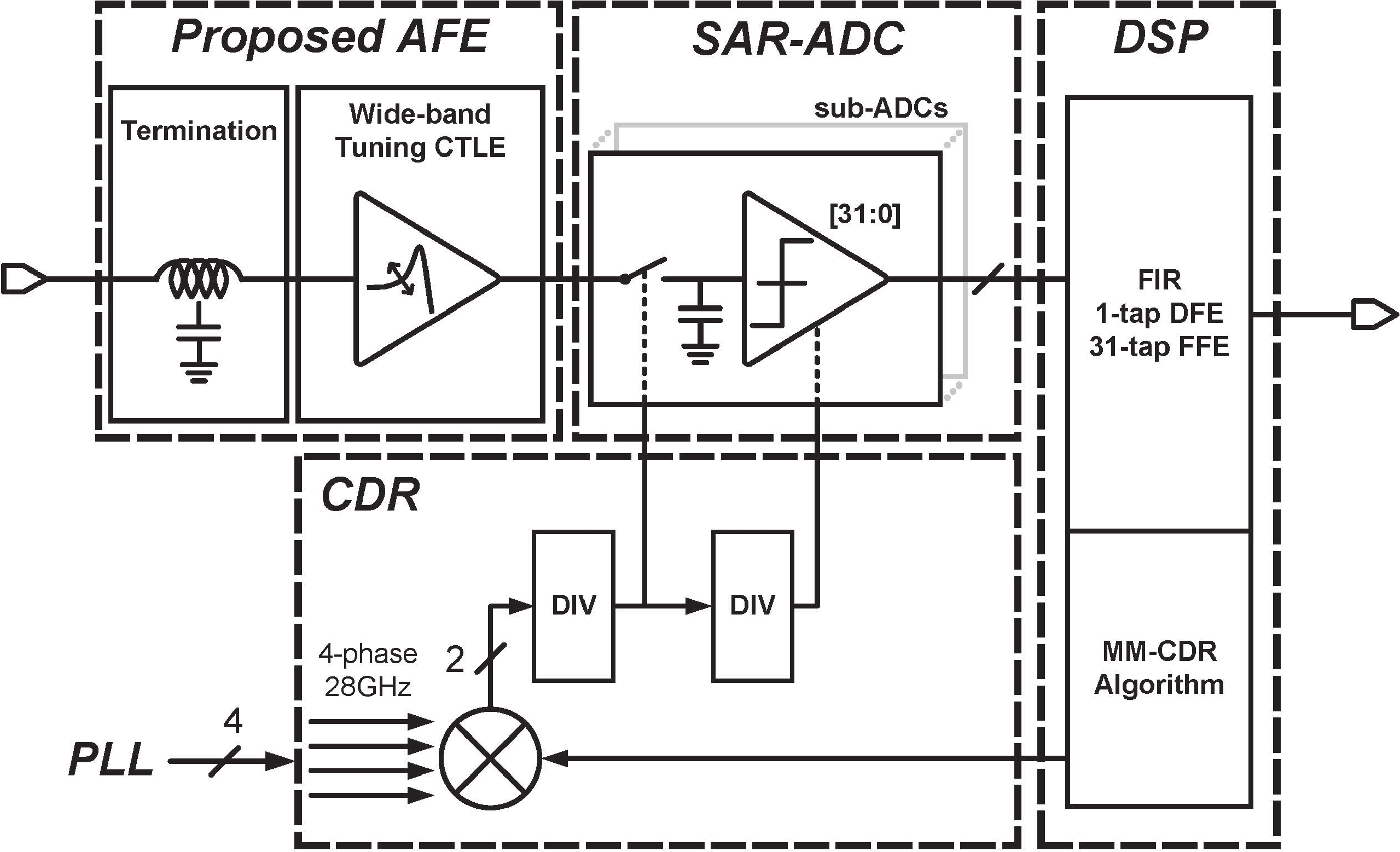

In DSP-based SerDes application, it is essential for AFE to implement a pre-ADC equalization to provide a better signal for ADC and DSP. To meet the various equalization requirements of different channel and transmitter configurations, this paper presents a 112 Gbps DSP-Based PAM4 SerDes receiver with a wide band equalization tuning AFE. The AFE is realized by implementing source degeneration transconductance, feedforward high-pass branch and inductive feedback peaking TIA. The AFE offers a flexible equalization gain tuning of up to 17.5 dB at Nyquist frequency without affecting the DC gain. With the proposed AFE, the receiver demonstrates eye opening after digital FIR equalization and achieves 6 × 10−9 BER with a 29.6 dB insertion loss channel.-

Keywords:

- AFE,

- 112Gbps,

- SerDes receiver,

- wide band equalization

-

References

[1] Krupnik Y, Perelman Y, Levin I, et al. 112-Gb/s PAM4 ADC-based SERDES receiver with resonant AFE for long-reach channels. IEEE J Solid State Circuits, 2020, 55(4), 1077 doi: 10.1109/JSSC.2019.2959511[2] Im J, Zheng K, Chou C A, et al. A 112-Gb/s PAM-4 long-reach wireline transceiver using a 36-way time-interleaved SAR ADC and inverter-based RX analog front-end in 7-nm FinFET. IEEE J Solid State Circuits, 2021, 56(1), 7 doi: 10.1109/JSSC.2020.3024261[3] Park H, Abdullatif M, Chen E, et al. A 4.63pJ/b 112Gb/s DSP-based PAM-4 transceiver for a large-scale switch in 5nm FinFET. 2023 IEEE International Solid-State Circuits Conference (ISSCC), 2023, 5 doi: 10.1109/ISSCC42615.2023.10067613[4] Khairi A, Krupnik Y, Laufer A, et al. A 1.41-pJ/b 224-Gb/s PAM4 6-bit ADC-based SerDes receiver with hybrid AFE capable of supporting long reach channels. IEEE J Solid State Circuits, 2023, 58(1), 8 doi: 10.1109/JSSC.2022.3211475[5] Li Z H, Tang M Z, Fan T Y, et al. A 56-Gb/s PAM4 receiver analog front-end with fixed peaking frequency and bandwidth in 40-nm CMOS. IEEE Trans Circuits Syst II Express Briefs, 2021, 68(9), 3058 doi: 10.1109/TCSII.2021.3074384[6] Parikh S, Kao T, Hidaka Y, et al. A 32Gb/s wireline receiver with a low-frequency equalizer, CTLE and 2-tap DFE in 28nm CMOS. 2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers, 2013, 28 doi: 10.1109/ISSCC.2013.6487622[7] Bailey J, Shakiba H, Nir E, et al. A 112-Gb/s PAM-4 low-power nine-tap sliding-block DFE in a 7-nm FinFET wireline receiver. IEEE J Solid State Circuits, 2022, 57(1), 32 doi: 10.1109/JSSC.2021.3109167[8] Pisati M, De Bernardinis F, Pascale P, et al. A 243-mW 1.25–56-Gb/s continuous range PAM-4 42.5-dB IL ADC/DAC-based transceiver in 7-nm FinFET. IEEE J Solid State Circuits, 2020, 55(1), 6 doi: 10.1109/JSSC.2019.2936307[9] Lin Y P, Peng P J, Lu C C, et al. 7.7 A 2.16pJ/b 112Gb/s PAM-4 transceiver with time-interleaved 2b/3b ADCs and unbalanced baud-rate CDR for XSR applications in 28nm CMOS. 2024 IEEE International Solid-State Circuits Conference (ISSCC), 2024, 136 doi: 10.1109/ISSCC49657.2024.10454418[10] Ye B Y, Sheng K, Gai W X, et al. A 2. 29pJ/b 112Gb/s wireline transceiver with RX 4-tap FFE for medium-reach applications in 28nm CMOS, 2022, 118 doi: 10.1109/ISSCC42614.2022.9731591[11] de Abreu Farias Neto P W, Hearne K, Chlis I, et al. A 112–134-Gb/s PAM4 receiver using a 36-way dual-comparator TI-SAR ADC in 7-nm FinFET. IEEE Solid State Circuits Lett, 2020, 3, 138 doi: 10.1109/LSSC.2020.3007580[12] Zand B, Bichan M K, Mahmoodi A, et al. A 1-58.125Gb/s, 5-33dB IL multi-protocol Ethernet-compliant analog PAM-4 receiver with 16 DFE taps in 10nm. 2022 IEEE International Solid-State Circuits Conference (ISSCC), 2022, 1 doi: 10.1109/ISSCC42614.2022.9731768[13] Guo Z, Mostafa A, Elshazly A, et al. A 112.5Gb/s ADC-DSP-based PAM-4 long-reach transceiver with >50dB channel loss in 5nm FinFET. 2022 IEEE International Solid-State Circuits Conference (ISSCC), 2022, 116 doi: 10.1109/ISSCC42614.2022.9731650[14] Depaoli E, Zhang H Y, Mazzini M, et al. A 64 gb/s low-power transceiver for short-reach PAM-4 electrical links in 28-nm FDSOI CMOS. IEEE J Solid State Circuits, 2019, 54(1), 6 doi: 10.1109/JSSC.2018.2873602[15] Tang R J, Wang K N, Sun H F, et al. A 112-Gb/s PAM-4 receiver with ultra-fine gain adjustment CTLE and novel sample-and-reset slicer in 28-nm CMOS. 2024 IEEE European Solid-State Electronics Research Conference (ESSERC), 2024, 297 doi: 10.1109/ESSERC62670.2024.10719519[16] Harwood M, Warke N, Simpson R, et al. A 12.5Gb/s SerDes in 65nm CMOS using a baud-rate ADC with digital receiver equalization and clock recovery. 2007 IEEE International Solid-State Circuits Conference. Digest of Technical Papers, 2007, 436 doi: 10.1109/ISSCC.2007.373481[17] Menin D, Bandiziol A, Grollitsch W, et al. Design and simulation of a 12 gb/s transceiver with 8-tap FFE, offset-compensated samplers and fully adaptive 1-tap speculative/3-tap DFE and sampling phase for MIPI A-PHY applications. IEEE Trans Circuits Syst II Express Briefs, 2020, 67(8), 1369 doi: 10.1109/TCSII.2019.2926152[18] Lin H D, Boecker C, Hossain M, et al. ADC-DSP-based 10-to-112-Gb/s multi-standard receiver in 7-nm FinFET. IEEE J Solid State Circuits, 2021, 56(4), 1265 doi: 10.1109/JSSC.2021.3051109 -

Proportional views

Huanan Guo received his bachelor’s degree from the Zhejiang University, China, in 2020. Now he is currently pursuing Ph.D. degree at the Institute of VLSI Design, Zhejiang University, under the supervision of Prof. Xiang Gao. His research focuses on the high speed SerDes receiver design.

Huanan Guo received his bachelor’s degree from the Zhejiang University, China, in 2020. Now he is currently pursuing Ph.D. degree at the Institute of VLSI Design, Zhejiang University, under the supervision of Prof. Xiang Gao. His research focuses on the high speed SerDes receiver design. Xiang Gao received his Ph.D. degree (cum laude) from the University of Twente, The Netherlands in 2010. From 2010 to 2016, he was a principal engineer and design manager with Marvell Semiconductor, Santa Clara, CA, focusing on wireless transceivers ICs. From 2016 to 2018, he was an Engineering Director with Credo Semiconductor, Milpitas, CA, working on high-speed SerDes. Since 2018, he is with the Institute of VLSI Design, Zhejiang University, China. He is an IEEE senior member and currently a TPC member of ISSCC and RFIC.

Xiang Gao received his Ph.D. degree (cum laude) from the University of Twente, The Netherlands in 2010. From 2010 to 2016, he was a principal engineer and design manager with Marvell Semiconductor, Santa Clara, CA, focusing on wireless transceivers ICs. From 2016 to 2018, he was an Engineering Director with Credo Semiconductor, Milpitas, CA, working on high-speed SerDes. Since 2018, he is with the Institute of VLSI Design, Zhejiang University, China. He is an IEEE senior member and currently a TPC member of ISSCC and RFIC.

DownLoad:

DownLoad: