| Citation: |

Wanyi Ling, Ranran Liu, Kun Ren, Dianyu Qi, Yongyu Wu, Guangji Li, Miao Zhou, Qingshuang Xu, Zhenghui Xia, Xuan Li, Dertsyr Fan, Ichun Chuang, Tzung Wen Cheng, Chenming Tsai, Dawei Gao. Optimizing 55 nm split-gate memory for compute-in-memory: a focus on floating-gate engineering[J]. Journal of Semiconductors, 2026, 47(3): 032301. doi: 10.1088/1674-4926/25060033

****

W Y Ling, R R Liu, K Ren, D Y Qi, Y Y Wu, G J Li, M Zhou, Q S Xu, Z H Xia, X Li, D Fan, I Chuang, T W Cheng, C Tsai, and D W Gao, Optimizing 55 nm split-gate memory for compute-in-memory: a focus on floating-gate engineering[J]. J. Semicond., 2026, 47(3): 032301 doi: 10.1088/1674-4926/25060033

|

Optimizing 55 nm split-gate memory for compute-in-memory: a focus on floating-gate engineering

DOI: 10.1088/1674-4926/25060033

CSTR: 32376.14.1674-4926.25060033

More Information-

Abstract

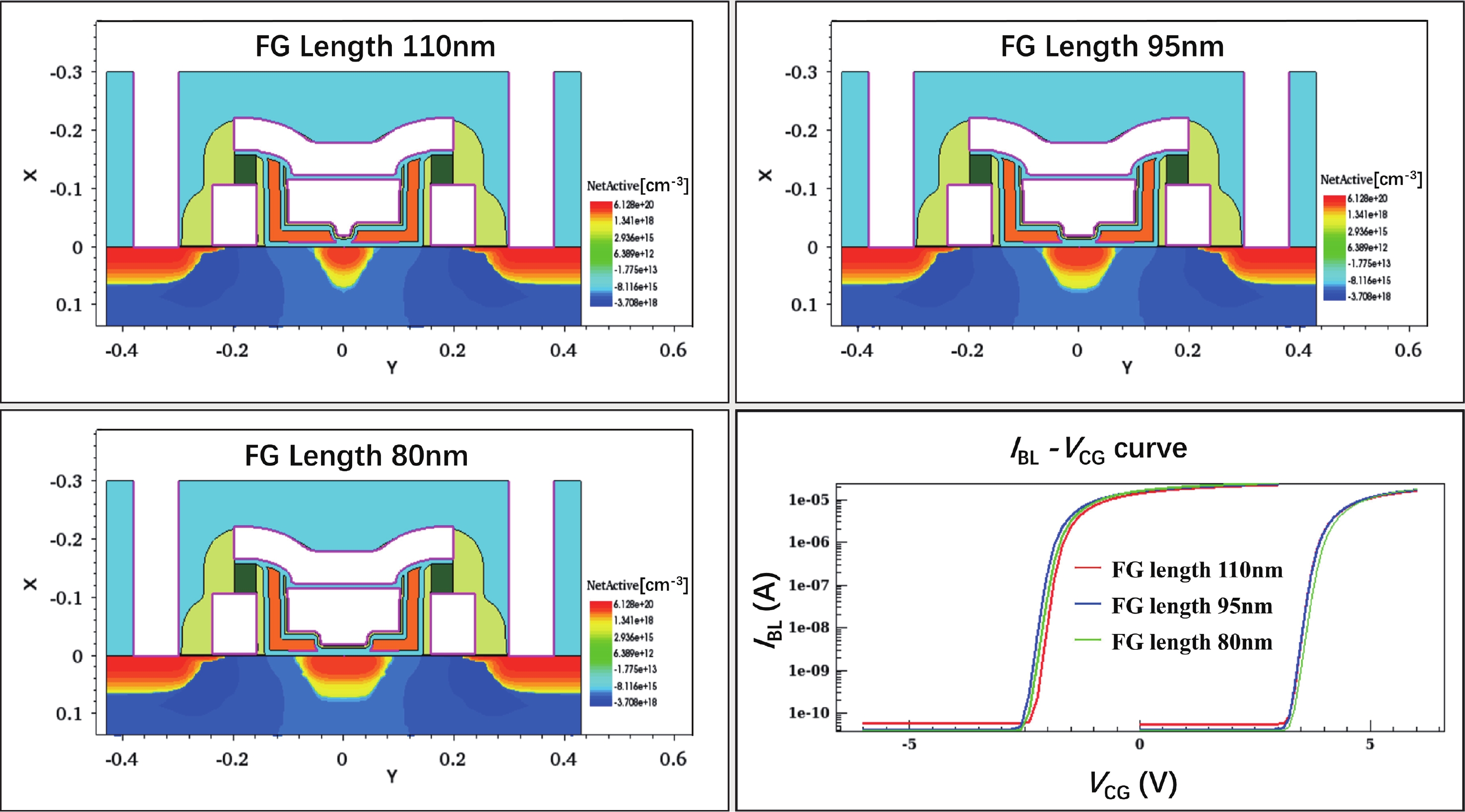

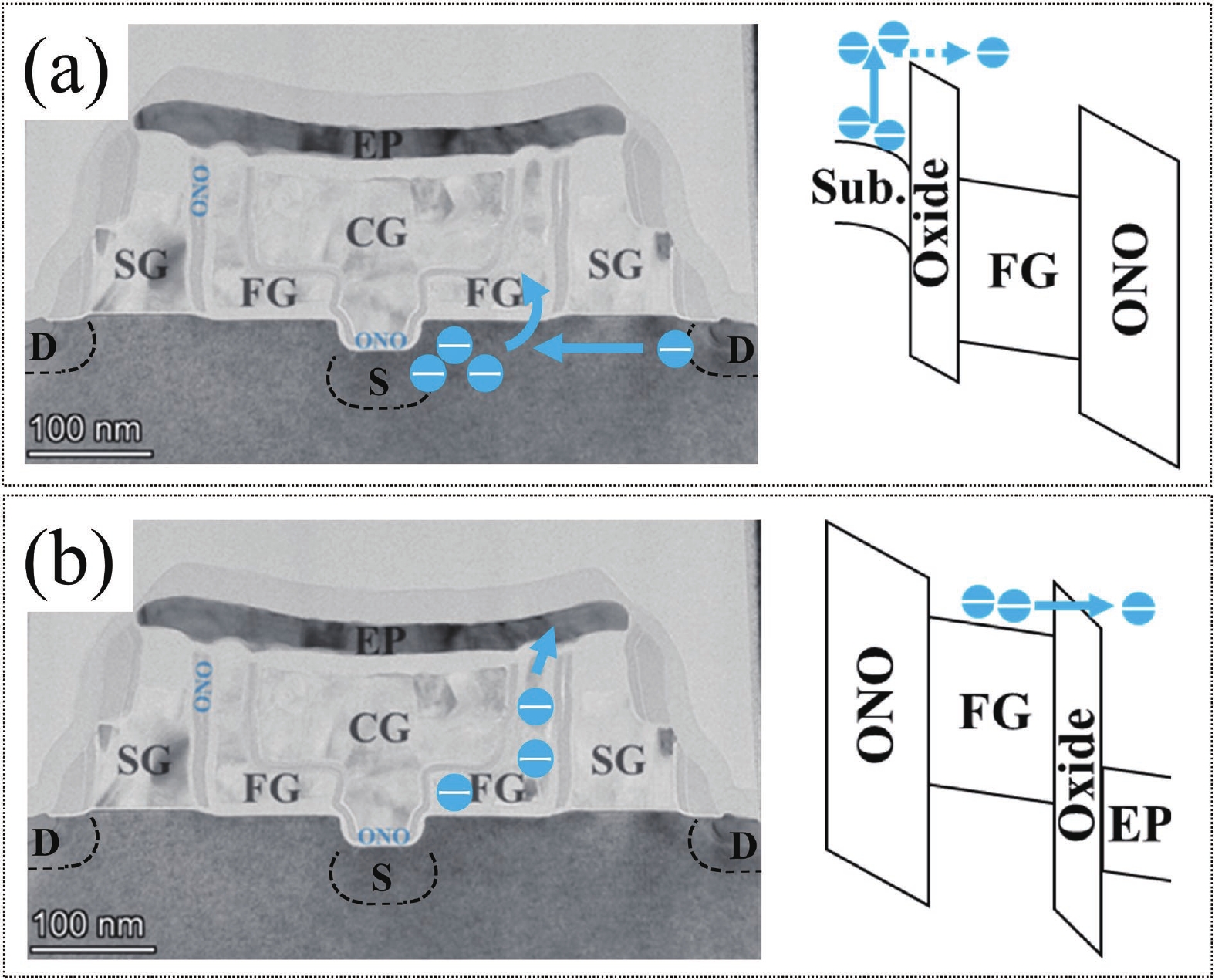

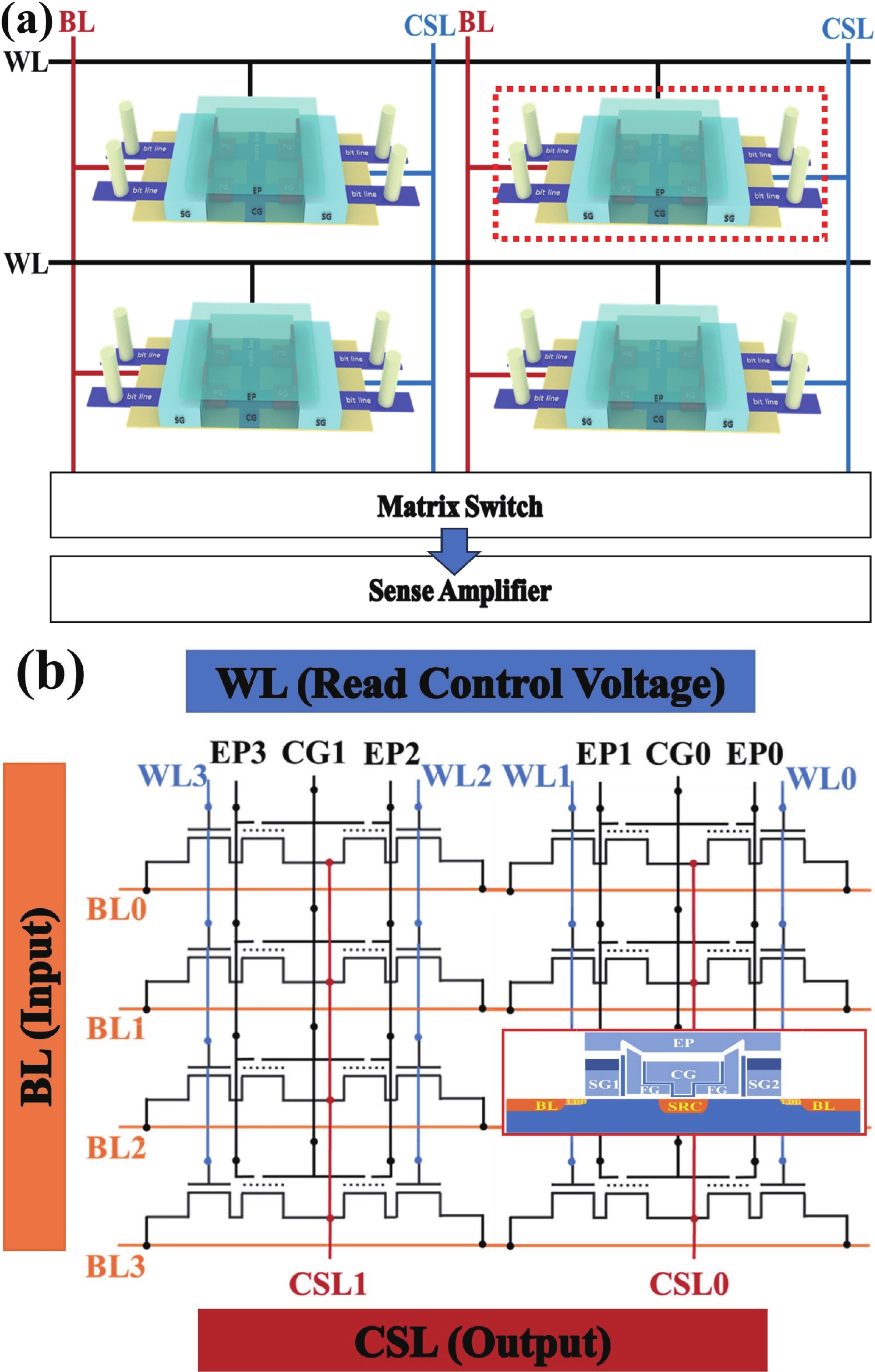

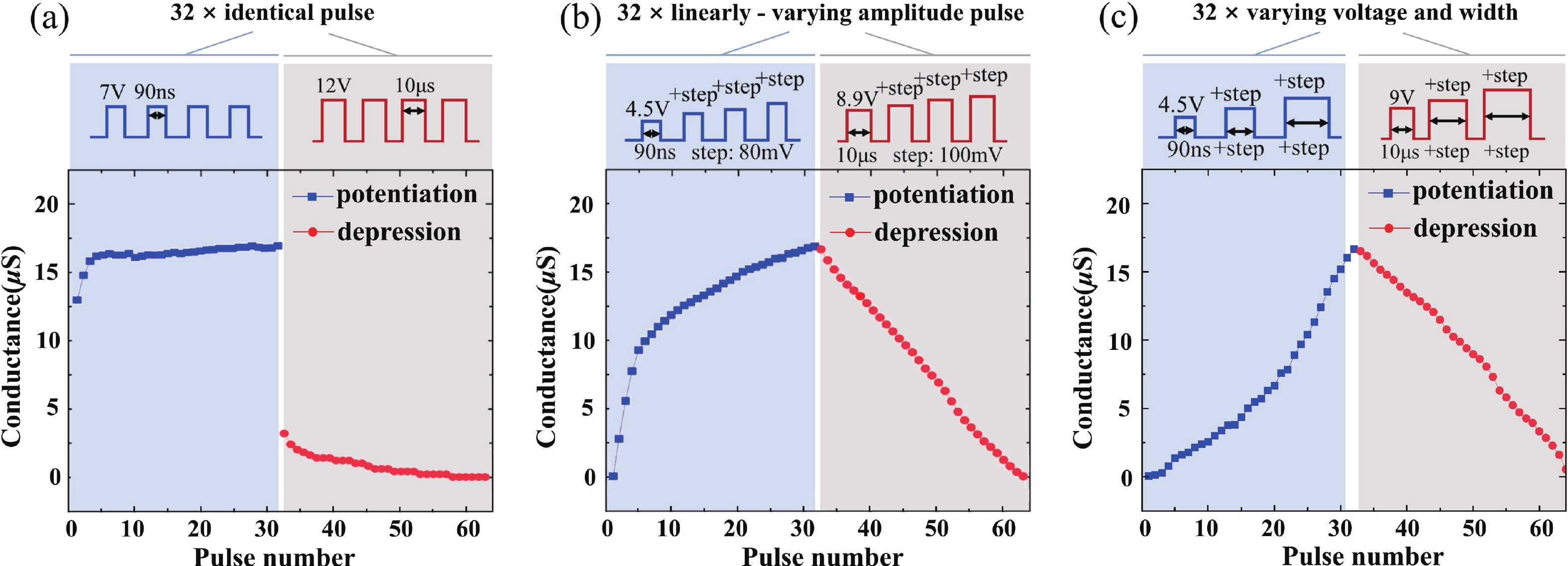

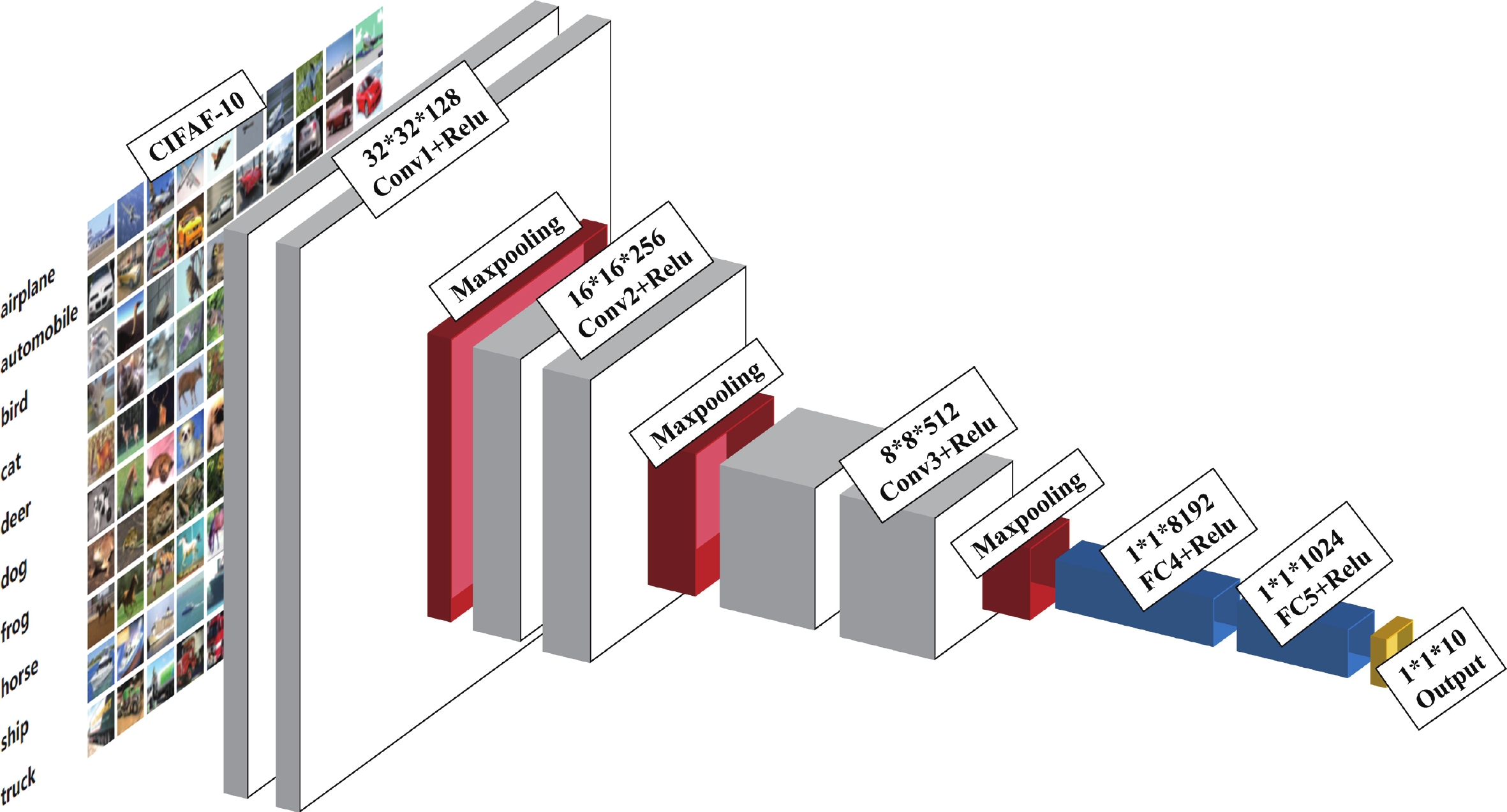

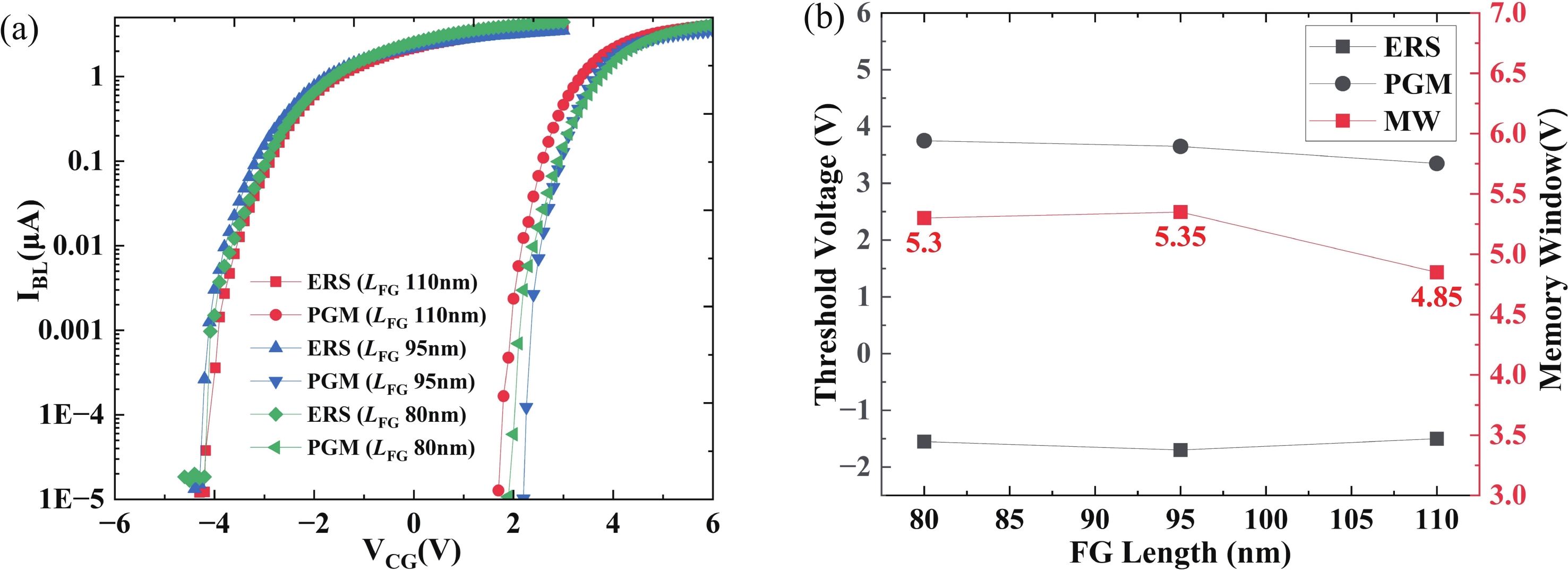

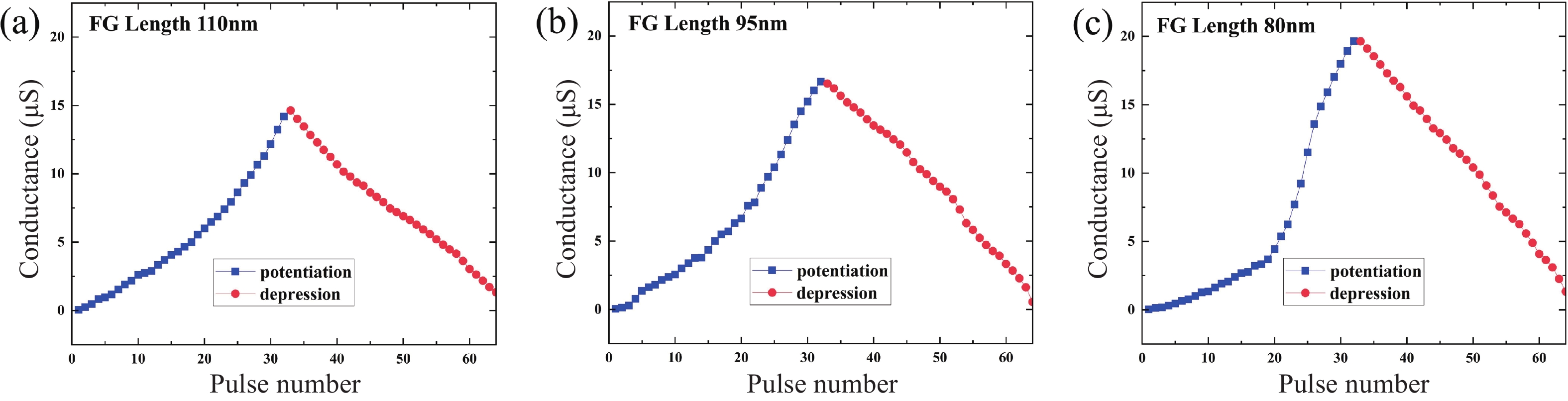

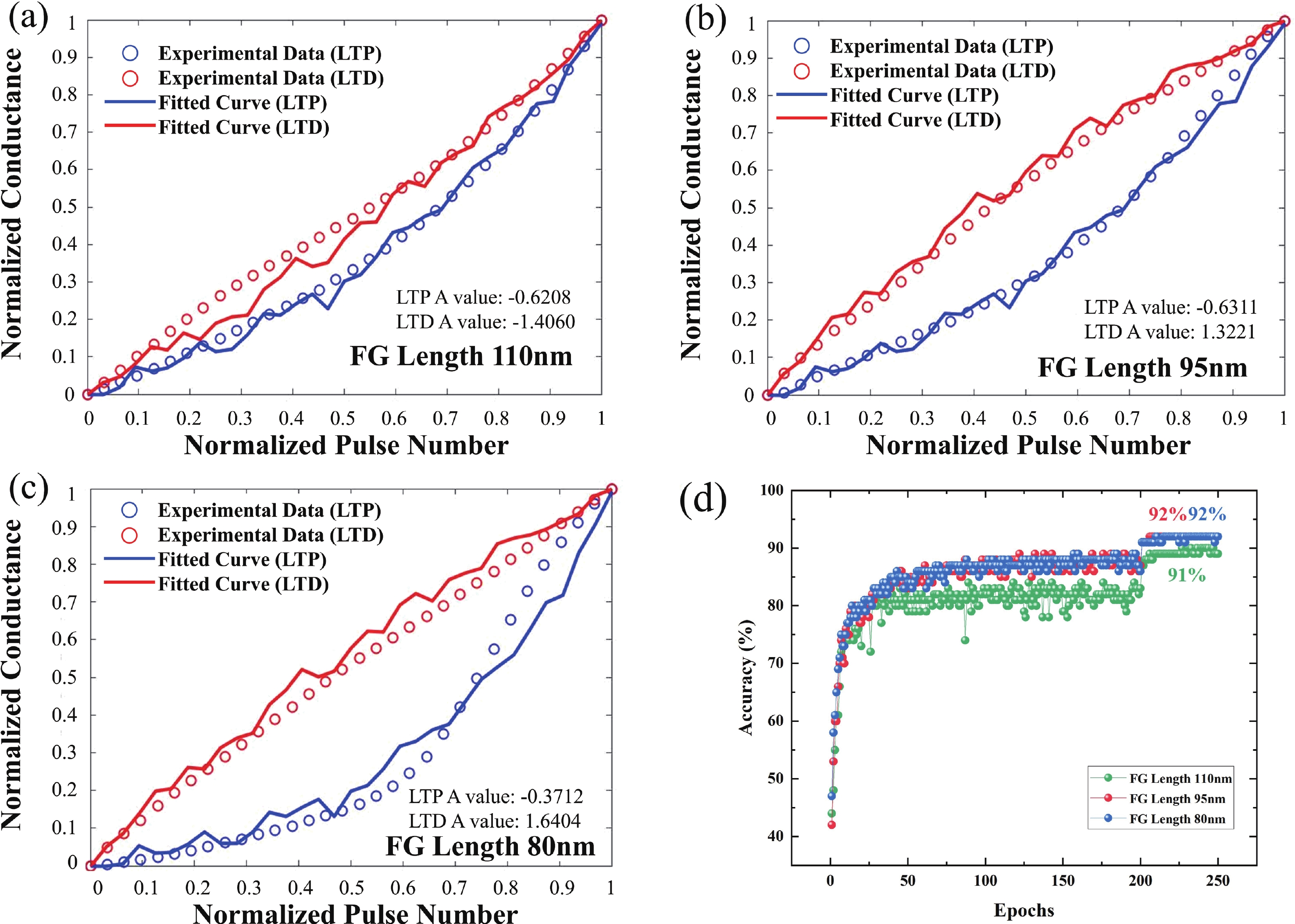

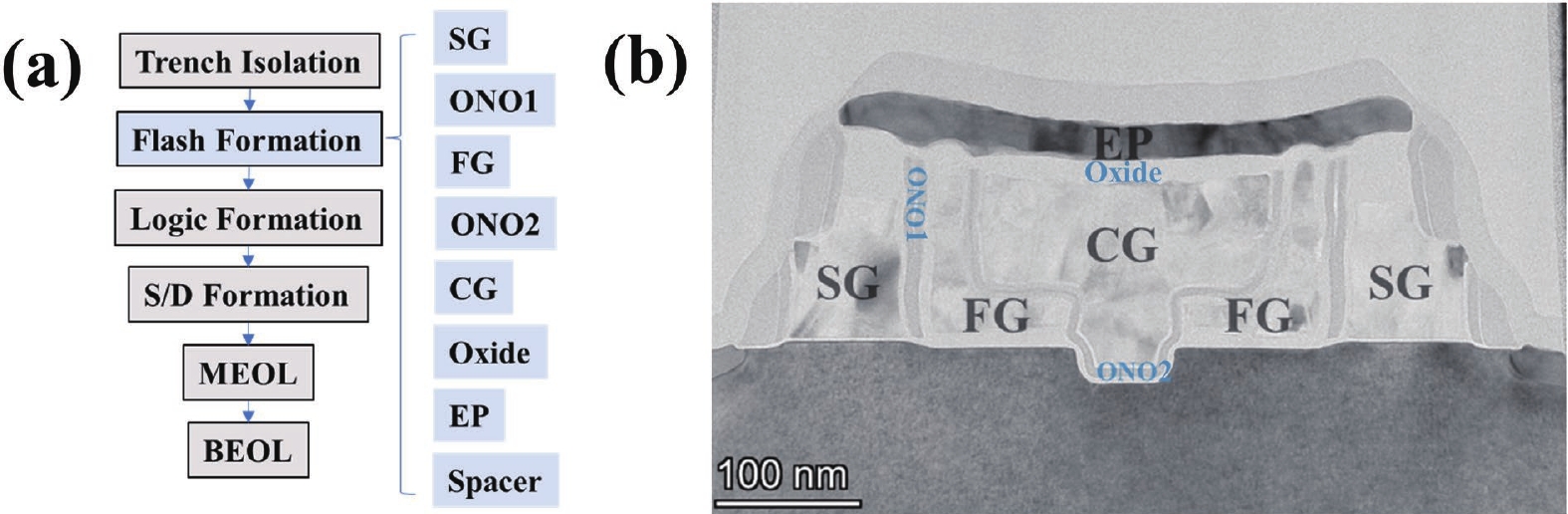

The escalating need for high-performance artificial intelligence (AI) computing intensifies the "memory bottleneck" of the von Neumann architecture, prompting extensive exploration of computation-in-memory (CIM) solutions. This study is centered on the optimization of a high-efficiency, low-power "L"-shaped split-gate floating-gate (FG) memory for CIM applications. Fabricated on a 55 nm CMOS platform, the memory devices were systematically investigated through wafer acceptance test (WAT), Sentaurus™ simulations and comprehensive evaluations with the DNN + NeuroSim Framework V2.0. Among devices with diverse FG lengths, the 95-nm FG variant exhibits outstanding performance: it achieves a 5.35 V memory window, reaches a maximum conductance of 16.7 μS with excellent linearity under the varying voltage and width pulse scheme (VWPS), realizes 32-state multi-level storage, and attains a 92% training accuracy on the CIFAR-10 dataset using the VGG8 neural network. -

References

[1] Yu S M, Jiang H W, Huang S S, et al. Compute-in-memory chips for deep learning: Recent trends and prospects. IEEE Circuits Syst Mag, 2021, 21(3): 31 doi: 10.1109/MCAS.2021.3092533[2] Peng X C, Huang S S, Jiang H W, et al. DNN NeuroSim V2.0: An end-to-end benchmarking framework for compute-in- memory accelerators for on-chip training. IEEE Trans Comput Aided Des Integr Circuits Syst, 2021, 40(11): 2306 doi: 10.1109/TCAD.2020.3043731[3] Yu S M, Shim W, Peng X C, et al. RRAM for compute-in-memory: From inference to training. IEEE Trans Circuits Syst I Regul Pap, 2021, 68(7): 2753 doi: 10.1109/TCSI.2021.3072200[4] Chang L, Ma X, Wang Z H, et al. DASM: Data-streaming-based computing in nonvolatile memory architecture for embedded system. IEEE Trans Very Large Scale Integr VLSI Syst, 2019, 27(9): 2046 doi: 10.1109/TVLSI.2019.2912941[5] Sun X, Khwa W S, Chen Y S, et al. PCM-based analog compute-In-memory: Impact of device non-idealities on inference accuracy. IEEE Trans Electron Devices, 2021, 68(11): 5585 doi: 10.1109/TED.2021.3113300[6] Khwa W S, Chen J J, Li J F, et al. A 65nm 4Kb algorithm-dependent computing-in-memory SRAM unit-macro with 2.3ns and 55.8 TOPS/W fully parallel product-sum operation for binary DNN edge processors. ISSCC, 2018, 8310401: 496 doi: 10.1109/ISSCC.2018.8310401[7] Lo Y C, Liu R S. Morphable CIM: Improving operation intensity and depthwise capability for SRAM-CIM architecture. 2023 60th ACM/IEEE Design Automation Conference (DAC), 2023: 1 doi: 10.1109/DAC56929.2023.10247750[8] Do N, Van Tran H, Kotov A, et al. Split-gate floating poly SuperFlash® memory technology, design, and reliability. Embedded Flash Memory for Embedded Systems: Technology, Design for Sub-systems, and Innovations. Cham: Springer International Publishing, 2017: 131 doi: 10.1007/978-3-319-55306-1_5[9] Yook C G, Kim J N, Kim Y, et al. Design strategies of 40 nm split-gate NOR flash memory device for low-power compute-in-memory applications. Micromachines, 2023, 14(9): 1753 doi: 10.3390/mi14091753[10] Feng Y, Sun Z H, Qi Y R, et al. Optimized operation scheme of flash-memory-based neural network online training with ultra-high endurance. J Semicond, 2024, 45(1): 012301 doi: 10.1088/1674-4926/45/1/012301[11] Feng Y, Chen B, Tang M F, et al. Near-threshold-voltage operation in flash-based high-precision computing-in-memory to implement Poisson image editing. Sci China Inf Sci, 2023, 66(12): 222402 doi: 10.1007/s11432-022-3743-x[12] Zhou Y J, Shao H Y, Zhu R T, et al. Hybrid-FE-layer FeFET with high linearity and endurance toward on-chip CIM by array demonstration. IEEE Electron Device Lett, 2024, 45(2): 276 doi: 10.1109/LED.2023.3346030[13] Jerry M, Dutta S, Kazemi A, et al. A ferroelectric field effect transistor based synaptic weight cell. J Phys D: Appl Phys, 2018, 51(43): 434001 doi: 10.1088/1361-6463/aad6f8[14] Lue H T, Hu H W, Hsu T H, et al. Design of computing-in-memory (CIM) with vertical split-gate flash memory for deep neural network (DNN) inference accelerator. 2021 IEEE International Symposium on Circuits and Systems (ISCAS), 2021: 1 doi: 10.1109/ISCAS51556.2021.9401723[15] Zhang X R, Huang J, Liu X P, et al. An adaptive read control voltage scheme for reliability enhancement of flash-based in-memory computing architecture for neural network. IEEE Trans Device Mater Reliab, 2024, 24(3): 422 doi: 10.1109/TDMR.2024.3429662 -

Proportional views

Wanyi Ling received her Bachelor's and Master's degrees in Materials Science from Sichuan University. She is currently pursuing her PhD in Integrated Circuit Engineering at Zhejiang University. Her research focuses on process optimization and device design of novel split-gate floating-gate memory.

Wanyi Ling received her Bachelor's and Master's degrees in Materials Science from Sichuan University. She is currently pursuing her PhD in Integrated Circuit Engineering at Zhejiang University. Her research focuses on process optimization and device design of novel split-gate floating-gate memory. Kun Ren received his PhD from the University of Chinese Academy of Sciences and his Bachelor's degree from Fudan University. He is a Senior Research Fellow and PhD Supervisor at Zhejiang University, focusing on computational lithography EDA, and embedded memory design-process co-optimization.

Kun Ren received his PhD from the University of Chinese Academy of Sciences and his Bachelor's degree from Fudan University. He is a Senior Research Fellow and PhD Supervisor at Zhejiang University, focusing on computational lithography EDA, and embedded memory design-process co-optimization. Dianyu Qi received his Ph.D. from East China University of Science and Technology in 2015. He is currently a Senior Research Fellow at the Hangzhou Global Scientific and Technological Innovation Center, Zhejiang University, China. His research focuses on novel semiconductor materials and devices.

Dianyu Qi received his Ph.D. from East China University of Science and Technology in 2015. He is currently a Senior Research Fellow at the Hangzhou Global Scientific and Technological Innovation Center, Zhejiang University, China. His research focuses on novel semiconductor materials and devices.

DownLoad:

DownLoad: