| Citation: |

Yanqing Li, Feixiong Wang, Heyi Huang, Yadong Zhang, Xiangpeng Liang, Shuang Liu, Jianshi Tang, Huaxiang Yin. A low-thermal-budget MOSFET-based reservoir computing for temporal data classification[J]. Journal of Semiconductors, 2026, 47(1): 012303. doi: 10.1088/1674-4926/25080038

****

Y Q Li, F X Wang, H Y Huang, Y D Zhang, X P Liang, S Liu, J S Tang, and H X Yin, A low-thermal-budget MOSFET-based reservoir computing for temporal data classification[J]. J. Semicond., 2026, 47(1): 012303 doi: 10.1088/1674-4926/25080038

|

A low-thermal-budget MOSFET-based reservoir computing for temporal data classification

DOI: 10.1088/1674-4926/25080038

CSTR: 32376.14.1674-4926.25080038

More Information-

Abstract

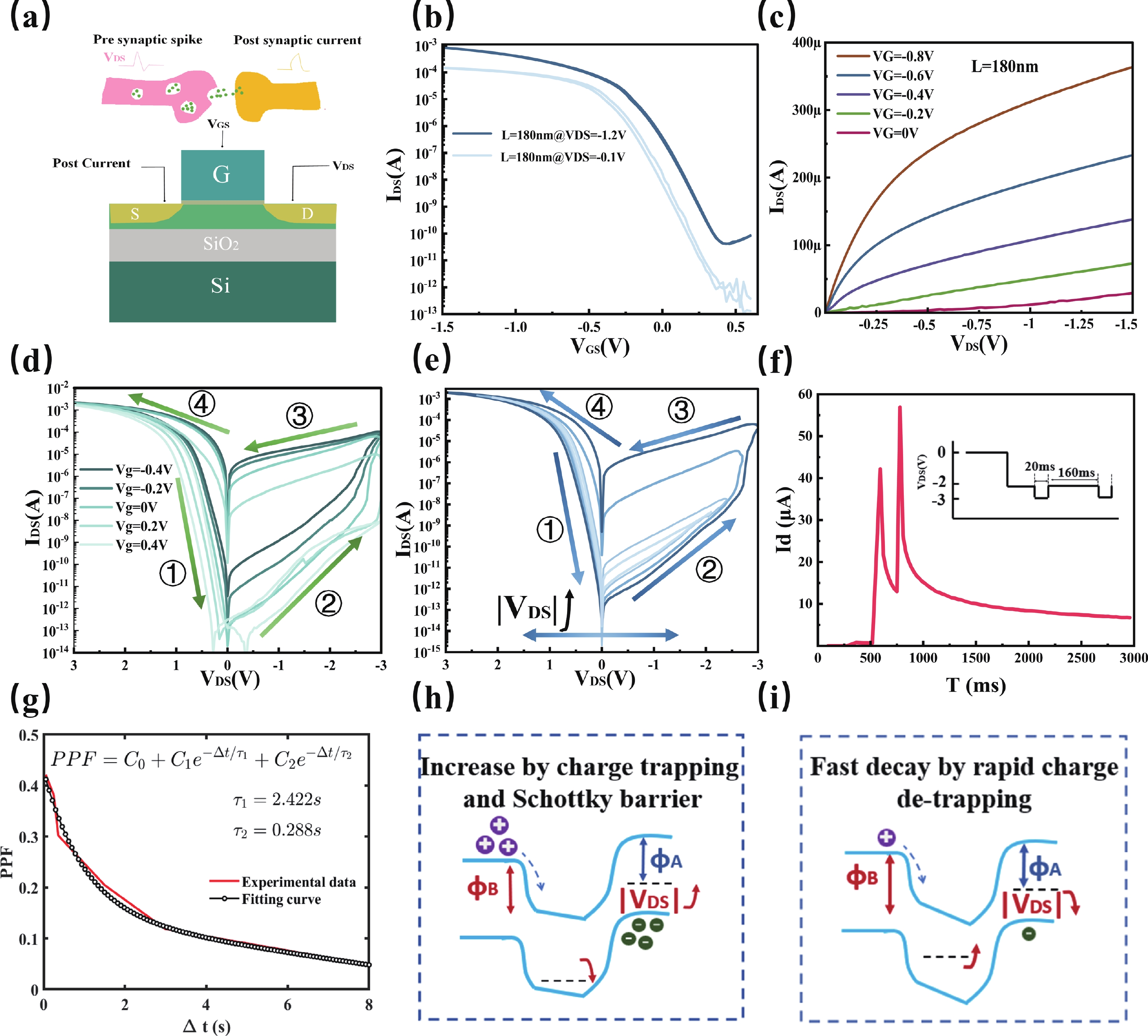

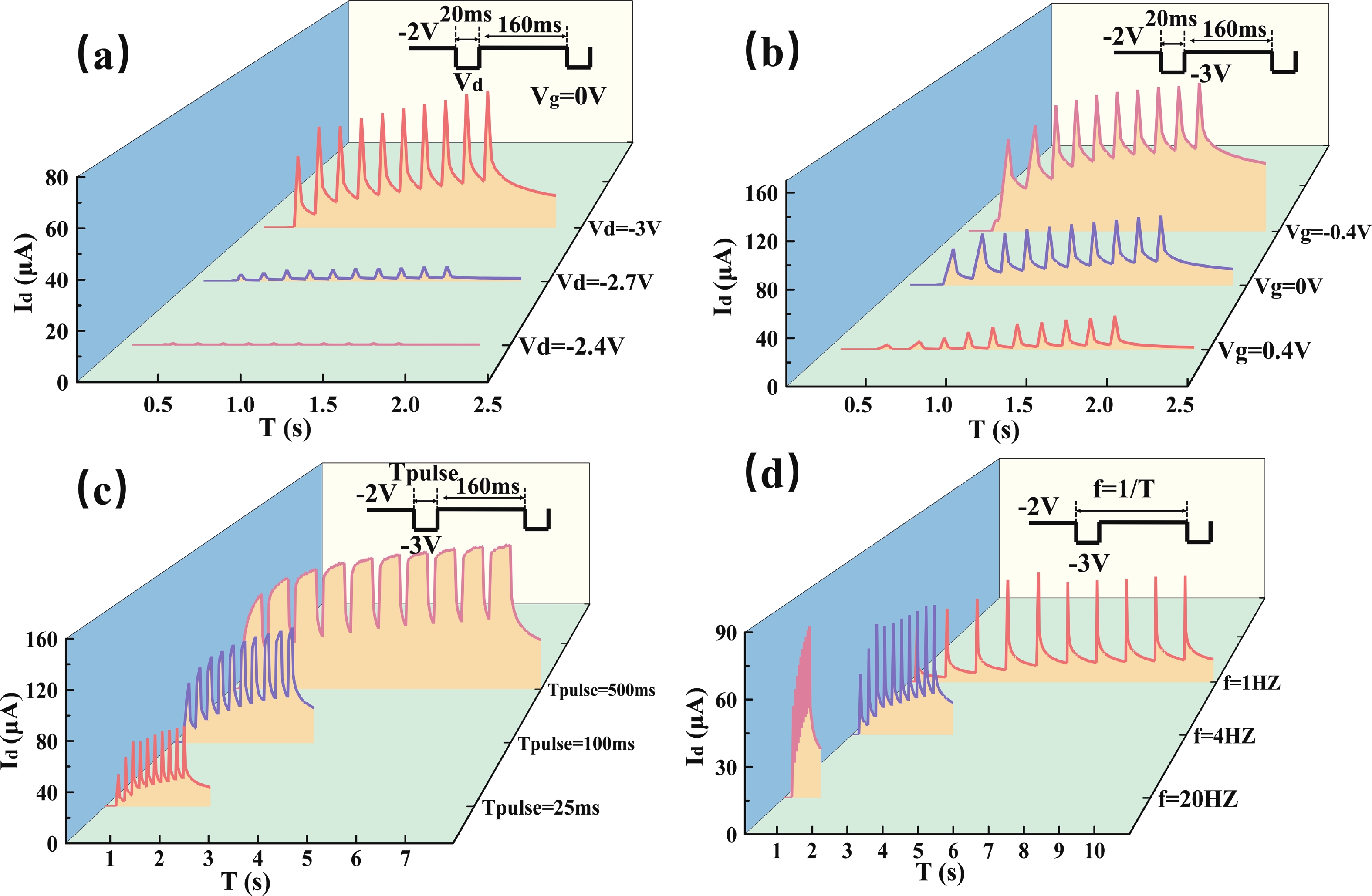

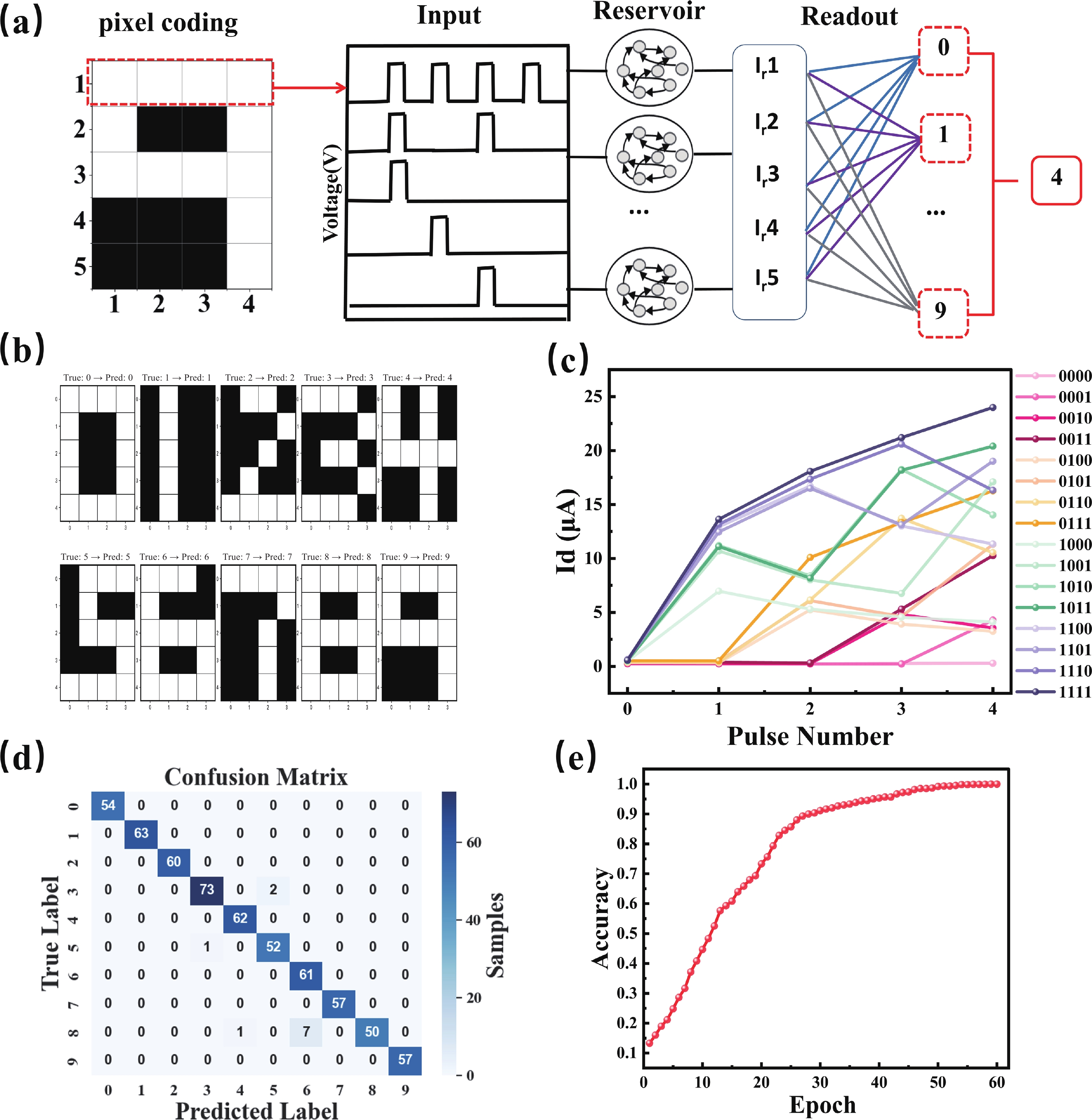

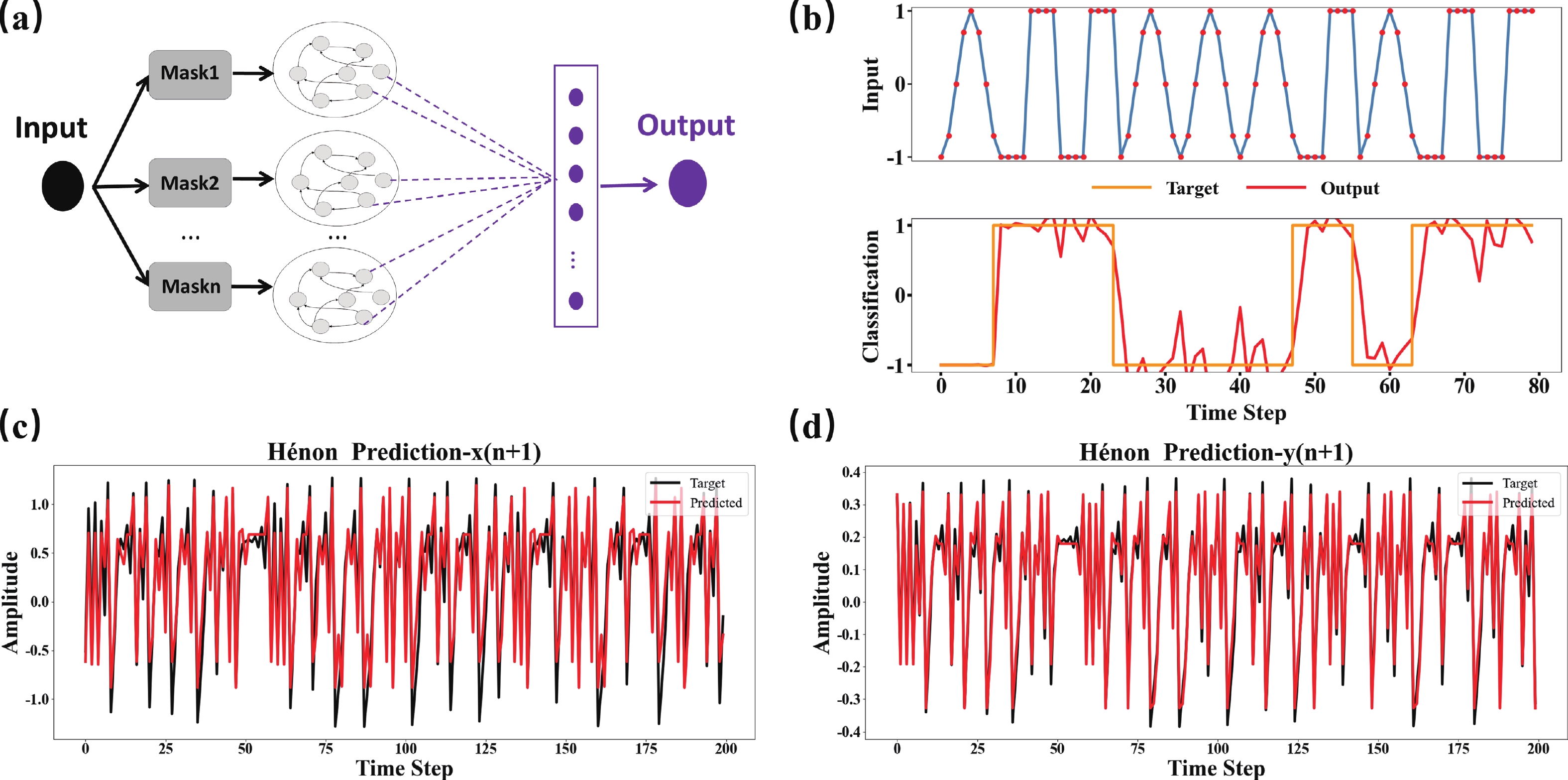

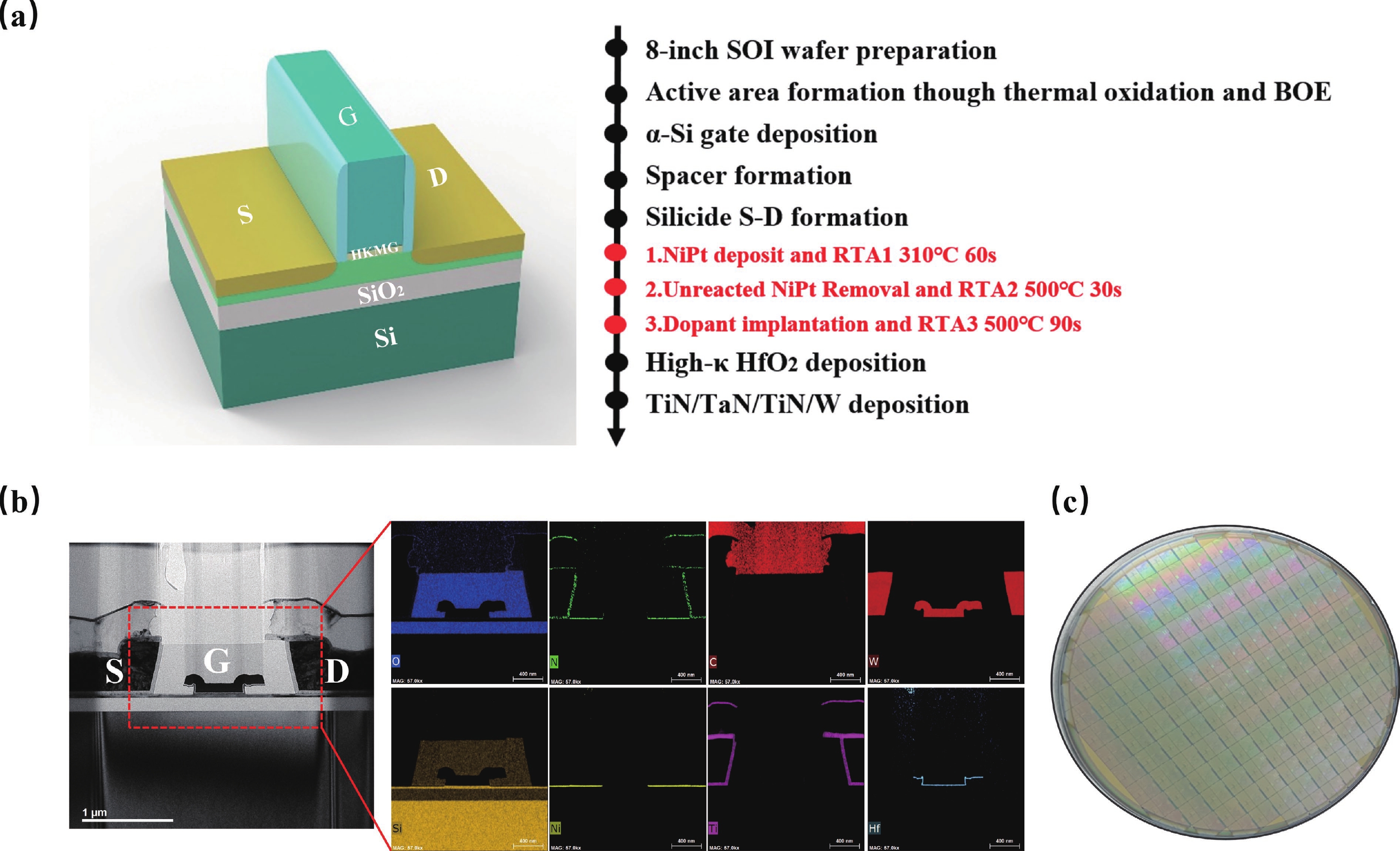

Neuromorphic devices have garnered significant attention as potential building blocks for energy-efficient hardware systems owing to their capacity to emulate the computational efficiency of the brain. In this regard, reservoir computing (RC) framework, which leverages straightforward training methods and efficient temporal signal processing, has emerged as a promising scheme. While various physical reservoir devices, including ferroelectric, optoelectronic, and memristor-based systems, have been demonstrated, many still face challenges related to compatibility with mainstream complementary metal oxide semiconductor (CMOS) integration processes. This study introduced a silicon-based schottky barrier metal−oxide−semiconductor field effect transistor (SB-MOSFET), which was fabricated under low thermal budget and compatible with back-end-of-line (BEOL). The device demonstrated short-term memory characteristics, facilitated by the modulation of schottky barriers and charge trapping. Utilizing these characteristics, a RC system for temporal data processing was constructed, and its performance was validated in a 5 × 4 digital classification task, achieving an accuracy exceeding 98% after 50 training epochs. Furthermore, the system successfully processed temporal signal in waveform classification and prediction tasks using time-division multiplexing. Overall, the SB-MOSFET's high compatibility with CMOS technology provides substantial advantages for large-scale integration, enabling the development of energy-efficient reservoir computing hardware. -

References

[1] Samuel A L. Some studies in machine learning using the game of checkers. IBM J Res Dev, 1959, 3(3): 210 doi: 10.1147/rd.33.0210[2] Gupta R S, Wood C E, Engstrom T, et al. A systematic review of quantum machine learning for digital health. NPJ Digit Med, 2025, 8(1): 237 doi: 10.1038/s41746-025-01597-z[3] Almalioglu Y, Turan M, Trigoni N, et al. Deep learning-based robust positioning for all-weather autonomous driving. Nat Mach Intell, 2022, 4(9): 749 doi: 10.1038/s42256-022-00520-5[4] Zhong Y N, Tang J S, Li X Y, et al. A memristor-based analogue reservoir computing system for real-time and power-efficient signal processing. Nat Electron, 2022, 5(10): 672 doi: 10.1038/s41928-022-00838-3[5] Lecun Y, Bottou L, Bengio Y, et al. Gradient-based learning applied to document recognition. Proc IEEE, 1998, 86(11): 2278 doi: 10.1109/5.726791[6] Mandic D P, Chambers J A. Recurrent neural networks for prediction. New York: John Wiley & Sons, 2001[7] Jaeger H. The "echo state" approach to analysing and training recurrent neural networks—with an erratum note. Bonn, Germany: German National Research Center for Information Technology GMD Technical Report, 2001: 148[8] Torrejon J, Riou M, Araujo F A, et al. Neuromorphic computing with nanoscale spintronic oscillators. Nature, 2017, 547(7664): 428 doi: 10.1038/nature23011[9] Antonik P, Duport F, Hermans M, et al. Online training of an opto-electronic reservoir computer applied to real-time channel equalization. IEEE Trans Neural Netw Learn Syst, 2017, 28(11): 2686 doi: 10.1109/TNNLS.2016.2598655[10] Lin J, Annadi, Sonde S, et al. Low-voltage artificial neuron using feedback engineered insulator-to-metal-transition devices. 2016 IEEE International Electron Devices Meeting(IEDM), 2016: 34.5.1 doi: 10.1109/IEDM.2016.7838541[11] Tuma T, Pantazi A, Le Gallo M, et al. Stochastic phase-change neurons. Nat Nanotechnol, 2016, 11(8): 693 doi: 10.1038/nnano.2016.70[12] Tanaka G, Yamane T, Héroux J B, et al. Recent advances in physical reservoir computing: A review. Neural Netw, 2019, 115: 100 doi: 10.1016/j.neunet.2019.03.005[13] Hiramoto T. Never-ending CMOS innovation: the past, present, and future perspectives. International Symposium on VLSI Technology, Systems and Applications, 2020: 3 doi: 10.1109/VLSI-TSA48913.2020.9203654[14] Zhu Y X, Mao H W, Zhu Y, et al. CMOS-compatible neuromorphic devices for neuromorphic perception and computing: A review. Int J Extrem Manuf, 2023, 5(4): 042010 doi: 10.1088/2631-7990/acef79[15] Wang F X, Zhang Y D , Bao Y J, et al. High-performance two-tier FinFETs with low-temperature (≤ 500 °C) silicide dopant segregation Schottky S-D for M3D circuits. IEEE Electron Device Lett, 2025, 46(5): 693 doi: 10.1109/LED.2025.3553873[16] Song Y, Zhou H J, Xu Q X. Source/drain technologies for the scaling of nanoscale CMOS device. Solid State Sci, 2011, 13(2): 294 doi: 10.1016/j.solidstatesciences.2010.12.002[17] Veloso A, Van Dal M J H, Collaert N, et al. Characteristics and integration challenges of FinFET-based devices for (Sub-)22nm technology nodes circuit applications. Extended abstracts of the 2009 international conference on solid state devices and materials. The Japan Society of Applied Physics, 2009: C-7-1 doi: 10.7567/SSDM.2009.C-7-1[18] Lukoševičius M. A practical guide to applying echo state networks. Neural Networks: Tricks of the Trade. Springer Berlin Heidelberg, 2012: 659 doi: 10.1007/978-3-642-35289-8_36[19] Zhang Z H, Tian G L, Huo J L, et al. Recent progress of hafnium oxide-based ferroelectric devices for advanced circuit applications. Sci China Inf Sci, 2023, 66(10): 200405 doi: 10.1007/s11432-023-3780-7[20] Nirmal K A, Kumbhar D D, Kesavan A V, et al. Advancements in 2D layered material memristors: Unleashing their potential beyond memory. NPJ 2D Mater Appl, 2024, 8(1): 83 doi: 10.1038/s41699-024-00522-4[21] Yan X D, Qian J H, Sangwan V K, et al. Progress and challenges for memtransistors in neuromorphic circuits and systems. Adv Mater, 2022, 34(48): e2108025 doi: 10.1002/adma.202108025[22] Liu K K, Li J, Li F Z, et al. A multi-terminal ion-controlled transistor with multifunctionality and wide temporal dynamics for reservoir computing. Nano Res, 2024, 17(5): 4444 doi: 10.1007/s12274-023-6343-1[23] Lukoševičius M, Jaeger H. Reservoir computing approaches to recurrent neural network training. Comput Sci Rev, 2009, 3(3): 127 doi: 10.1016/j.cosrev.2009.03.005[24] Verstraeten D, Schrauwen B, D’Haene M, et al. An experimental unification of reservoir computing methods. Neural Netw, 2007, 20(3): 391 doi: 10.1016/j.neunet.2007.04.003[25] Chen Z W, Li W J, Fan Z, et al. All-ferroelectric implementation of reservoir computing. Nat Commun, 2023, 14(1): 3585 doi: 10.1038/s41467-023-39371-y[26] Chen R Q, Yang H Z, Li R Y, et al. Thin-film transistor for temporal self-adaptive reservoir computing with closed-loop architecture. Sci Adv, 2024, 10(7): eadl1299 doi: 10.1126/sciadv.adl1299[27] Moon J, Ma W, Shin J H, et al. Temporal data classification and forecasting using a memristor-based reservoir computing system. Nat Electron, 2019, 2(10): 480 doi: 10.1038/s41928-019-0313-3[28] Appeltant L, Soriano M C, Van der Sande G, et al. Information processing using a single dynamical node as complex system. Nat Commun, 2011, 2(1): 468 doi: 10.1038/ncomms1476[29] Martinez A, Lee Y, Kim G, et al. Higher-order temporal dynamics in complementary charge trap memristor for high-dimensional reservoir computing. Adv Funct Materials, 2025: e11469 doi: 10.1002/adfm.202511469[30] Viehweg J, Poll C, Mäder P. Deterministic reservoir computing for chaotic time series prediction. Sci Rep, 2025, 15: 17695 doi: 10.1038/s41598-025-98172-z[31] Zhong Y N, Tang J S, Li X Y, et al. Dynamic memristor-based reservoir computing for high-efficiency temporal signal processing. Nat Commun, 2021, 12(1): 408 doi: 10.1038/s41467-020-20692-1[32] Liang X P, Zhong Y N, Li X Y, et al. A physical reservoir computing model based on volatile memristor for temporal signal processing. 2022 29th IEEE International Conference on Electronics, Circuits and Systems (ICECS), 2022: 1 doi: 10.1109/ICECS202256217.2022.9970880 -

Supplements

Supplementary_Information.pdf

Supplementary_Information.pdf

-

Proportional views

Yanqing Li graduated from Beijing University of Information Science and Technology in 2024 with a bachelor's degree. He is currently pursuing a master's degree at the Institute of Microelectronics, Chinese Academy of Sciences, under the supervision of Researcher Fellow Huaxiang Yin and Associate Researcher Heyi Huang. His primary research focuses on brain-inspired neuromorphic devices for three-dimensional integration.

Yanqing Li graduated from Beijing University of Information Science and Technology in 2024 with a bachelor's degree. He is currently pursuing a master's degree at the Institute of Microelectronics, Chinese Academy of Sciences, under the supervision of Researcher Fellow Huaxiang Yin and Associate Researcher Heyi Huang. His primary research focuses on brain-inspired neuromorphic devices for three-dimensional integration. Heyi Huang is currently an Associate Professor at the Institute of Microelectronics (IMECAS), Chinese Academy of Sciences (CAS). She earned her Ph.D. in Physics in 2020 from the Institute of Physics (IOP), CAS under the supervision of Academician Kui-Juan Jin, followed by postdoctoral research (2020−2023) at Tsinghua University. Her research focuses on Advanced electronic Device Integration, Neuromorphic Devices, and In-sensor Computing. Her pioneering work was recognized in China's Top 10 Semiconductor Research Advances.

Heyi Huang is currently an Associate Professor at the Institute of Microelectronics (IMECAS), Chinese Academy of Sciences (CAS). She earned her Ph.D. in Physics in 2020 from the Institute of Physics (IOP), CAS under the supervision of Academician Kui-Juan Jin, followed by postdoctoral research (2020−2023) at Tsinghua University. Her research focuses on Advanced electronic Device Integration, Neuromorphic Devices, and In-sensor Computing. Her pioneering work was recognized in China's Top 10 Semiconductor Research Advances.

DownLoad:

DownLoad: