| Citation: |

Yuhan Ding, Tiehuai Zhang, Kailei Wang, Yuanxun Zhou, Yuyang Nan, Yinan Zhou, Qian Xie, Yiming Yu, Jingzhi Zhang, Kai Kang, Zheng Wang. A compact and low-power sub-THz direct-conversion receiver with 2nd-harmonic-remixed LO chain (×9) in 28 nm CMOS technology[J]. Journal of Semiconductors, 2026, In Press. doi: 10.1088/1674-4926/26010040

****

Y H Ding, T H Zhang, K L Wang, Y X Zhou, Y Y Nan, Y N Zhou, Q Xie, Y M Yu, J Z Zhang, K Kang, and Z Wang, A compact and low-power sub-THz direct-conversion receiver with 2nd-harmonic-remixed LO chain (×9) in 28 nm CMOS technology[J]. J. Semicond., 2026, accepted doi: 10.1088/1674-4926/26010040

|

A compact and low-power sub-THz direct-conversion receiver with 2nd-harmonic-remixed LO chain (×9) in 28 nm CMOS technology

DOI: 10.1088/1674-4926/26010040

CSTR: 32376.14.1674-4926.26010040

More Information-

Abstract

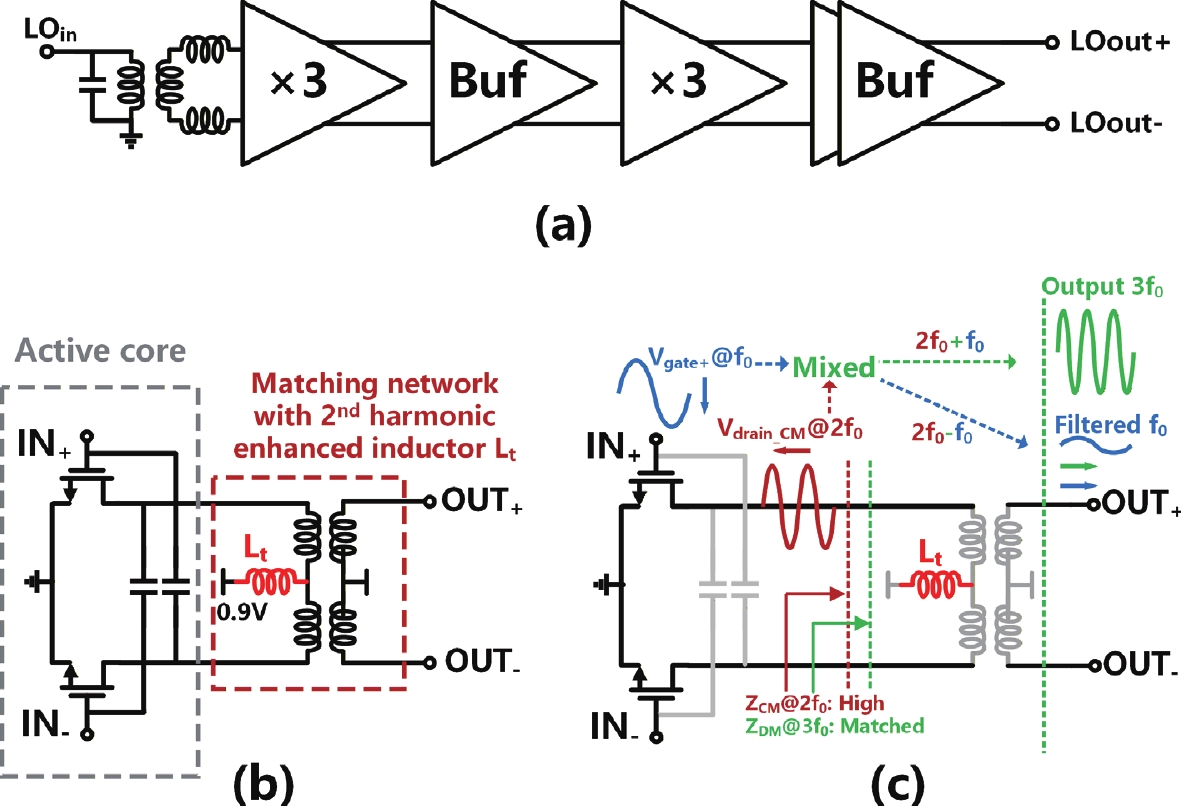

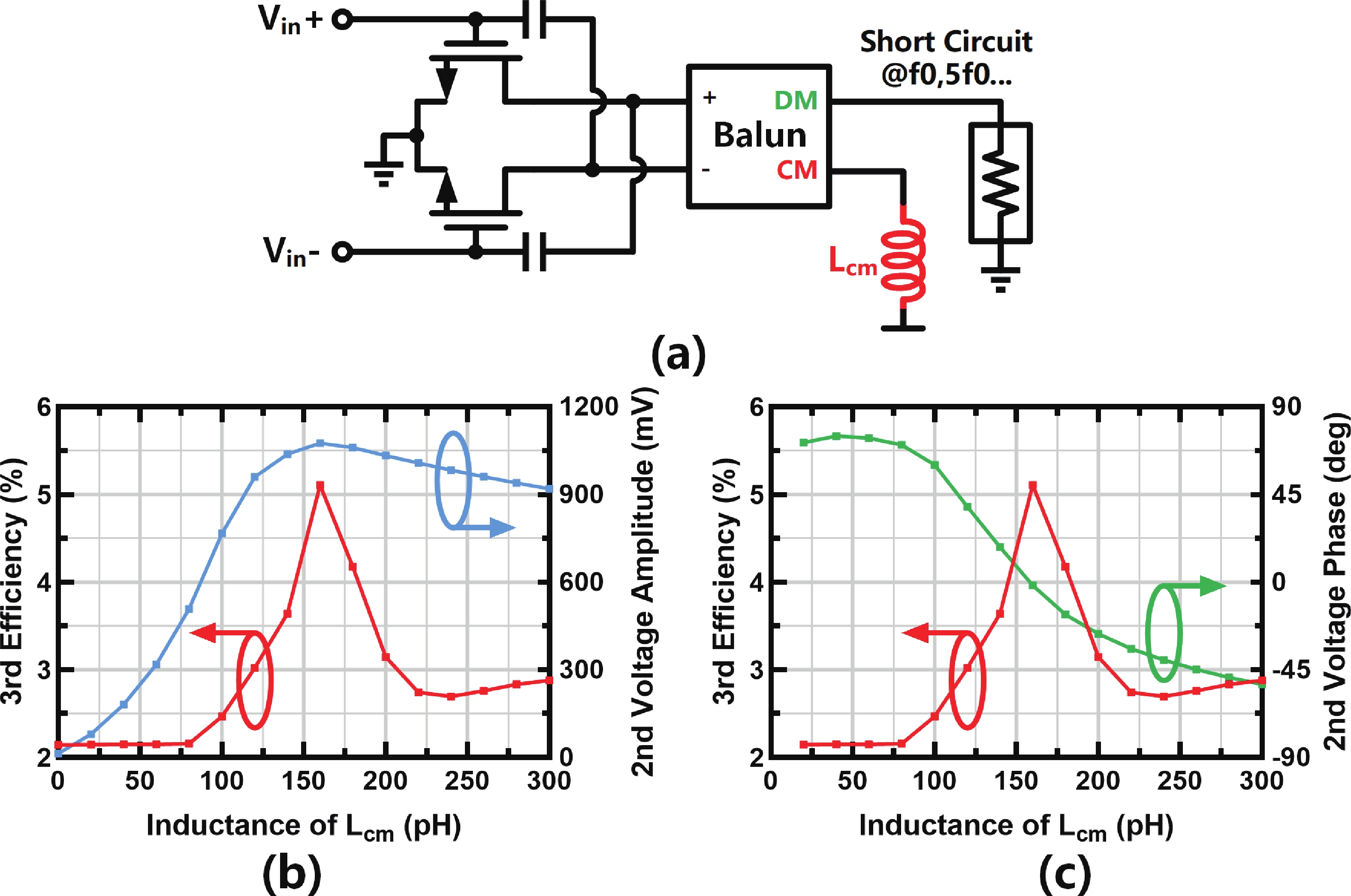

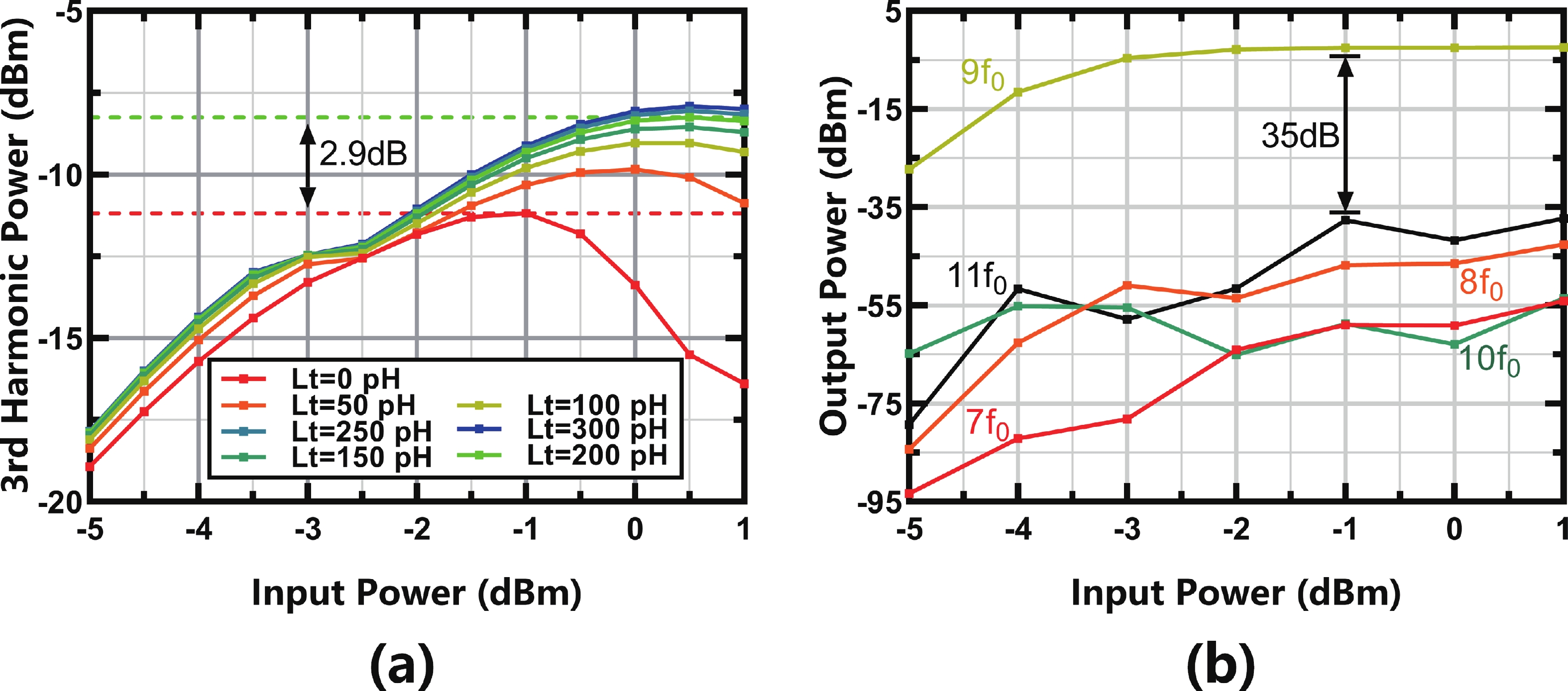

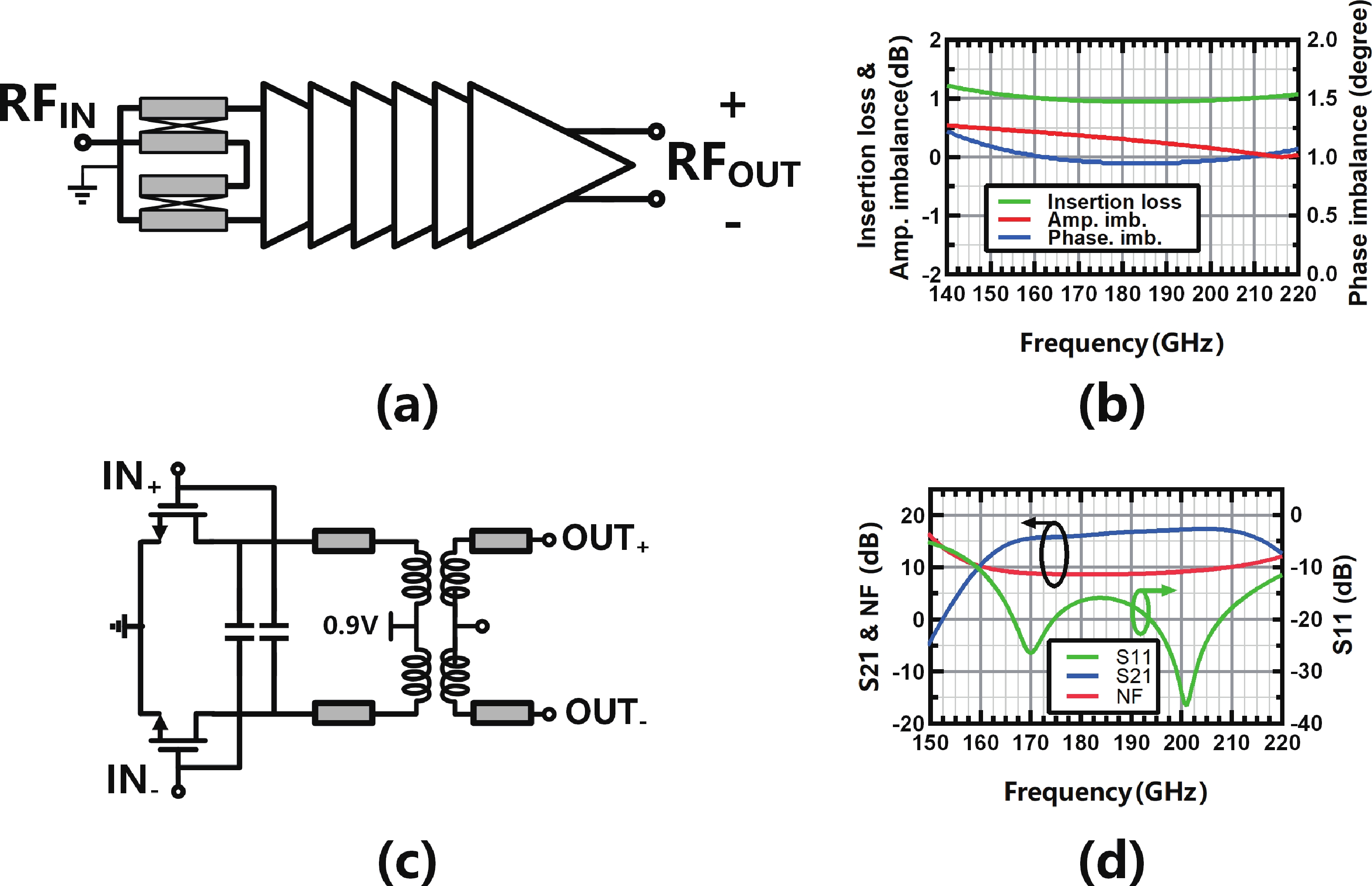

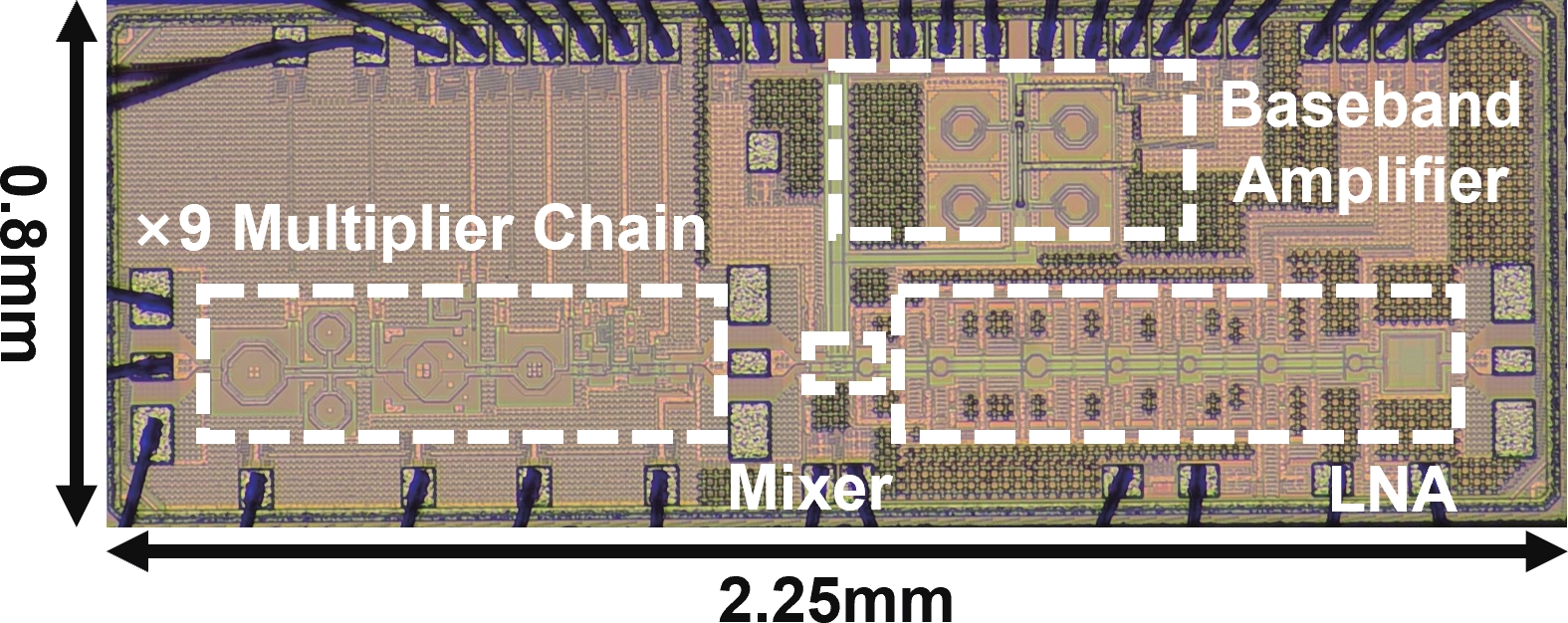

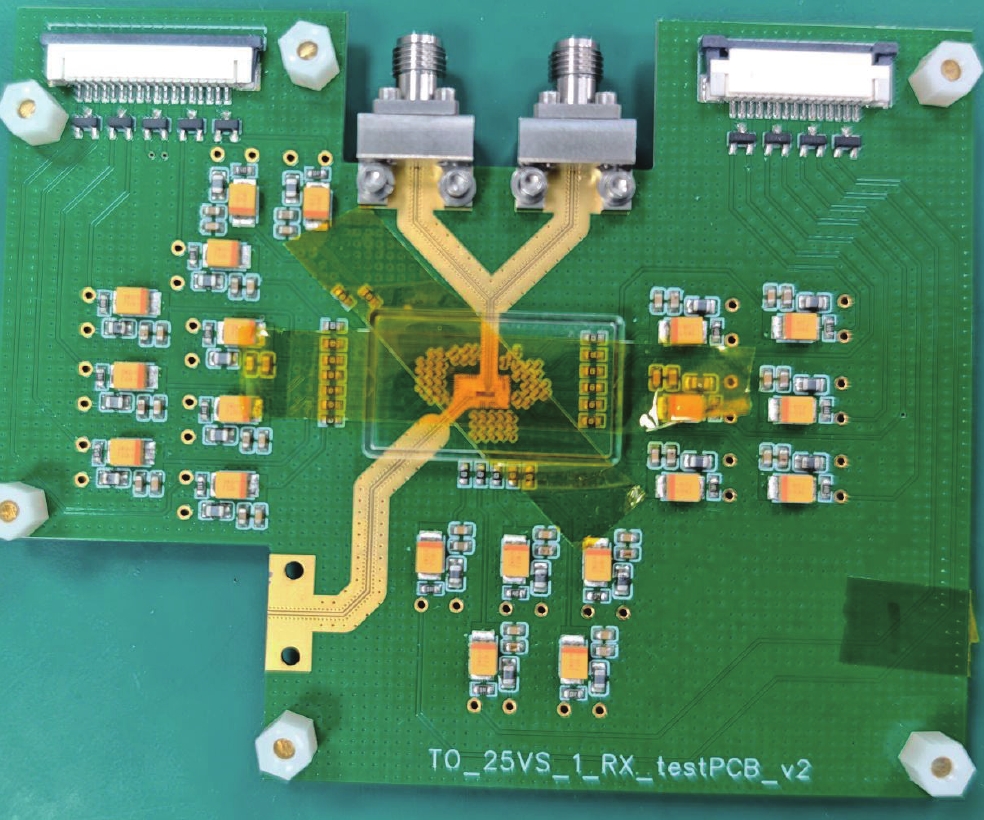

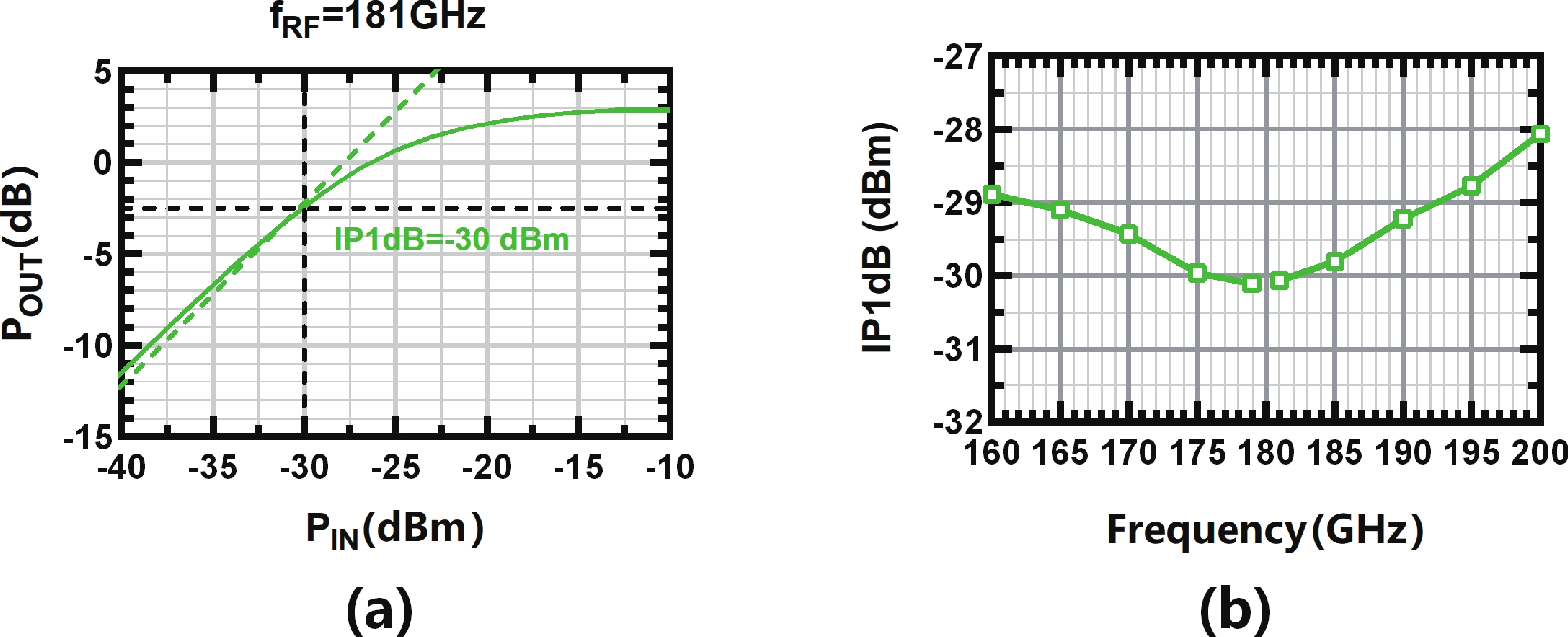

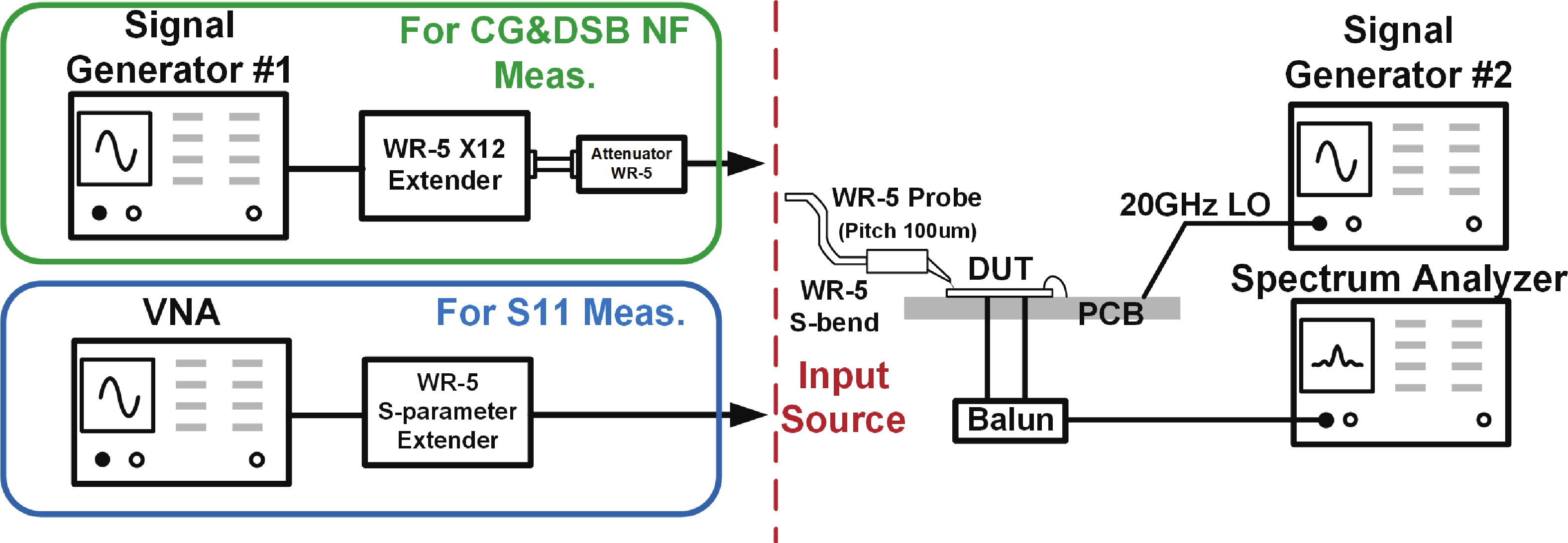

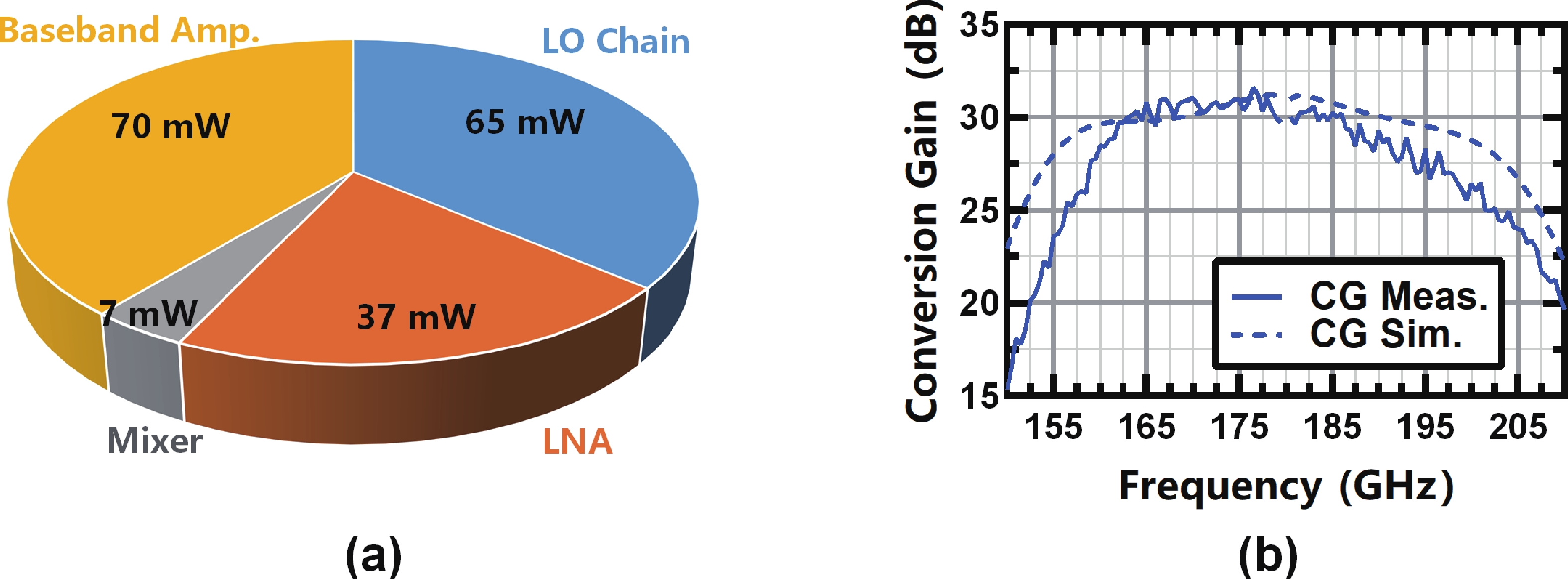

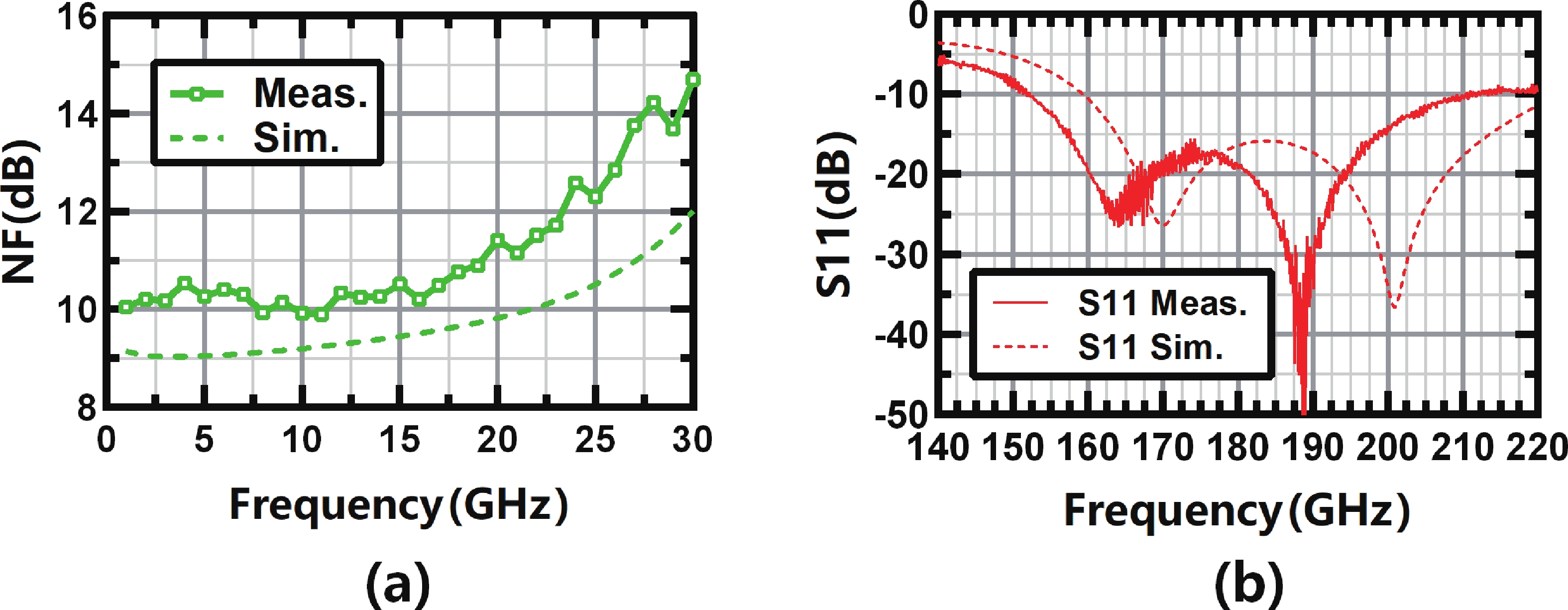

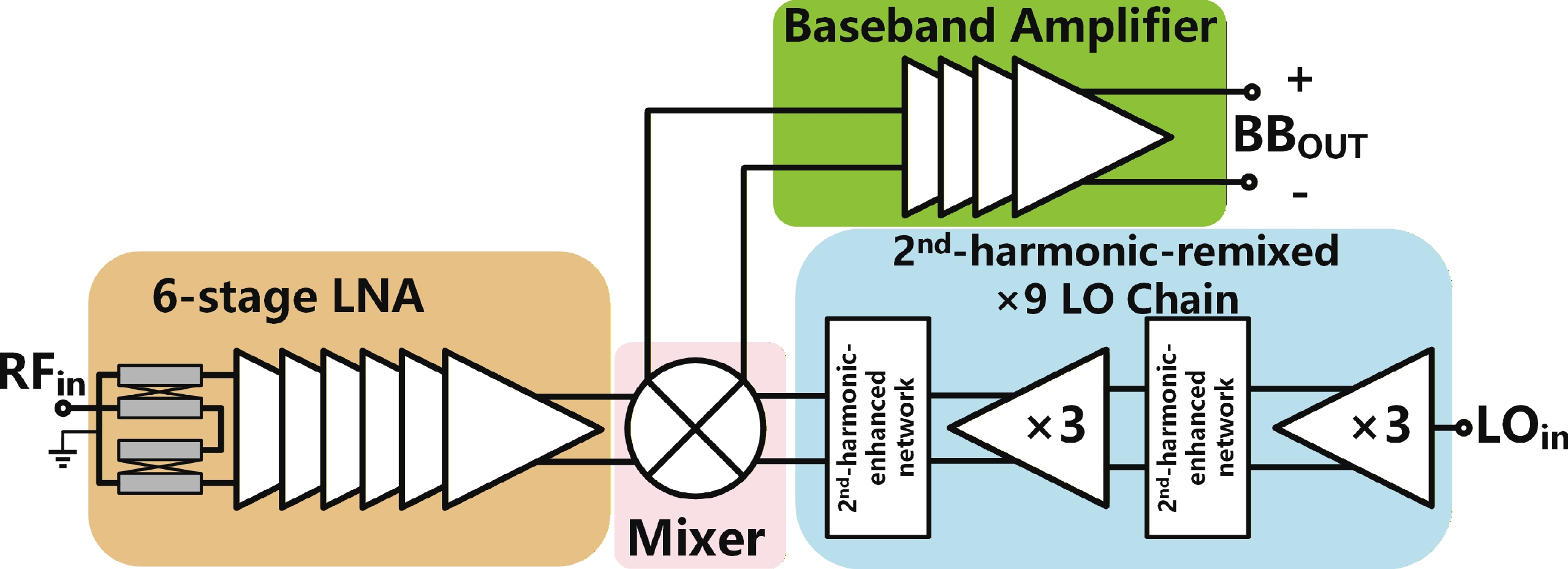

In this paper, a compact and low-power sub-THz direct-conversion receiver with a second-harmonic-remixed LO chain is proposed. Based on a common-mode second-harmonic-enhanced network, the common-mode second-harmonic voltage at the drains of the common-source differential pair in the tripler is enhanced and mixed with the fundamental voltage at the gate to generate additional differential third-harmonic voltage. Hence, the saturation output power and efficiency of the triplers used in the LO chain have been significantly improved. The power consumption of the LO chain employed in the receiver is as low as 65 mW. Measurement results demonstrate that the receiver achieves a conversion gain of 30.5 dB and a 3-dB RF bandwidth of 34 GHz, while the in-band minimum noise figure is 9.9 dB.-

Keywords:

- sub-THz,

- receiver,

- integrated circuits,

- LO chain,

- CMOS technology

-

References

[1] Anon. IEEE Std 802.15. 3TM-2023 (Revision of IEEE Std 802. 11. 3-2016) IEEE Standard for Wireless Multimedia Networks. IEEE, 2024: 1 doi: 10.1109/IEEESTD.2024.10443750[2] Chou E, Beshary H, Baniasadi N, et al. A 200 GHz wideband and low-power direct-downconversion receiver element in 16 nm FinFET technology. IEEE Solid State Circuits Lett, 2025, 8: 349 doi: 10.1109/LSSC.2025.3626442[3] Rodriguez-Vazquez P, Grzyb J, Heinemann B, et al. A QPSK 110-Gb/s polarization-diversity MIMO wireless link with a 220–255 GHz tunable LO in a SiGe HBT technology. IEEE Trans Microw Theory Tech, 2020, 68(9): 3834 doi: 10.1109/TMTT.2020.2986196[4] Eissa M H, Malignaggi A, Wang R Y, et al. Wideband 240-GHz transmitter and receiver in BiCMOS technology with 25-gbit/s data rate. IEEE J Solid State Circuits, 2018, 53(9): 2532 doi: 10.1109/JSSC.2018.2839037[5] Peng Q Y, Jia H K, Fang R, et al. A 26-Gb/s 140-GHz OOK CMOS transmitter and receiver chipset for high-speed wireless and dielectric waveguide communication. IEEE J Solid State Circuits, 2025, 60(6): 1985 doi: 10.1109/JSSC.2024.3483818[6] Tang D W, Li Z K, Huang L Y, et al. A 110-160 GHz ASK receiver with isomorphic low noise power amplifier and multi-mode interface in 28-nm CMOS. 2023 IEEE Asian Solid-State Circuits Conference (A-SSCC), 2023: 1 doi: 10.1109/A-SSCC58667.2023.10348003[7] Wang Z, Chiang P Y, Nazari P, et al. A CMOS 210-GHz fundamental transceiver with OOK modulation. IEEE J Solid State Circuits, 2014, 49(3): 564 doi: 10.1109/JSSC.2013.2297415[8] Li Z K, Chen J X, Li H B, et al. A 220-GHz sliding-IF quadrature transmitter and receiver chipset for high data rate communication in 0.13-µm SiGe BiCMOS. IEEE J Solid State Circuits, 2023, 58(7): 1913 doi: 10.1109/JSSC.2023.3236621[9] Wu W P, Bao X, Chen S, et al. A CMOS 228-324GHz RF domain quadrature receiver with a broadband harmonic-enhanced LO generator. 2025 IEEE Custom Integrated Circuits Conference (CICC), 2025: 1 doi: 10.1109/CICC63670.2025.10982973[10] Chen X B, Yi X, Khan M I W, et al. A 140-GHz FMCW TX/RX-antenna-sharing transceiver with low-inherent-loss duplexing and adaptive self-interference cancellation. IEEE J Solid State Circuits, 2022, 57(12): 3631 doi: 10.1109/JSSC.2022.3202814[11] Jeon H R, Yun B H, Lee H K, et al. A 250-GHz wideband direct-conversion CMOS receiver adopting baseband equalized low-loss resistive passive mixer. IEEE Trans Circuits Syst II Express Briefs, 2023, 70(10): 3852 doi: 10.1109/tcsii.2023.3289215[12] Wang L J, Shen Y Z, Ding Y F, et al. A 220-GHz low-noise CMOS receiver utilizing noise cancellation and gain enhancement. IEEE Trans Microw Theory Tech, 2025, 73(12): 10465 doi: 10.1109/TMTT.2025.3602475[13] Abdo I, da Gomez C, Wang C, et al. A bi-directional 300-GHz-band phased-array transceiver in 65-nm CMOS with outphasing transmitting mode and LO emission cancellation. IEEE J Solid State Circuits, 2022, 57(8): 2292 doi: 10.1109/JSSC.2022.3179166[14] Liu C X, Li Z, Yamazaki Y, et al. A 640-Gb/s 4 × 4-MIMO D-band CMOS transceiver chipset. IEEE J Solid State Circuits, 2025, 60(4): 1132 doi: 10.1109/JSSC.2024.3515640[15] Fu J H, Qin P, Wu L. A 32-QAM 50-gbps D-band receiver RF front-end with IF bandwidth extension. IEEE Trans Circuits Syst II Express Briefs, 2025, 72(12): 1982 doi: 10.1109/tcsii.2025.3629972[16] Liu M, Cai Z T, Liu J, et al. Exploration of high-speed 3.0 THz imaging with a 65 nm CMOS process. J Semicond, 2023, 44(10): 102401 doi: 10.1088/1674-4926/44/10/102401[17] Wang Y, Xu H T. Millimeter-wave PA design techniques in ISSCC 2024. J Semicond, 2024, 45(4): 040205 doi: 10.1088/1674-4926/45/4/040205[18] D’heer C, Reynaert P. A fully integrated 135-GHz direct-digital 16-QAM wireless and dielectric waveguide link in 28-nm CMOS. IEEE J Solid State Circuits, 2024, 59(3): 889 doi: 10.1109/JSSC.2023.3311673[19] Yoo J, Hong S. An efficient V-band frequency tripler with back-to-back connected varactors. IEEE Microw Wirel Technol Lett, 2023, 33(8): 1219 doi: 10.1109/LMWT.2023.3274663[20] Li S Y, Chen W H, Li X C, et al. A 5.1 dBm 127–162 GHz frequency sextupler with broadband compensated transformer-based baluns in 22nm FD-SOI CMOS. 2022 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), 2022: 315 doi: 10.1109/RFIC54546.2022.9863124[21] Shin D J, Choi U G, Yang J R. High-power V-band CMOS frequency tripler with efficient matching networks. IEEE Microw Wirel Compon Lett, 2021, 31(8): 1020 doi: 10.1109/LMWC.2021.3088860[22] Dong R B, Hara S, Watanabe I, et al. A 213-233 GHz × 9 frequency multiplier chain with 4.1 dBm output power in 40nm bulk CMOS. 2021 IEEE MTT-S International Microwave Symposium (IMS), 2021: 458 doi: 10.1109/IMS19712.2021.9574846[23] Ding Y F, Shen Y Z, Lin Z, et al. A 192–229 GHz frequency tripler with 4.4 dBm output power using slotline-based drain harmonic shaping technique in 40nm CMOS. 2024 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), 2024: 159 doi: 10.1109/RFIC61187.2024.10600043[24] Liao X F, Zhao D X, You X H. An E-band CMOS frequency quadrupler with 1.7-dBm output power and 45-dB fundamental suppression. J Semicond, 2022, 43(9): 092401 doi: 10.1088/1674-4926/43/9/092401[25] Liu X Z, Liu Z C, Han F, et al. A 7.2–16 GHz 50%-LO receiver with enhanced linearity and high dynamic range in 55-nm CMOS. IEEE Trans Circuits Syst II, 2025, 72(11): 1690 doi: 10.1109/tcsii.2025.3614156[26] Liao R L, Wang H R, Zhang J Z, et al. A 15/30/60-GHz 1TX/4RX radar chipset achieving 6° angular resolution using frequency dimension for virtual aperture expansion. 2025 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), 2025: 395 doi: 10.1109/RFIC61188.2025.11082860[27] Zheng S D, Li Z K, Zhou P G, et al. A 300-GHz upconverter with 0-dBm psat and 44-GHz bandwidth in 130-nm SiGe BiCMOS. IEEE Microw Wirel Technol Lett, 2023, 33(12): 1646 doi: 10.1109/LMWT.2023.3322938[28] Keum W, Lee J, Choi M, et al. A 115.6–156.1-GHz wideband low-noise amplifier in 65-nm CMOS technology. IEEE Microw Wireless Tech Lett, 2025, 35(11): 1792 doi: 10.1109/LMWT.2025.3595372[29] He F, Ni M H, Xie Q, et al. Analyze the loss utilization in near- fmax embedded amplifiers using uniform 3-D gain space: The super-gain-boosting technique. IEEE Trans Microw Theory Tech, 2024, 72(5): 2745 doi: 10.1109/TMTT.2024.3365088[30] Zhang X, Liu Z H, Meng F Y. A 203-to-250GHz staggered-tuning amplifier in 0.13-μm SiGe technology. IEEE Microw Wirel Technol Lett, 2025, 35(7): 1049 doi: 10.1109/LMWT.2025.3560671[31] Xu Z C, Ni M H, Xie Q, et al. Collaborative gain and noise optimization: A design of 150–173-GHz cascode LNA with 22.3 dB gain and 6.92 dB NF based on the gain-noise plane. Sci China Inf Sci, 2023, 66(10): 209401 doi: 10.1007/s11432-022-3622-1[32] Wu W X, Liu B K, He P, et al. A W-band GSG probe fabricated by metal additive manufacturing. IEEE Trans Instrum Meas, 2022, 71: 8006610 doi: 10.1109/tim.2022.3214278 -

Proportional views

Yuhan Ding was born in Pingxiang, Jiangxi, China, in 1999. He received the B.E. degrees in microelectronic science and technology from the University of Electronic Science and Technology of China, Chengdu, China, in 2021, where he is currently pursuing the Ph.D. degree in electronic science and technology with the Smart Integrated Circuits and System Laboratory (SICS). His current research interests include sub-THz transceiver and building blocks.

Yuhan Ding was born in Pingxiang, Jiangxi, China, in 1999. He received the B.E. degrees in microelectronic science and technology from the University of Electronic Science and Technology of China, Chengdu, China, in 2021, where he is currently pursuing the Ph.D. degree in electronic science and technology with the Smart Integrated Circuits and System Laboratory (SICS). His current research interests include sub-THz transceiver and building blocks. Qian Xie received the B.S. degree from the University of Electronic Science and Technology of China (UESTC), Chengdu, China, in 2007, and the Ph.D. degree in microelectronics from Tsinghua University, Beijing, China, in 2013. She is currently an Associate Professor with UESTC. Her research interests include silicon based device modeling and circuit design.

Qian Xie received the B.S. degree from the University of Electronic Science and Technology of China (UESTC), Chengdu, China, in 2007, and the Ph.D. degree in microelectronics from Tsinghua University, Beijing, China, in 2013. She is currently an Associate Professor with UESTC. Her research interests include silicon based device modeling and circuit design. Zheng Wang received the B.S. and M.S. degrees from Tsinghua University, Beijing, China, in 2007 and 2010, respectively, and the Ph.D. degree in electrical engineering from the University of California-Irvine, CA, USA, in 2014. From 2014 to 2017, he was with Qualcomm Inc., San Diego, USA, working on RFIC design for cellular application. In 2017, he joined the University of Electronic Science and Technology of China, Chengdu, China, as a Professor. His research interests include the design of novel radio frequency, millimeter wave, and terahertz silicon-based integrated circuits for the next-generation 10-Gb wireless communications as well as imaging systems.

Zheng Wang received the B.S. and M.S. degrees from Tsinghua University, Beijing, China, in 2007 and 2010, respectively, and the Ph.D. degree in electrical engineering from the University of California-Irvine, CA, USA, in 2014. From 2014 to 2017, he was with Qualcomm Inc., San Diego, USA, working on RFIC design for cellular application. In 2017, he joined the University of Electronic Science and Technology of China, Chengdu, China, as a Professor. His research interests include the design of novel radio frequency, millimeter wave, and terahertz silicon-based integrated circuits for the next-generation 10-Gb wireless communications as well as imaging systems.

DownLoad:

DownLoad: