Article Navigation >

Journal of Semiconductors

>

2026

> Uncorrected proof

| Citation: |

Junyan Bi, Hao Xu, Na Yan. Multi-phase clock generation techniques toward high-frequency and wideband applications[J]. Journal of Semiconductors, 2026, In Press. doi: 10.1088/1674-4926/26020027

****

J Y Bi, H Xu, and N Yan, Multi-phase clock generation techniques toward high-frequency and wideband applications[J]. J. Semicond., 2026, 47(5): 050202 doi: 10.1088/1674-4926/26020027

|

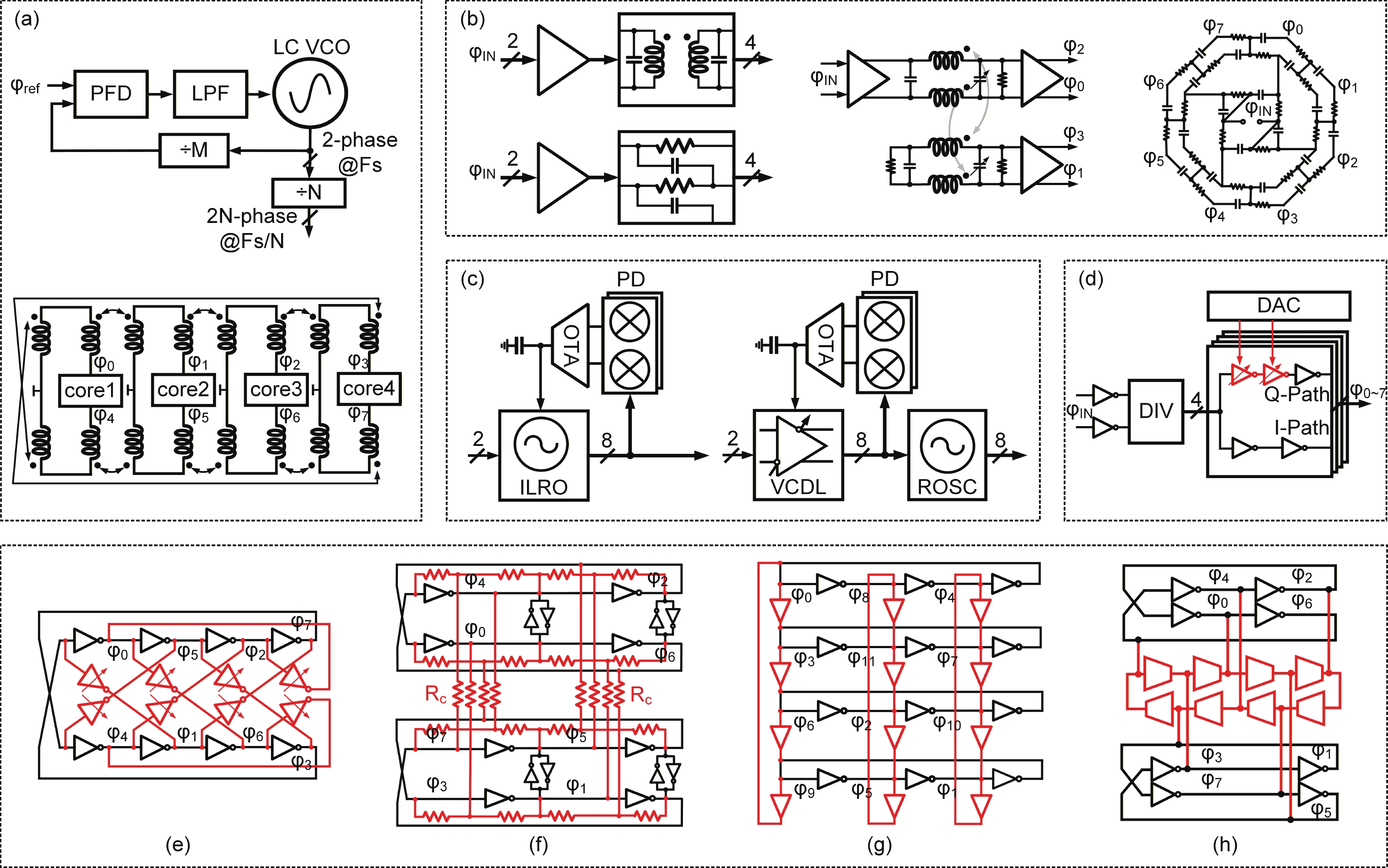

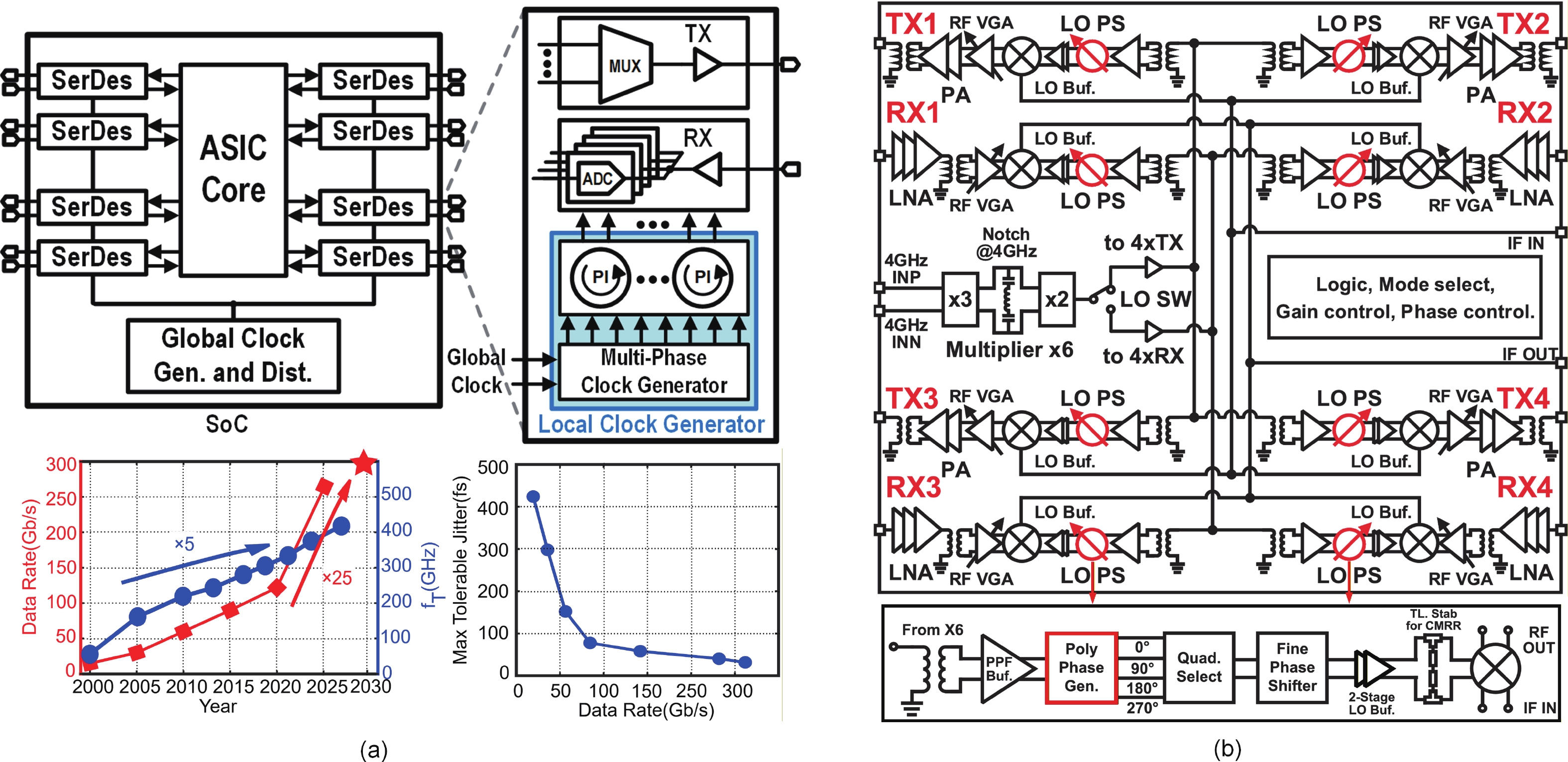

Multi-phase clock generation techniques toward high-frequency and wideband applications

DOI: 10.1088/1674-4926/26020027

CSTR: 32376.14.1674-4926.26020027

More Information-

References

[1] Chen E H, Park H, Abdullatif M, et al. A 212.5Gb/s DSP-based PAM-4 transceiver with 50dB loss compensation for large AI system interconnects in 4nm FinFET. 2025 IEEE International Solid-State Circuits Conference (ISSCC), 2025: 1 doi: 10.1109/ISSCC49661.2025.10904601[2] Mostafa A, Hassan A, Hsu A, et al. A 2.2pJ/b 212.5Gb/s PAM-4 transceiver with >46dB reach in 5nm FinFET. 2025 IEEE Int Solid-State Circuits Conference (ISSCC), 2025: 138 doi: 10.1109/ISSCC49661.2025.10904591[3] Pang J, Wu R, Wang Y, et al. A 28-GHz CMOS phased-array transceiver based on LO phase-shifting architecture with gain invariant phase tuning for 5G new radio. IEEE J Solid State Circuits, 2019, 54(5): 1228 doi: 10.1109/JSSC.2019.2899734[4] Wang Y, Wu R, Pang J, et al. A 39-GHz 64-element phased-array transceiver with built-In phase and amplitude calibrations for large-array 5G NR in 65-nm CMOS. IEEE J Solid State Circuits, 2020, 55(5): 1249 doi: 10.1109/JSSC.2020.2980509[5] Zhao Y, Fan C, Fang Q Y, et al. A 0.07 mm2 20-to-23.8GHz 8-phase oscillator incorporating magnetic + dual-injection coupling achieving 189.2dBc/Hz FoM@10 MHz and 200.7dBc/Hz FoMA in 65nm CMOS. 2024 IEEE International Solid-State Circuits Conference (ISSCC), 2024: 354 doi: 10.1109/ISSCC49657.2024.10454464[6] Li C, Guo J H, Qin P, et al. A wideband mode-switching quad-core VCO using compact multi-mode magnetically coupled LC network. IEEE J Solid State Circuits, 2023, 58(7): 1959 doi: 10.1109/JSSC.2023.3235347[7] Chen X, Hu Y Z, Siriburanon T, et al. A 30-GHz class-F quadrature DCO using phase shifts between drain–gate–source for low flicker phase noise and I/Q exactness. IEEE J Solid State Circuits, 2023, 58(7): 1945 doi: 10.1109/JSSC.2023.3237788[8] Huang M Y, Chi T Y, Li S S, et al. A 24.5–43.5-GHz ultra-compact CMOS receiver front end with calibration-free instantaneous full-band image rejection for multiband 5G massive MIMO. IEEE J Solid State Circuits, 2020, 55(5): 1177 doi: 10.1109/JSSC.2019.2959495[9] Krishnamurthy S, Iotti L, Niknejad A M. Design of high-linearity mixer-first receivers for mm-wave digital MIMO arrays. IEEE J Solid State Circuits, 2021, 56(11): 3375 doi: 10.1109/JSSC.2021.3101984[10] Chen W C, Wen C H, Fu C M, et al. A 4-to-18GHz active poly phase filter quadrature clock generator with phase error correction in 5nm CMOS. 2020 IEEE Symposium on VLSI Circuits, 2020, 1: 1 doi: 10.1109/VLSICircuits18222.2020.9162794[11] Rahman M, Elbadry M, Harjani R. An IEEE 802.15. 6 standard compliant 2.5 nJ/bit multiband WBAN transmitter using phase multiplexing and injection locking. IEEE J Solid State Circuits, 2015, 50(5): 1126 doi: 10.1109/JSSC.2015.2402214[12] Mirzaei A, Heidari M E, Bagheri R, et al. Multi-phase injection widens lock range of ring-oscillator-based frequency dividers. IEEE J Solid State Circuits, 2008, 43(3): 656 doi: 10.1109/JSSC.2007.916602[13] Raj M, Saeedi S, Emami A. A 4-to-11GHz injection-locked quarter-rate clocking for an adaptive 153fJ/b optical receiver in 28nm FDSOI CMOS. 2015 IEEE International Solid-State Circuits Conference (ISSCC), 2015: 1 doi: 10.1109/ISSCC.2015.7063097[14] Monaco E, Anzalone G, Albasini G, et al. 2–11 GHz 7-bit high-linearity phase rotator based on wideband injection-locking multi-phase generation for high-speed serial links in 28-nm CMOS FDSOI. IEEE J Solid State Circuits, 2017, 52(7): 1739 doi: 10.1109/JSSC.2017.2702742[15] Chen S, Zhou L, Zhuang I, et al. A 4-to-16GHz inverter-based injection-locked quadrature clock generator with phase interpolators for multi-standard I/Os in 7nm FinFET. 2018 IEEE International Solid-State Circuits Conference (ISSCC), 2018: 390 doi: 10.1109/ISSCC.2018.8310348[16] Wang Z W, Zhang Y D, Onizuka Y, et al. Multi-phase clock generation for phase interpolation with a multi-phase, injection-locked ring oscillator and a quadrature DLL. IEEE J Solid State Circuits, 2022, 57(6): 1776 doi: 10.1109/JSSC.2021.3124486[17] Tian Y C, Gu J J, He W T, et al. A 28-nm 8–28-GHz eight-phase clock generator using an injection-locked dual-feedback ring oscillator. IEEE J Solid State Circuits, 2026, 61(1): 47 doi: 10.1109/JSSC.2025.3613940[18] Kim J, Kundu S, Balankutty A, et al. A 224-Gb/s DAC-based PAM-4 quarter-rate transmitter with 8-tap FFE in 10-nm FinFET. IEEE J Solid State Circuits, 2022, 57(1): 6 doi: 10.1109/JSSC.2021.3108969[19] Song S Q, Poulton J, Chen X, et al. A 2-to-20 GHz multi-phase clock generator with phase interpolators using injection-locked oscillation buffers for high-speed IOs in 16nm FinFET. 2019 IEEE Custom Integrated Circuits Conference (CICC), 2019: 1 doi: 10.1109/CICC.2019.8780177[20] Chen X, Song S Q, Poulton J, et al. Voltage-follower coupling quadrature oscillator with embedded phase-interpolator in 16nm FinFET. 2019 IEEE Custom Integrated Circuits Conference (CICC), 2019, 1: 1 doi: 10.1109/CICC.2019.8780309 -

Proportional views

Junyan Bi received the B.S. degree in microelectronics science and engineering from Xi'an Jiaotong University, Xi'an, China, in 2022. He is currently pursuing a Ph.D. degree at Fudan University, Shanghai, China. His research interests focus on high-speed analog IC design, including radio frequency receivers and multi-phase clock generation and distribution.

Junyan Bi received the B.S. degree in microelectronics science and engineering from Xi'an Jiaotong University, Xi'an, China, in 2022. He is currently pursuing a Ph.D. degree at Fudan University, Shanghai, China. His research interests focus on high-speed analog IC design, including radio frequency receivers and multi-phase clock generation and distribution. Hao Xu received the B.S. degree in microelectronics from Fudan University, Shanghai, China, in 2010, and the M.S. and Ph.D. degrees in electrical engineering from the University of California, Los Angeles, CA, USA, in 2012 and 2018, respectively. From 2017 to 2019, he was with Broadcom Inc., Irvine, CA, USA, developing DSP-based high-speed optical transceivers. From 2019 to 2021, he was with Apple Inc., San Diego, CA, USA, developing high performance cellular RF transceivers. He held various part-time positions with Broadcom, Mediatek, and Tensorcom, during his graduate study. Since 2021, he has been an Associate Professor at Fudan University. His research interests include mixed-signal, RF, and analog integrated circuits design.

Hao Xu received the B.S. degree in microelectronics from Fudan University, Shanghai, China, in 2010, and the M.S. and Ph.D. degrees in electrical engineering from the University of California, Los Angeles, CA, USA, in 2012 and 2018, respectively. From 2017 to 2019, he was with Broadcom Inc., Irvine, CA, USA, developing DSP-based high-speed optical transceivers. From 2019 to 2021, he was with Apple Inc., San Diego, CA, USA, developing high performance cellular RF transceivers. He held various part-time positions with Broadcom, Mediatek, and Tensorcom, during his graduate study. Since 2021, he has been an Associate Professor at Fudan University. His research interests include mixed-signal, RF, and analog integrated circuits design. Na Yan received the B.S. and Ph.D. degrees from Fudan University, Shanghai, China, in 2002 and 2007, respectively. After her studies, she joined the School of Microelectronics, Fudan University, where she is currently a Full Professor. From 2011 to 2012, she was a Visiting Scholar with the University of California, Los Angeles, CA, USA, where she was involved in millimeter-wave transceiver and RF interconnect transceiver design. She has authored or coauthored over 100 refereed publications, including one chapter in RF mixed-signal circuit design resulting in more than 20 patents. Her research interests include power efficient mixed-signal circuits design for highly integrated CMOS RF systems.

Na Yan received the B.S. and Ph.D. degrees from Fudan University, Shanghai, China, in 2002 and 2007, respectively. After her studies, she joined the School of Microelectronics, Fudan University, where she is currently a Full Professor. From 2011 to 2012, she was a Visiting Scholar with the University of California, Los Angeles, CA, USA, where she was involved in millimeter-wave transceiver and RF interconnect transceiver design. She has authored or coauthored over 100 refereed publications, including one chapter in RF mixed-signal circuit design resulting in more than 20 patents. Her research interests include power efficient mixed-signal circuits design for highly integrated CMOS RF systems.

DownLoad:

DownLoad: