| Citation: |

Qing Dong, Yinyin Lin. SRAM standby leakage decoupling analysis for different leakage reduction techniques[J]. Journal of Semiconductors, 2013, 34(4): 045008. doi: 10.1088/1674-4926/34/4/045008

****

Q Dong, Y Y Lin. SRAM standby leakage decoupling analysis for different leakage reduction techniques[J]. J. Semicond., 2013, 34(4): 045008. doi: 10.1088/1674-4926/34/4/045008.

|

SRAM standby leakage decoupling analysis for different leakage reduction techniques

DOI: 10.1088/1674-4926/34/4/045008

More Information

-

Abstract

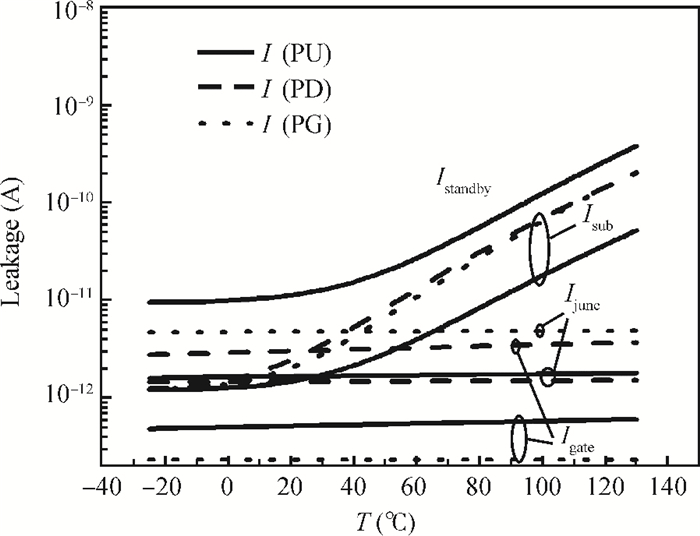

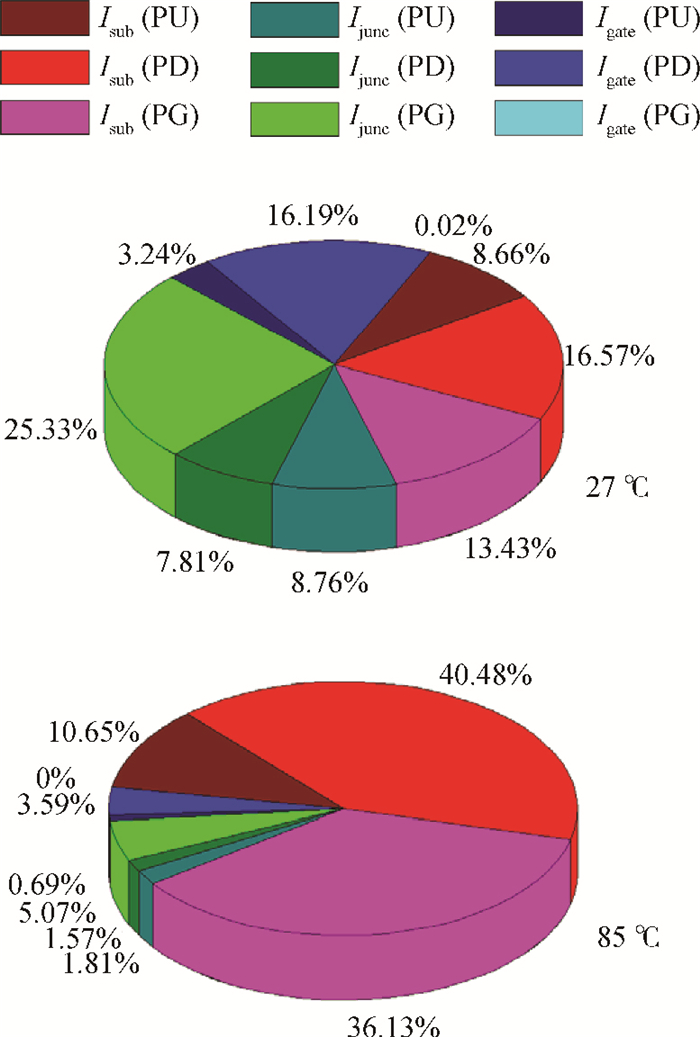

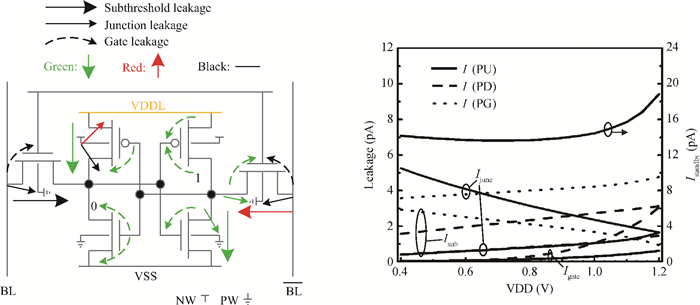

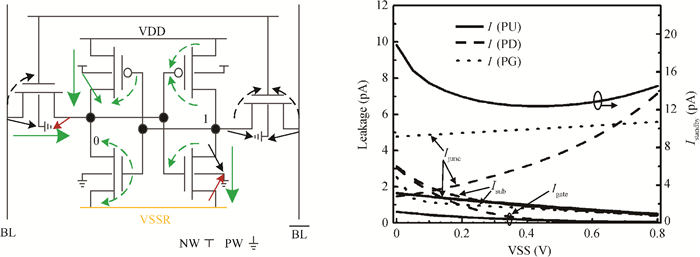

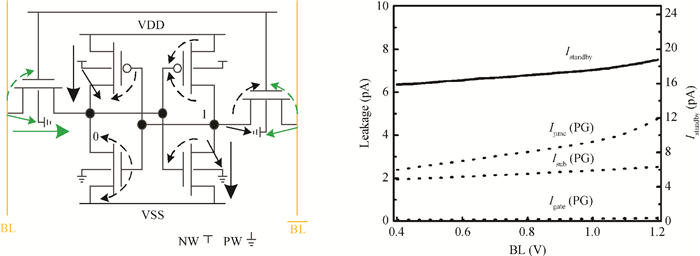

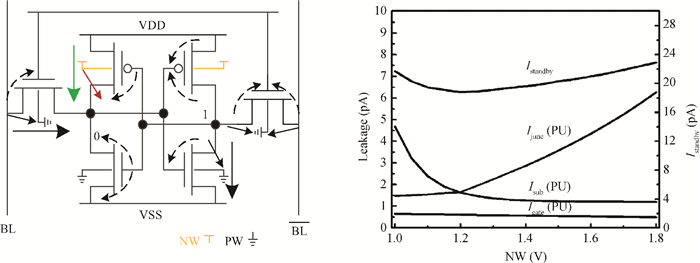

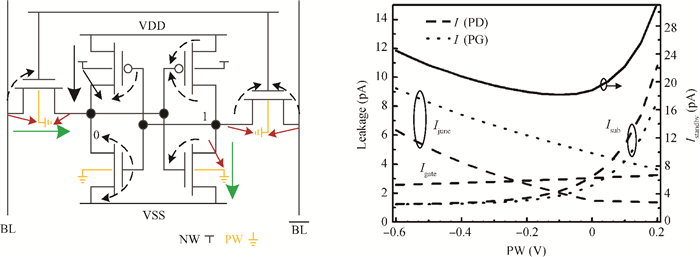

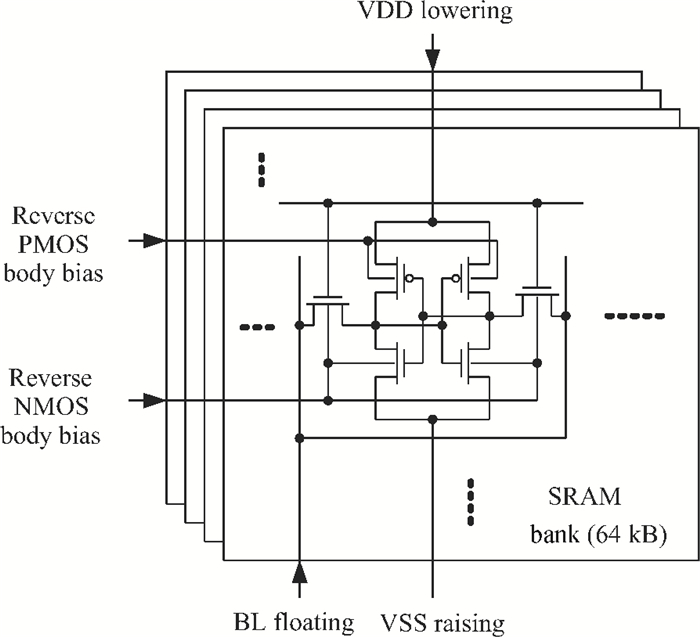

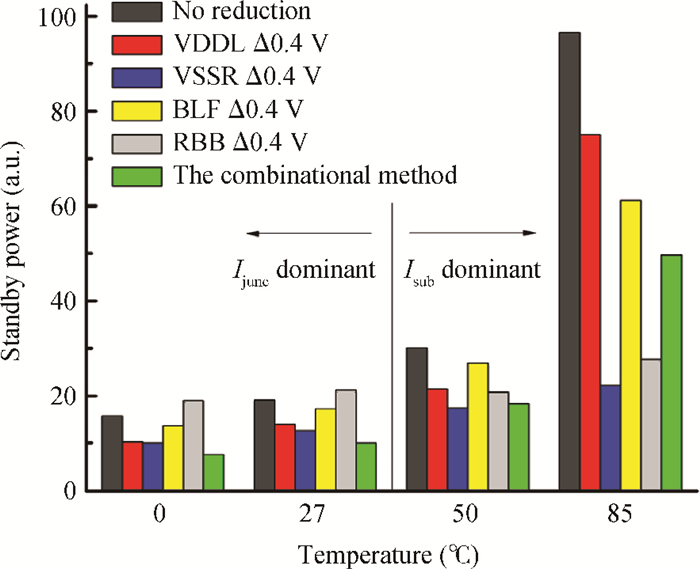

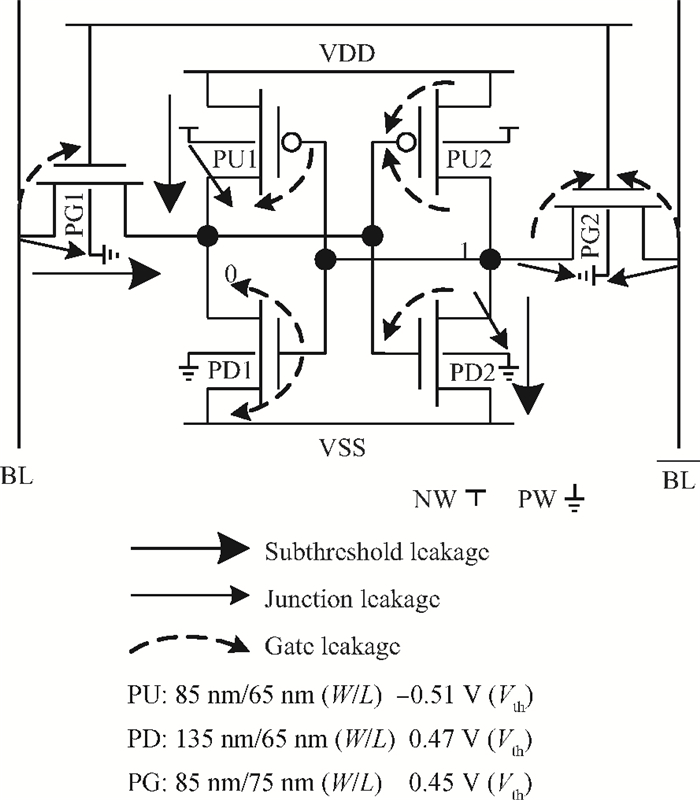

SRAM standby leakage reduction plays a pivotal role in minimizing the power consumption of application processors. Generally, four kinds of techniques are often utilized for SRAM standby leakage reduction:Vdd lowering (VDDL), Vss rising (VSSR), BL floating (BLF) and reversing body bias (RBB). In this paper, we comprehensively analyze and compare the reduction effects of these techniques on different kinds of leakage. It is disclosed that the performance of these techniques depends on the leakage composition of the SRAM cell and temperature. This has been verified on a 65 nm SRAM test macro.-

Keywords:

- SRAM,

- standby power,

- leakage reduction

-

References

[1] Lee Y, Seok M, Hanson S, et al. Standby power reduction techniques for ultra-low power processors. IEEE ESSCIRC, 2008:186 http://web.eecs.umich.edu/faculty/blaauw/images/pdfs/366.pdf[2] Kumar A, Qin H, Ishwar P, et al. Fundamental bounds on power reduction during data-retention in standby SRAM. IEEE International Symposium on Circuits and System, 2007:1867 http://ieeexplore.ieee.org/document/4253026/authors[3] Hamzaoglu F, Zhang K, Wang Y, et al. A 3.8 GHz 153 Mb SRAM design with dynamic stability enhancement and leakage reduction in 45 nm high-k metal gate CMOS technology. IEEE J Solid-State Circuits, 2009, 44(1):148 doi: 10.1109/JSSC.2008.2007151[4] Lai F, Lee C. On-chip voltage down converter to improve SRAM read/write margin and static power for sub-nano CMOS technology. IEEE J Solid-State Circuits, 2007, 42(9):2061 doi: 10.1109/JSSC.2007.903072[5] Wang Y, Bhattacharya U, Hamzaoglu F, et al. A 4.0 GHz 291 Mb voltage-scalable SRAM design in a 32 nm high-k + metal-gate CMOS technology with integrated power management. IEEE J Solid-State Circuits, 2010, 45(1):103 doi: 10.1109/JSSC.2009.2034082[6] Yamaoka M, Kawahara T. Operating-margin-improved SRAM with column-at-a-time body-bias control technique. IEEE ESSCIRC Dig, 2007:396[7] Yamaoka M, Shinozaki Y, Maeda N, et al. A 300-MHz 25-μA/Mb-leakage on-chip SRAM module featuring process-variation immunity and low-leakage-active mode for mobile-phone application processor. IEEE J Solid-State Circuits, 2005, 40(1):186 doi: 10.1109/JSSC.2004.838014[8] Lakshminarayanan S, Joung J, Narasimhan G, et al. Standby power reduction and SRAM cell optimization for 65 nm technology. IEEE International Symposium on Quality Electronic Design, 2009:471[9] Maeda N, Komatsu S, Morimoto M, et al. A 0.41μA standby leakage 32 kb embedded SRAM with low-voltage resume-standby utilizing all digital current comparator in 28 nm HKMG CMOS. IEEE VLSI Circuits Symp Dig, 2012:58[10] Hsu P K, Tang Y, Tao D, et al. A SRAM cell array with adaptive leakage reduction scheme for data retention in 28 nm high-k metal-gate CMOS. IEEE VLSI Circuits Symp Dig, 2012:62 https://www.infona.pl/resource/bwmeta1.element.ieee-art-000006243790 -

Proportional views

DownLoad:

DownLoad: