| Citation: |

Ling Yang, Guoding Dai, Chongwei Xu, Yuezhi Liu. A current-mode DC-DC buck converter with adaptive zero compensation[J]. Journal of Semiconductors, 2013, 34(8): 085012. doi: 10.1088/1674-4926/34/8/085012

****

L Yang, G D Dai, C W Xu, Y Z Liu. A current-mode DC-DC buck converter with adaptive zero compensation[J]. J. Semicond., 2013, 34(8): 085012. doi: 10.1088/1674-4926/34/8/085012.

|

A current-mode DC-DC buck converter with adaptive zero compensation

DOI: 10.1088/1674-4926/34/8/085012

More Information

-

Abstract

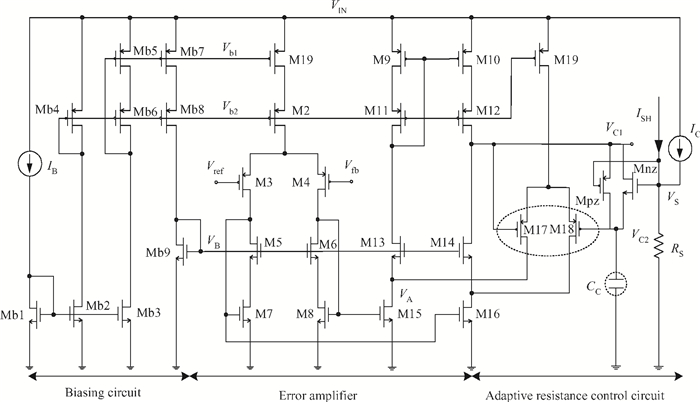

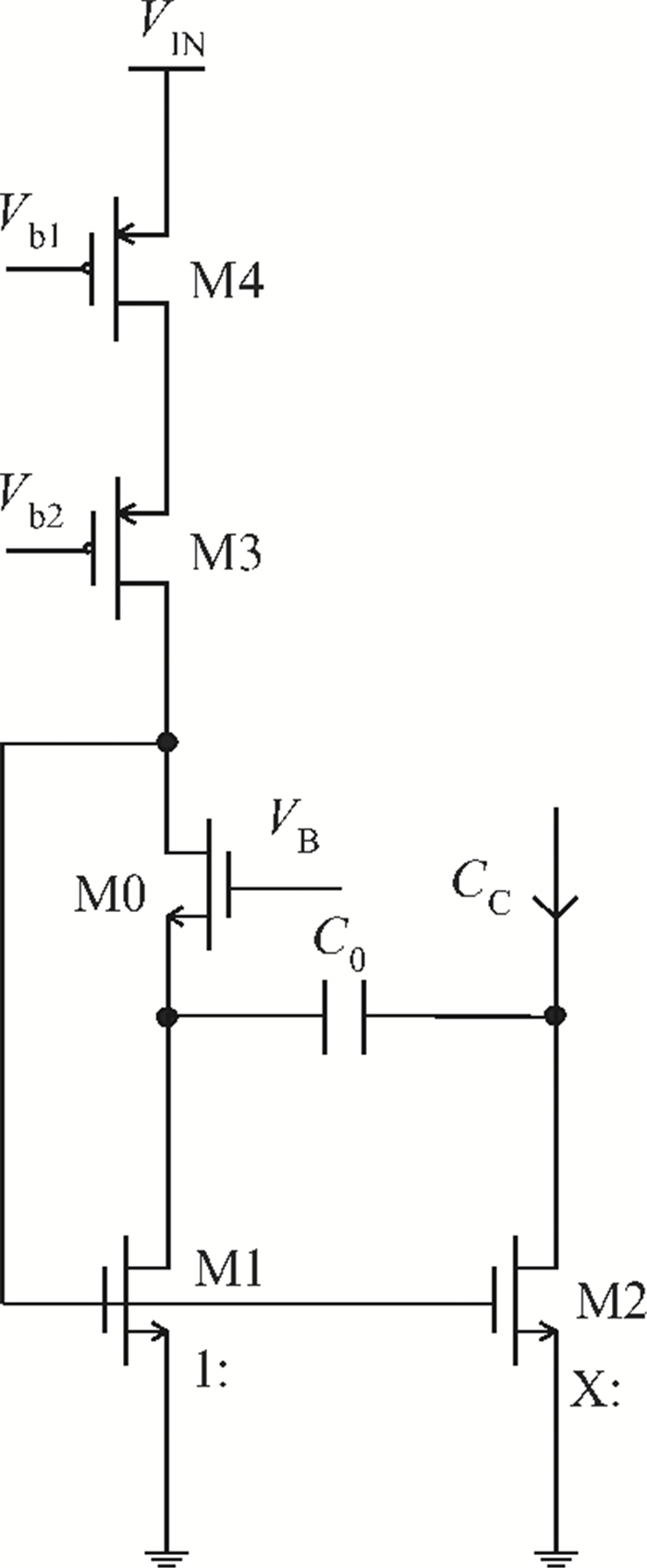

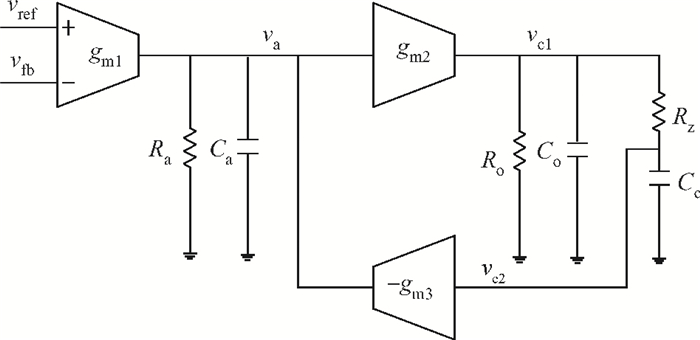

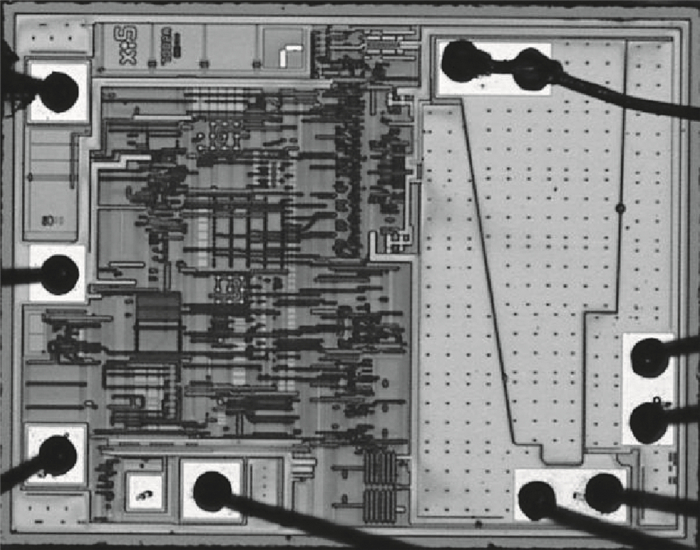

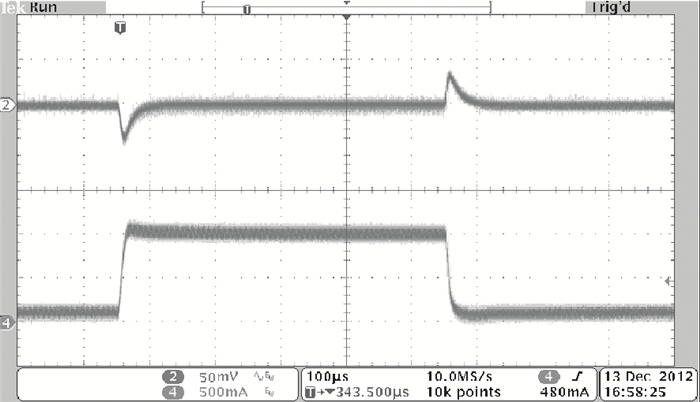

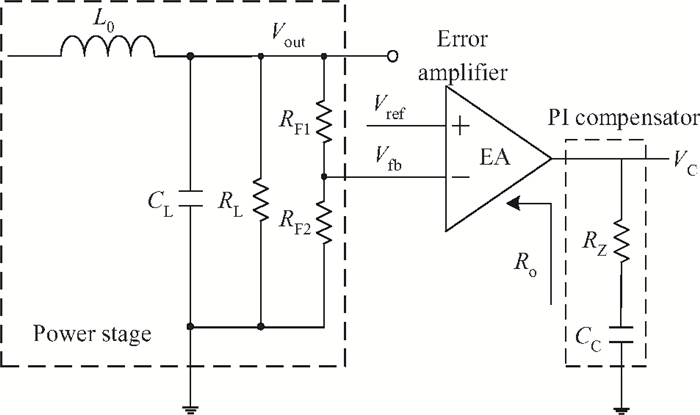

To achieve fast transient response for a DC-DC buck converter, an adaptive zero compensation circuit is presented. The compensation resistance is dynamically adjusted according to the different output load conditions, and achieves an adequate system phase margin under the different conditions. An improved capacitor multiplier circuit is adopted to realize the minimized compensation capacitance size. In addition, analysis of the small-signal model shows the correctness of the mechanism of the proposed adaptive zero compensation technique. A current-mode DC-DC buck converter with the proposed structure has been implemented in a 0.35 μm CMOS process, and the die size is only 800×1040 μm2. The experimental results show that the transient undershoot/overshoot voltage and the recovery times do not exceed 40 mV and 30 μs for a load current variation from 100 mA to 1 A. -

References

[1] Lee H, Mok P K T, Leung K N. Design of low-power analog drivers based on slew-rate enhancement circuit for CMOS low-dropout regulators. IEEE Trans Circuits Syst Ꜷ, 2005, 52(9):563 doi: 10.1109/TCSII.2005.850781[2] Chen L, Ferrario B. Adaptive frequency compensation for DC-to-DC converter. United States Patent, No. 0176098, 2006[3] Xu J, Zhou G, He M. Improved digital peak voltage predictive control for switching DC-DC converters. IEEE Trans Ind Electron, 2009, 56(8):3222 doi: 10.1109/TIE.2009.2022068[4] Yousefzadeh V, Babazadeh A, Ramachandran B, et al. Proximate time-optimal digital control for synchronous buck DC-DC converters. IEEE Trans Power Electron, 2008, 23(4):2018 doi: 10.1109/TPEL.2008.924843[5] Hsieh C Y, Chen K H. Adaptive pole-zero (APZP) technique of regulated power supply for improving SNR. IEEE Trans Power Electron, 2008, 23(6):2949 doi: 10.1109/TPEL.2008.2003014[6] Lee Y H, Huang S C, Wang S W, et al. Fast transient (FT) technique with adaptive phase margin (APM) for current mode DC-DC buck converters. IEEE Trans VLSI Syst, 2012, 20(10):1781 doi: 10.1109/TVLSI.2011.2163093[7] Lee Y H, Chu K Y, Shih C J, et al. Proportional compensated buck converter with a differential-in differential-out (DIDO) error amplifier and load regulation enhancement (LRE) mechanism. IEEE Trans Power Electron, 2012, 27(5):2426 doi: 10.1109/TPEL.2011.2173701[8] Chen K H, Huang H W, Kuo S Y. Fast-transient DC-DC converter with on-chip compensated error amplifier. IEEE Trans Circuits Syst, 2007, 54(12):1150 doi: 10.1109/TCSII.2007.905884[9] Lee Y H, Wang S J, Hsieh C Y, et al. Current mode DC-DC buck converters with optimal fast-transient control. IEEE International Symposium on Circuits and Systems, 2008:18 http://ieeexplore.ieee.org/document/4542100/authors[10] Rincon-Mora G. Active capacitor multiplier in Miller-compensated circuits. IEEE Trans Solid-State Circuits, 2000, 35(1):26 doi: 10.1109/4.818917[11] Chen K H, Chang C J, Liu T H. Bidirectional current-mode capacitor multipliers for on-chip compensation. IEEE Trans Power Electron, 2008, 23(1):180 doi: 10.1109/TPEL.2007.911776[12] Cai Shujiang, Pi Changming, Yan Wei, et al. A low noise high efficiency buck DC-DC converter with sigma-delta modulation. Journal of Semiconductors, 2011, 32(7):075004 doi: 10.1088/1674-4926/32/7/075004 -

Proportional views

DownLoad:

DownLoad: