| Citation: |

Xueqing Li, Hua Fan, Qi Wei, Zhen Xu, Jianan Liu, Huazhong Yang. A 14-bit 250-MS/s current-steering CMOS digital-to-analog converter[J]. Journal of Semiconductors, 2013, 34(8): 085013. doi: 10.1088/1674-4926/34/8/085013

****

X Q Li, H Fan, Q Wei, Z Xu, J N Liu, H Z Yang. A 14-bit 250-MS/s current-steering CMOS digital-to-analog converter[J]. J. Semicond., 2013, 34(8): 085013. doi: 10.1088/1674-4926/34/8/085013.

|

A 14-bit 250-MS/s current-steering CMOS digital-to-analog converter

DOI: 10.1088/1674-4926/34/8/085013

More Information

-

Abstract

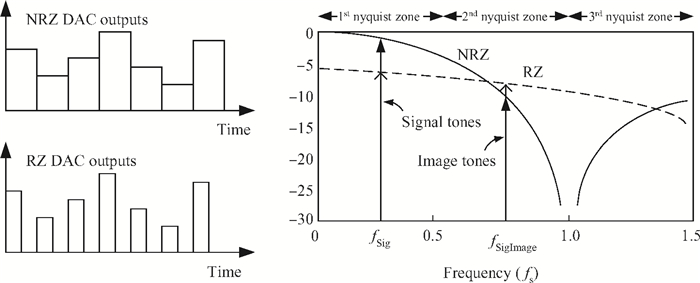

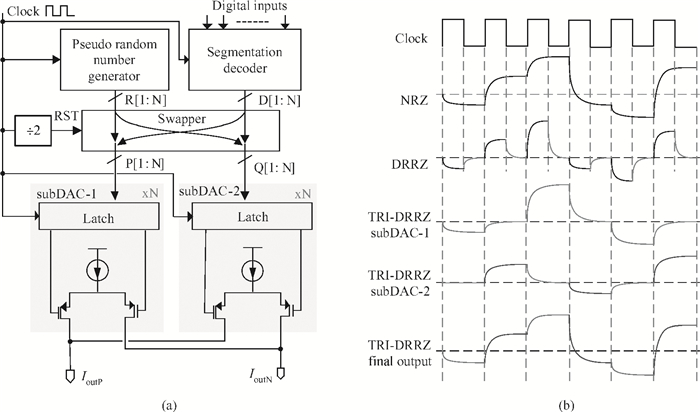

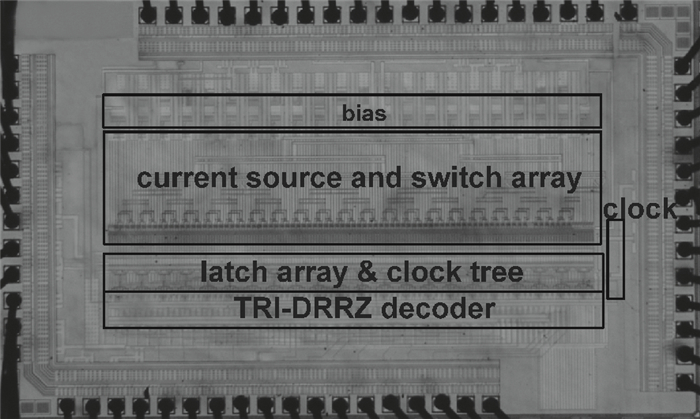

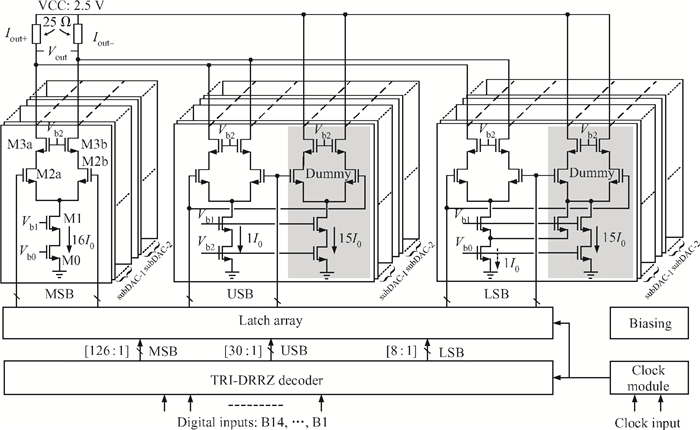

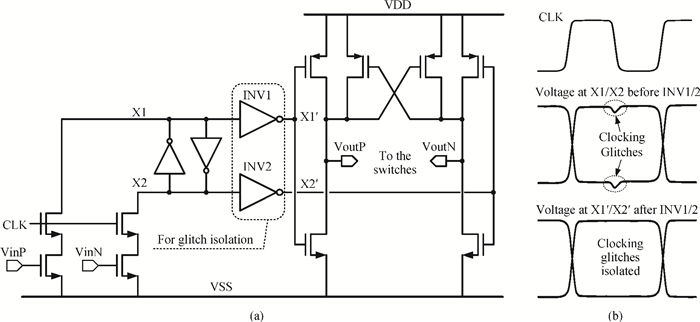

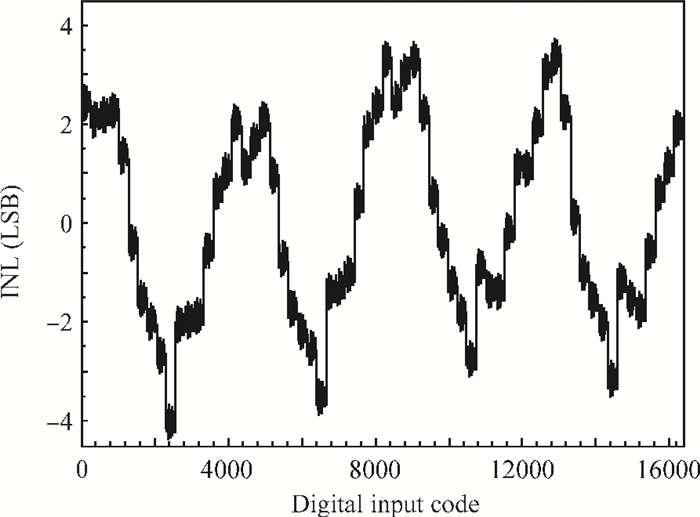

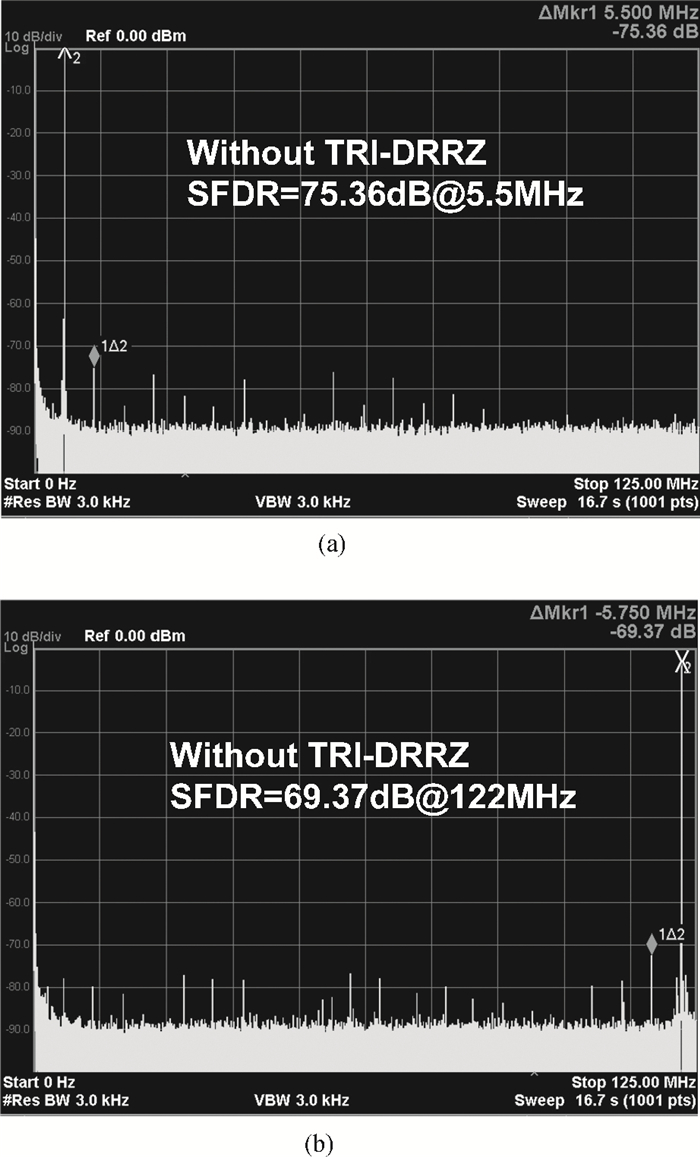

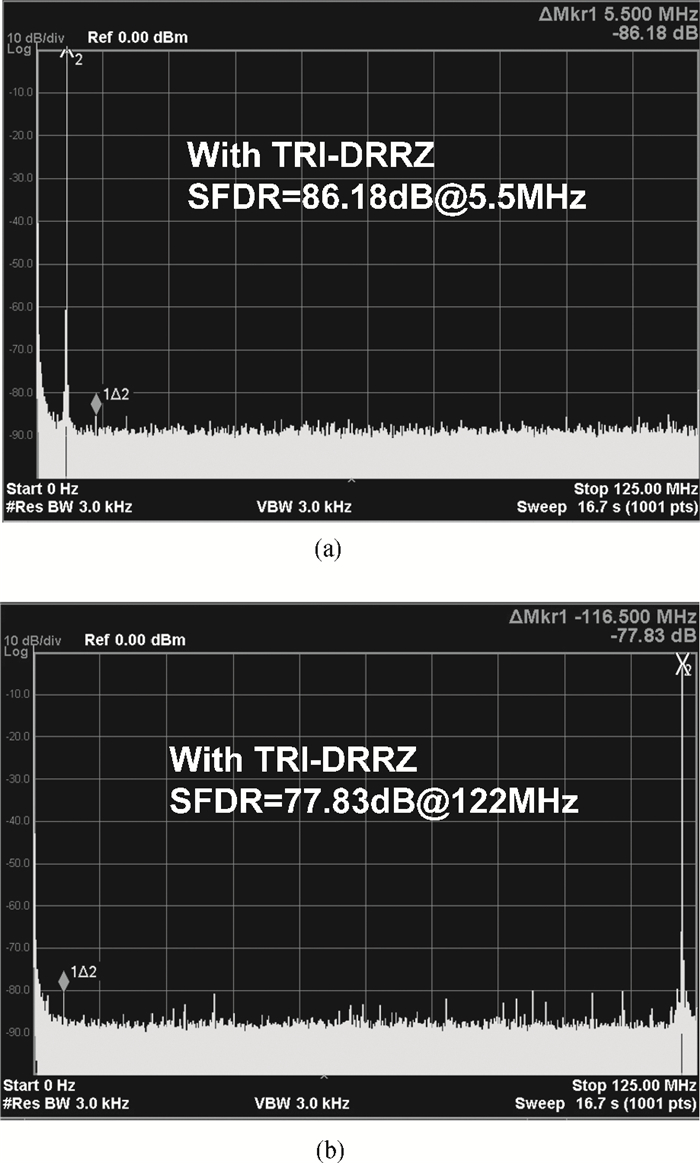

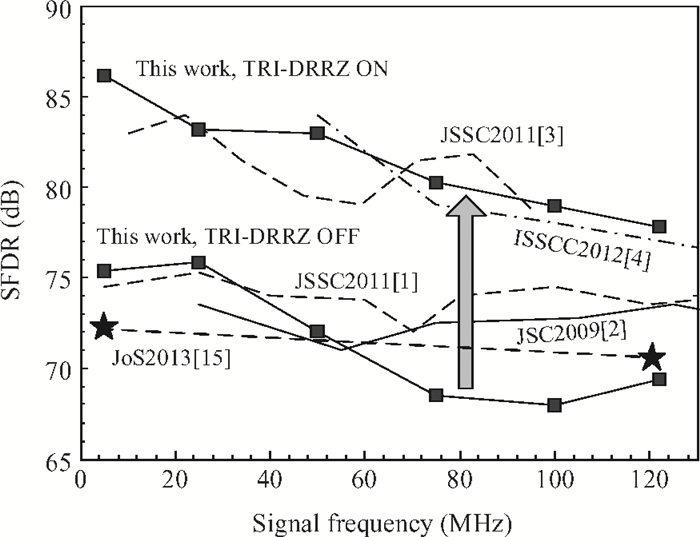

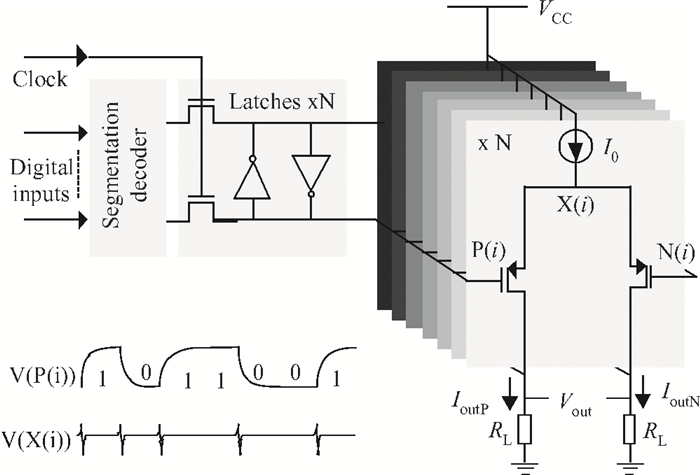

A 14-bit 250-MS/s current-steering digital-to-analog converter (DAC) was fabricated in a 0.13 μm CMOS process. In conventional high-speed current-steering DACs, the spurious-free dynamic range (SFDR) is limited by nonlinear distortions in the code-dependent switching glitches. In this paper, the bottleneck is mitigated by the time-relaxed interleaving digital-random-return-to-zero (TRI-DRRZ). Under 250-MS/s sampling rate, the measured SFDR is 86.2 dB at 5.5-MHz signal frequency and 77.8 dB up to 122 MHz. The DAC occupies an active area of 1.58 mm2 and consumes 226 mW from a mixed power supply of 1.2/2.5 V.-

Keywords:

- DAC,

- current-steering,

- SFDR,

- wide-band,

- time-interleaved

-

References

[1] Tseng W H, Fan C W, Wu J T. A 12-bit 1.25-GS/s DAC in 90 nm CMOS with >70 dB SFDR up to 500 MHz. IEEE J Solid-State Circuits, 2011, 46(12):2845 doi: 10.1109/JSSC.2011.2164302[2] Lin C H, van der Goes F M L, Westra J R, et al. A 12 bit 2.9 GS/s DAC with < -60 dBc beyond 1 GHz in 65 nm CMOS. IEEE J Solid-State Circuits, 2009, 44(12):3285 doi: 10.1109/JSSC.2009.2032624[3] Tang Y, Briaire J, Doris K, et al. A14 b 200 MS/s DAC with SFDR > 78 dBc, IM3<-83 dBc and NSD < -163 dBm/Hz across the whole Nyquist band enabled by dynamic-mismatch mapping. IEEE J Solid-State Circuits, 2011, 46(6):1371 doi: 10.1109/JSSC.2011.2126410[4] Engel G, Kuo S, Rose S. A 14b 3/6 GHz current-steering RF DAC in 0.18μm CMOS with 66 dB ACLR at 2.9 GHz. IEEE International Solid-State Circuits Conference (ISSCC), 2012:458[5] Van de Sande F, Lugil N, Demarsin F, et al. A 7.2 GSa/s, 14 bit or 12 GSa/s, 12 bit signal generator on a chip in a 165 GHz fT BiCMOS process. IEEE J Solid-State Circuits, 2012, 47(4):1003 doi: 10.1109/JSSC.2012.2185172[6] Schofield W, Mercer D, Onge L S. A 16 b 400 MS/s DAC with < -80 dBc IMD to 300 MHz and < -160 dBm/Hz noise power spectral density. IEEE International Solid-State Circuits Conference (ISSCC), 2003:126[7] Doris K, Briaire J, Leenaerts D, et al. A 12 b 500 MS/s DAC with > 70 dB SFDR up to 120 MHz in 0.18μm CMOS. IEEE International Solid-State Circuits Conference (ISSCC), 2005:116[8] Schafferer B, Adams R. A 3 V CMOS 400 mW 14 b 1.4 GS/s DAC for multi-carrier applications. IEEE International Solid-State Circuits Conference (ISSCC), 2004:360[9] Bugeja A R, Song B S, Rakers P L, et al. A 14-b, 100-MS/s CMOS DAC designed for spectral performance. IEEE J Solid-State Circuits, 1999, 34(12):1719 doi: 10.1109/4.808897[10] Lin W T, Kuo T H. A compact dynamic-performance-improved current-steering DAC with random rotation-based binary-weighted selection. IEEE J Solid-State Circuits, 2012, 47(2):444 doi: 10.1109/JSSC.2011.2168651[11] Van den Bosch A, Steyaert M, Sansen W. An accurate statistical yield model for CMOS current-steering D/A converters. IEEE Int Symp Circuits and Systems (ISCAS), 2000:Ⅳ.105 http://ieeexplore.ieee.org/document/858699/[12] Duinmaijer A C J, Welbers P G. Matching properties of MOS transistors. IEEE J Solid-State Circuits, 1989, 24(5):1433 doi: 10.1109/JSSC.1989.572629[13] Van der Plas G, Vandenbussche J, Sansen W, et al. A 14-bit intrinsic accuracy Q random walk CMOS DAC. IEEE J Solid-State Circuits, 1999, 34(12):1708 doi: 10.1109/4.808896[14] Lin C H, Bult K. A 10-b, 500-MSample/s CMOS DAC in 0.6 mm2. IEEE J Solid-State Circuits, 1998, 33(12):1948 doi: 10.1109/4.735535[15] Zhao Qi, Li Ran, Qiu Dong, et al. A 14-bit 1-GS/s DAC with a programmable interpolation filter in 65 nm CMOS. Journal of Semiconductors, 2013, 34(2):025004 doi: 10.1088/1674-4926/34/2/025004[16] Palmers P, Steyaert M S J. A 10-bit 1.6-GS/s 27-mW current-steering D/A converter with 550-MHz 54-dB SFDR bandwidth in 130-nm CMOS. IEEE Trans Circuits Syst Ⅰ, 2010, 57(11):2870 doi: 10.1109/TCSI.2010.2052491 -

Proportional views

DownLoad:

DownLoad: