| Citation: |

Lei Wang, Jianhua Jiang, Yiming Xiang, Yumei Zhou. A 130 nm radiation hardened flip-flop with an annular gate and a C-element[J]. Journal of Semiconductors, 2014, 35(1): 015010. doi: 10.1088/1674-4926/35/1/015010

****

L Wang, J H Jiang, Y M Xiang, Y M Zhou. A 130 nm radiation hardened flip-flop with an annular gate and a C-element[J]. J. Semicond., 2014, 35(1): 015010. doi: 10.1088/1674-4926/35/1/015010.

|

A 130 nm radiation hardened flip-flop with an annular gate and a C-element

DOI: 10.1088/1674-4926/35/1/015010

More Information

-

Abstract

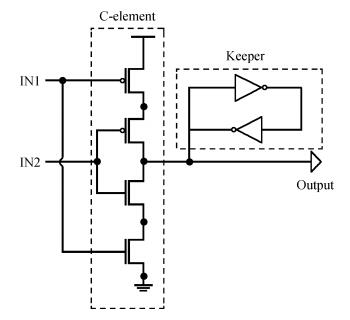

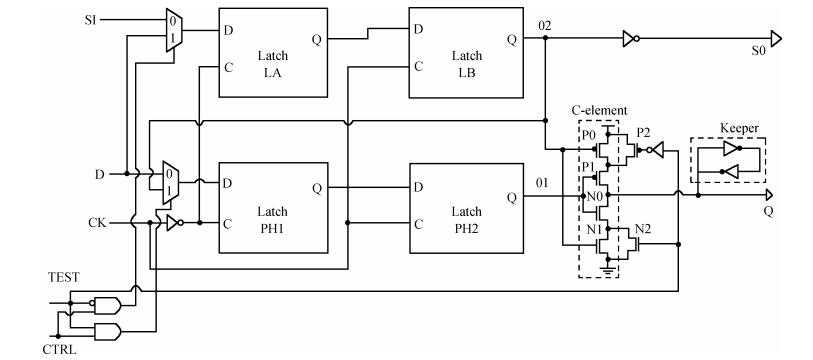

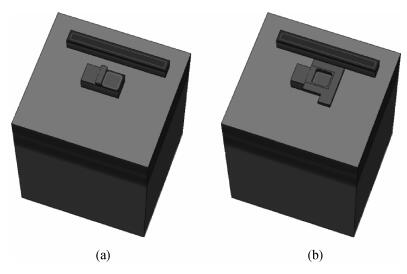

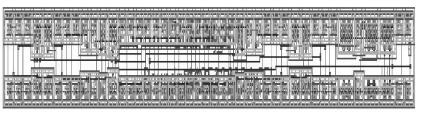

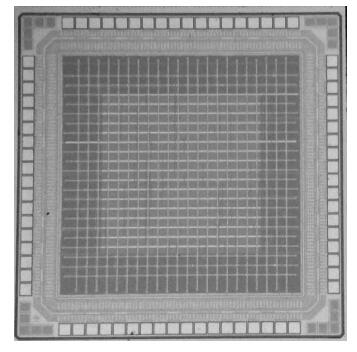

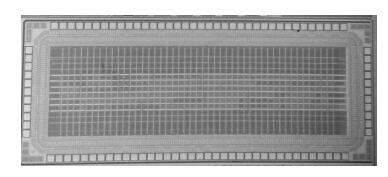

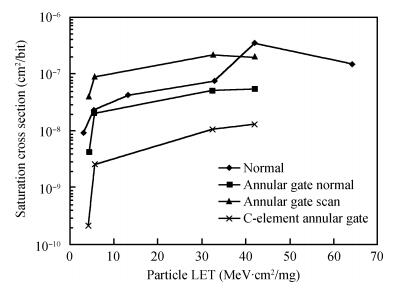

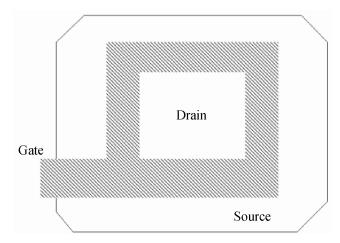

This paper presents a radiation hardened flip-flop with an annular gate and a Muller C-element. The proposed cell has multiple working modes which can be used in different situations. Each part of the cell can be verified easily and completely by using different modes. This cell has been designed under an SMIC 0.13 μm process and 3-D simulated by using Synopsys TCAD. Heavy-ion testing has been done on the cell and its counterparts. The test results demonstrate that the presented cell reduces the cell's saturation cross section by approximately two orders of magnitude with little penalty on performance.-

Keywords:

- SEU,

- flip-flop,

- annular gate,

- C-element

-

References

[1] Petersen E. Single event effects in aerospace. Wiley-IEEE Press, 2010 http://www.wiley.com/WileyCDA/WileyTitle/productCd-1118084314.html[2] Nicolaidis M. Design for soft error mitigation. IEEE Trans Device Mater Reliab, 2005, 5(3):405 doi: 10.1109/TDMR.2005.855790[3] Gan Xuewen, Wang Xushe, Zhang Xing. Analysis of threshold voltage decreasing for double-gate and surrounding-gate MOSFET's. Chinese Journal of Semiconductors, 2001, 22(12):1581 http://www.oalib.com/paper/1520674[4] Mitra S, Seifert N, Zhang M, et al. Robust system design with built-in soft-error resilience. Computer, 2005, 38(2):43 doi: 10.1109/MC.2005.70[5] Mitra S, Zhang M, Seifert N, et al. Built-in soft error resilience for robust system design. IEEE International Conference on Integrated Circuit Design and Technology, 2007 http://web.stanford.edu/class/ee386/[6] Uemura T, Tosaka Y, Matsuyama H, et al. Robust flip-flop circuit against soft errors for combinational and sequential logic circuits. Jpn J Appl Phys, 2009, 48:04C070 http://adsabs.harvard.edu/abs/2009JaJAP..48dC070U[7] Mitra S. Robust system design. 23rd International Conference on VLSI Design, 2010:434 -

Proportional views

DownLoad:

DownLoad: