| Citation: |

Yiqiang Wu, Zhigong Wang, Junliang Wang, Li Ma, Jian Xu, Lu Tang. Lower-power, high-linearity class-AB current-mode programmable gain amplifier[J]. Journal of Semiconductors, 2014, 35(10): 105003. doi: 10.1088/1674-4926/35/10/105003

****

Y Q Wu, Z G Wang, J L Wang, L Ma, J Xu, L Tang. Lower-power, high-linearity class-AB current-mode programmable gain amplifier[J]. J. Semicond., 2014, 35(10): 105003. doi: 10.1088/1674-4926/35/10/105003.

|

Lower-power, high-linearity class-AB current-mode programmable gain amplifier

DOI: 10.1088/1674-4926/35/10/105003

More Information

-

Abstract

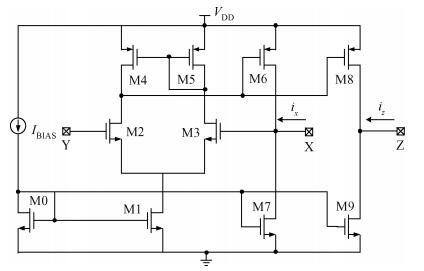

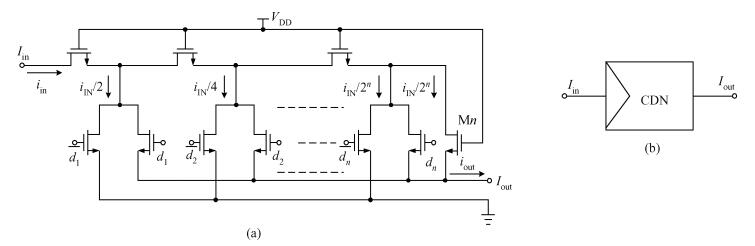

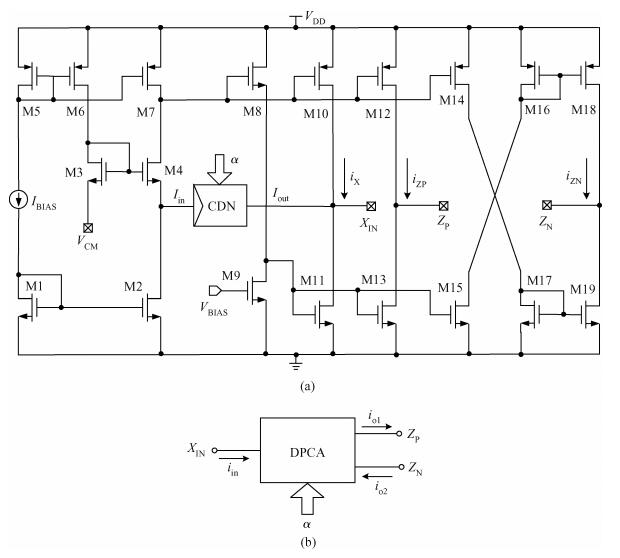

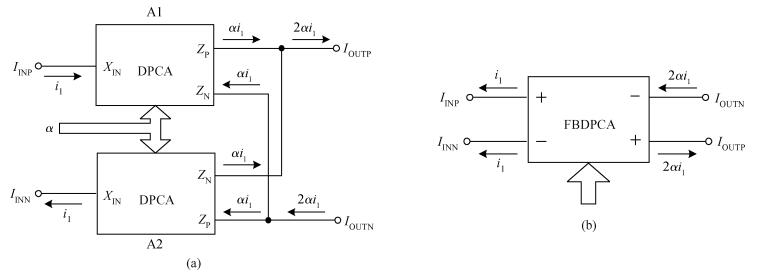

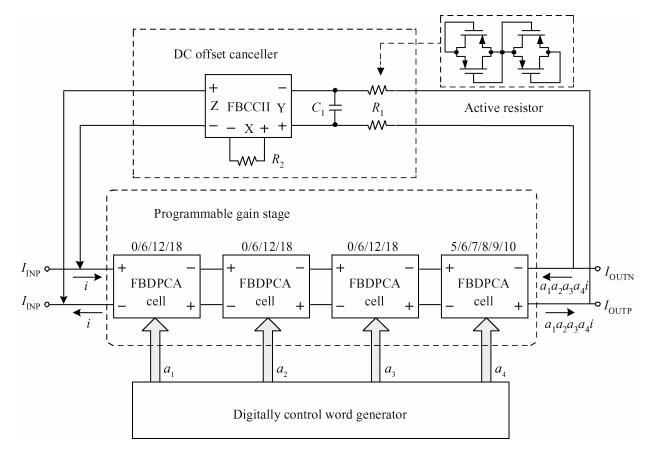

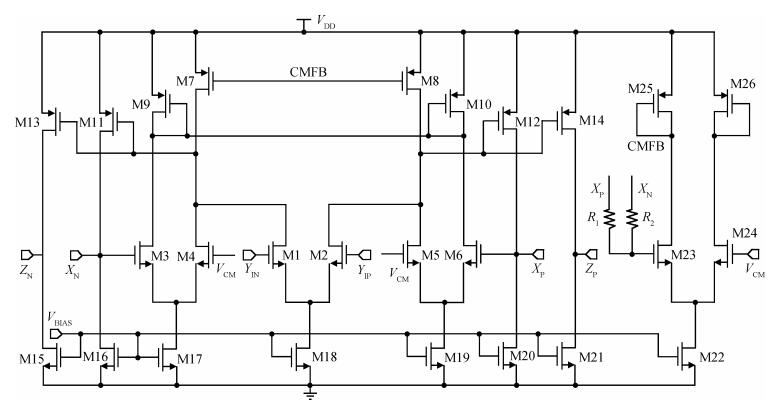

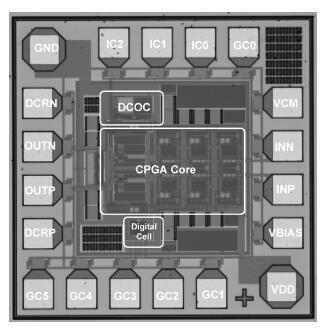

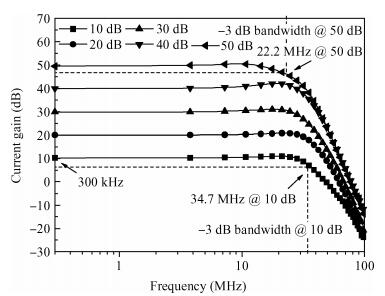

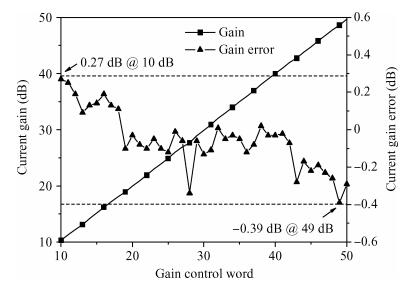

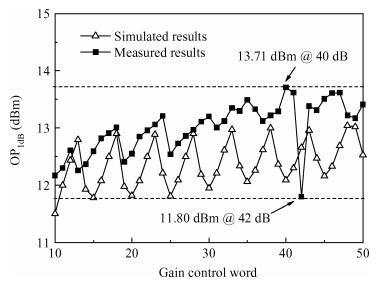

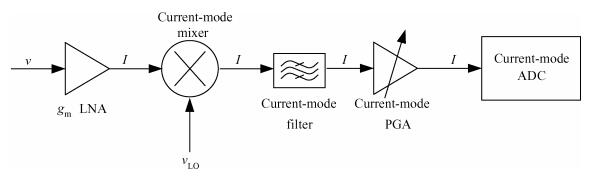

A novel class-AB implementation of a current-mode programmable gain amplifier (CPGA) including a current-mode DC offset cancellation loop is presented. The proposed CPGA is based on a current amplifier and provides a current gain in a range of 40 dB with a 1 dB step. The CPGA is characterized by a wide range of current gain variation, a lower power dissipation, and a small chip size. The proposed circuit is fabricated using a 0.18 μm CMOS technology. The CPGA draws a current of less than 2.52 mA from a 1.8 V supply while occupying an active area of 0.099 μm2. The measured results show an overall gain variation from 10 to 50 dB with a gain error of less than 0.40 dB. The OP1dB varies from 11.80 to 13.71 dBm, and the 3 dB bandwidth varies from 22.2 to 34.7 MHz over the whole gain range.-

Keywords:

- current mode,

- class AB,

- programmable gain amplifier,

- current amplifier

-

References

[1] Yoshii N, Mizutani K, Sugimoto Y. A current-mode ADC with current exchanging and averaging capabilities by switching the currents and calculating data in the digital domain. IEEE Custom Integrated Circuits Conference, 2007:209 https://www.infona.pl/resource/bwmeta1.element.ieee-art-000004405715[2] Sun Yong, Lai Fengchang, Ye Yizheng. Current mode ADC design in a 0.5-μm CMOS process. Journal of Semiconductors, 2009, 30(6):065002 doi: 10.1088/1674-4926/30/6/065002[3] Peric I, Armbruster T, Koch M, et al. DCD-the multi-channel current-mode ADC chip for the readout of DEPFET pixel detectors. IEEE Trans Nucl Sci, 2010, 57(2):743 doi: 10.1109/TNS.2010.2040487[4] Sugimoto Y, Gohda Y, Tanaka S. A 35 MS/s and 2 V/2.5 V current-mode sample-and-hold circuit with an input current linearization technique. IEEE Asian Solid-State Circuits Conference, 2005:445 http://ieeexplore.ieee.org/document/4017627/?reload=true&arnumber=4017627&count=140&index=113[5] Alzaher H A. A CMOS digitally programmable universal current-mode filter. IEEE Trans Circuits Syst, 2008, 55(8):758 doi: 10.1109/TCSII.2008.921599[6] Mahmoud S A, Hashiesh M A, Soliman A M. Low-voltage digitally controlled fully differential current conveyor. IEEE Trans Circuits Syst I:Regular Papers, 2005, 52(10):2055 doi: 10.1109/TCSI.2005.852922[7] Alzaher H, Tasadduq N. Realizations of CMOS fully differential current followers/amplifiers. IEEE International Symposium on Circuits and Systems, 2009:1381 http://ieeexplore.ieee.org/document/5118022/?arnumber=5118022&contentType=Conference%20Publications[8] Elmala M, Carlton B, Bishop R, et al. A 1.4 V, 13.5 mW, 10/100 MHz 6th order elliptic filter/VGA with DC-offset correction in 90 nm CMOS. IEEE Radio Frequency integrated Circuits (RFIC) Symposium, 2005:189 http://ieeexplore.ieee.org/abstract/document/1489627/[9] Zhou Jiaye, Tan Xi, Wang Junyu, et al. A 60-dB linear VGA with novel exponential gain approximation. Journal of Semiconductors, 2009, 30(6):065006 doi: 10.1088/1674-4926/30/6/065006[10] Soliman E A, Mahmoud S A. Multi-standard receiver baseband chain using digitally programmable OTA based on CCⅡ and current division networks. IEEE International Conference on Engineering and Technology, 2012:1 http://ieeexplore.ieee.org/document/6396167/authors[11] La Cruz-Blas D, López-Martín A. A 0.75-V compact CMOS class-AB current-mode exponential variable gain amplifier. IEEE Trans Circuits Syst Ⅱ:Express Briefs, 2007, 54(12):1042 doi: 10.1109/TCSII.2007.906965 -

Proportional views

DownLoad:

DownLoad: