| Citation: |

Xian Li, Huicai Zhong, Cheng Jia, Xin Li. A 4-kbit low-cost antifuse one-time programmable memory macro for embedded applications[J]. Journal of Semiconductors, 2014, 35(5): 055007. doi: 10.1088/1674-4926/35/5/055007

****

X Li, H C Zhong, C Jia, X Li. A 4-kbit low-cost antifuse one-time programmable memory macro for embedded applications[J]. J. Semicond., 2014, 35(5): 055007. doi: 10.1088/1674-4926/35/5/055007.

|

A 4-kbit low-cost antifuse one-time programmable memory macro for embedded applications

DOI: 10.1088/1674-4926/35/5/055007

More Information

-

Abstract

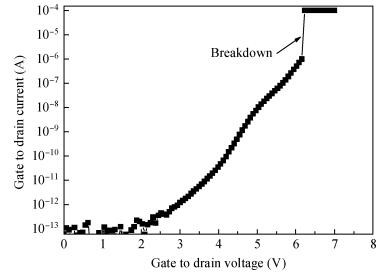

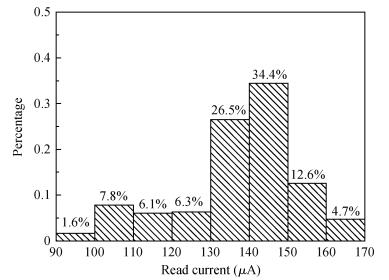

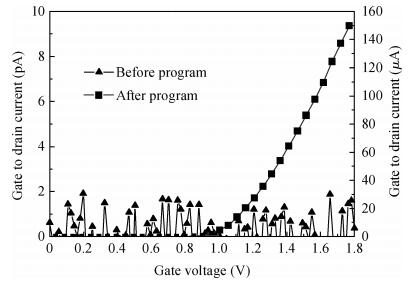

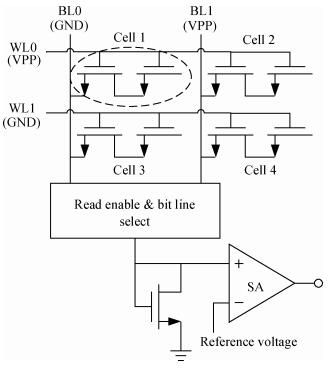

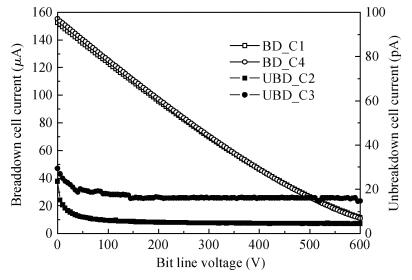

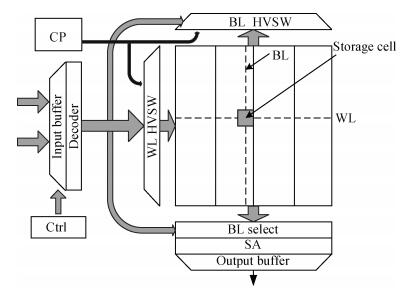

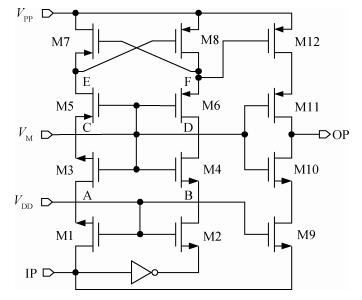

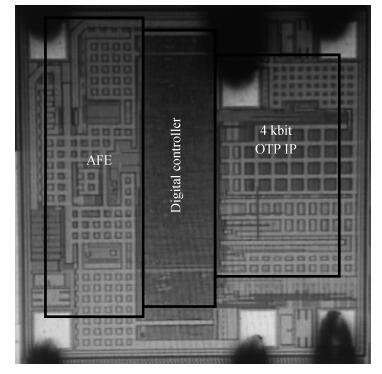

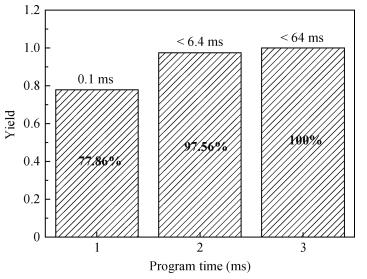

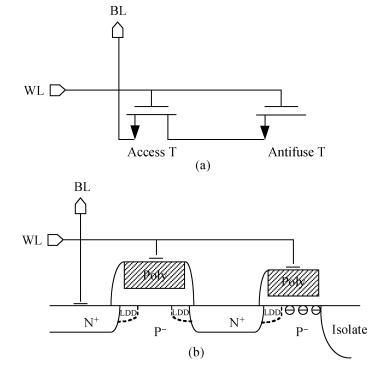

A 4-kbit low-cost one-time programmable (OTP) memory macro for embedded applications is designed and implemented in a 0.18-μm standard CMOS process. The area of the proposed 1.5 transistor (1.5T) OTP cell is 2.13 μm2, which is a 49.3% size reduction compared to the previously reported cells. The 1.5T cell is fabricated and measured and shows a large programming window without any disturbance. A novel high voltage switch (HVSW) circuit is also proposed to make sure the OTP macro, implemented in a standard CMOS process, works reliably with the high program voltage. The OTP macro is embedded in negative radio frequency identification (RFID) tags. The full chip size, including the analog front-end, digital controller and the 4-kbit OTP macro, is 600×600 μm2. The 4-kbit OTP macro only consumes 200×260 μm2. The measurement shows a 100% program yield by adjusting the program time and has obvious advantages in the core area and power consumption compared to the reported 3T and 2T OTP cores.-

Keywords:

- OTP,

- 1.5 transistor cell,

- high voltage switch,

- RFID,

- size reduction

-

References

[1] Cha H K, Yun I, Kim J, et al. A 32-KB standard CMOS antifuse one-time programmable ROM embedded in a 16-bit microcontroller. IEEE J Solid-State Circuits, 2006, 41:2115 doi: 10.1109/JSSC.2006.880603[2] Yang Xiaonan, Wang Yong, Zhang Manhong. A novel 2-T structure memory device using a Si nanodot for embedded application. Journal of Semiconductors, 2011, 32(12):124007 doi: 10.1088/1674-4926/32/12/124007[3] Jia Xiaoyun, Feng Peng, Zhang Shengguang. An ultra-low-power area efficient non-volatile memeory in 0.18μm single-poly CMOS process for passive RFID tags. Journal of Semiconductors, 2013, 34(8):085004 doi: 10.1088/1674-4926/34/8/085004[4] Kothandaraman C, Iyer S K, Iyer S S. Electrically programmable fuse (eFUSE) using electromigration in silicides. IEEE Electron Device Lett, 2002, 23:523 doi: 10.1109/LED.2002.802657[5] Alavi M, Bohr M, Hicks J, et al. A PROM element based on salicide agglomeration of poly fuses in a CMOS logic process. Technical Digest, International Electron Devices Meeting, 1997:855 http://www.smtnet.com/library/files/upload/prom-element.pdf[6] Wee J K, Min K S, Park J T, et al. A post-package bit-repair scheme using static latches with bipolar-voltage programmable antifuse circuit for high-density DRAMs. IEEE J Solid-State Circuits, 2002, 37:251 doi: 10.1109/4.982432[7] Candelier P, Villani N, Schoellkopf J P, et al. One time programmable drift antifuse cell reliability. Proceedings 38th Annual 2000 IEEE International Reliability Physics Symposium, 2000:169 http://ieeexplore.ieee.org/document/843909/[8] Ito H, Namekawa T. Pure CMOS one-time programmable memory using gate-ox anti-fuse. Proceedings of the IEEE Custom Integrated Circuits Conference, 2004:469 doi: 10.1007/s11771-011-0669-7[9] Kim J, Lee K. Three-transistor one-time programmable (OTP) ROM cell array using standard CMOS gate oxide antifuse. IEEE Electron Device Lett, 2003, 24:589 doi: 10.1109/LED.2003.815429[10] Barsatan R, Yin M T, Mansun C. A zero-mask one-time programmable memory array for RFID applications. Proceedings IEEE International Symposium on Circuits and Systems, 2006:4 https://www.mendeley.com/research-papers/zeromask-onetime-programmable-memory-array-rfid-applications/[11] Peng J, Rosendale G, Fliesler M. A novel embedded OTP NVM using standard foundry CMOS logic technology. NVSMW, 2006:24 doi: 10.1007/978-3-319-48339-9_9/fulltext.html[12] Palumbo G, Pappalardo D, Gaibotti M. Charge-pump circuits:power-consumption optimization. IEEE Trans Circuits Syst I-Fundamental Theory and Applications, 2002, 49:1535 doi: 10.1109/TCSI.2002.804544[13] Baek J M, Chun J H, Kwon K W. A power-efficient voltage upconverter for embedded EEPROM application. IEEE Trans Circuits Syst Ⅱ-Express Briefs, 2010, 57:435 doi: 10.1109/TCSII.2010.2048351 -

Proportional views

DownLoad:

DownLoad: