| Citation: |

Sen Yue, Yiqiang Zhao, Ruilong Pang, Yun Sheng. A 14-bit 50 MS/s sample-and-hold circuit for pipelined ADC[J]. Journal of Semiconductors, 2014, 35(5): 055009. doi: 10.1088/1674-4926/35/5/055009

****

S Yue, Y Q Zhao, R L Pang, Y Sheng. A 14-bit 50 MS/s sample-and-hold circuit for pipelined ADC[J]. J. Semicond., 2014, 35(5): 055009. doi: 10.1088/1674-4926/35/5/055009.

|

A 14-bit 50 MS/s sample-and-hold circuit for pipelined ADC

DOI: 10.1088/1674-4926/35/5/055009

More Information

-

Abstract

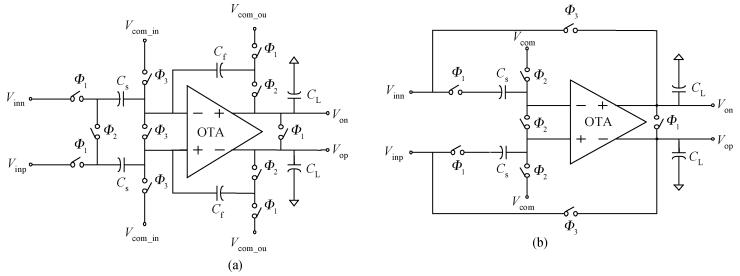

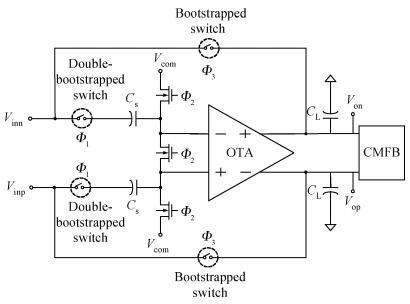

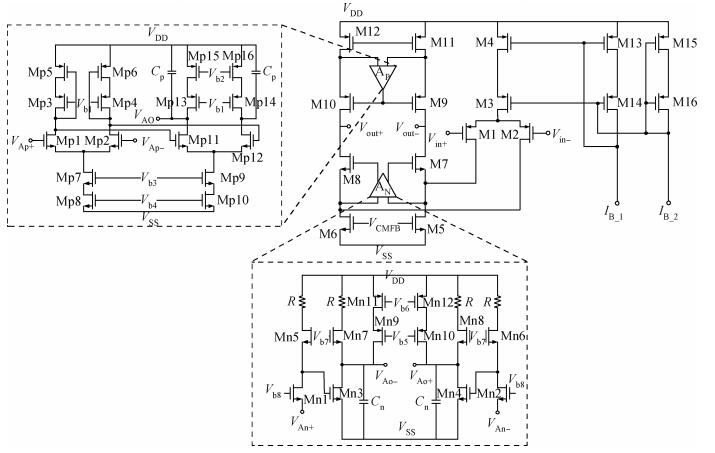

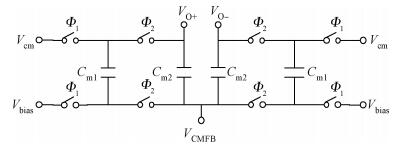

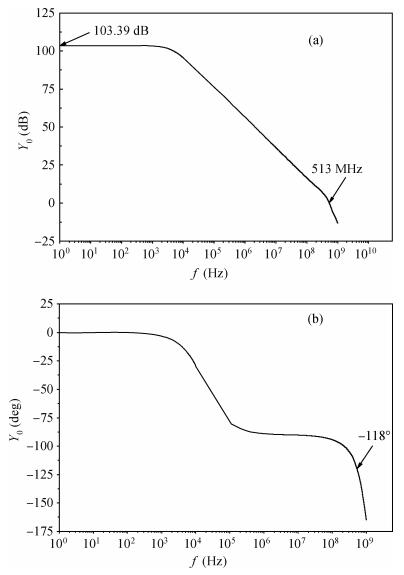

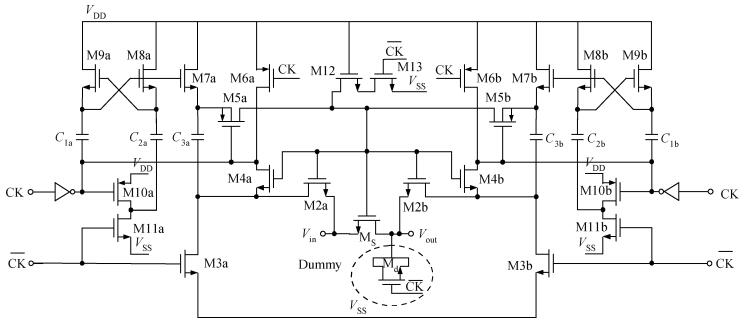

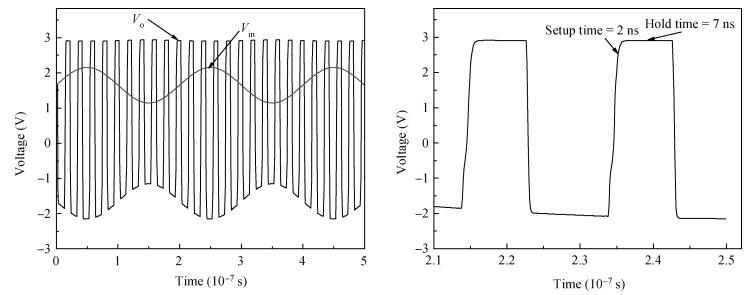

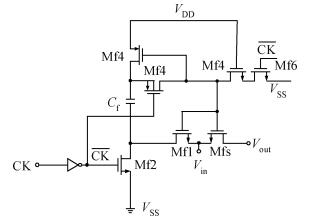

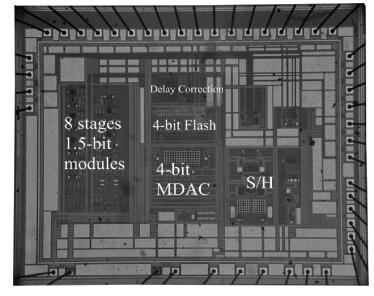

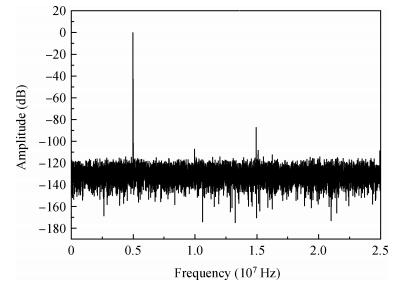

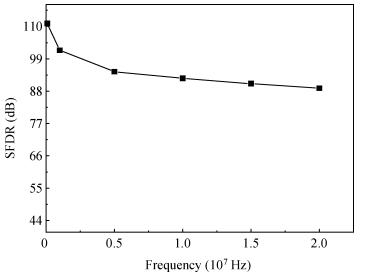

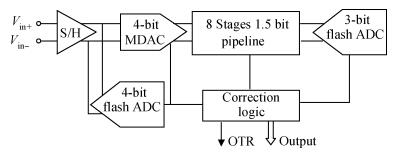

A high performance sample-and-hold (S/H) circuit used in a pipelined analog-to-digital converter (ADC) is presented. Capacitor flip-around architecture is used in this S/H circuit with a novel gain-boosted differential folded cascode operational transconductance amplifier. A double-bootstrapped switch is designed to improve the performance of the circuit. The circuit is implemented using a 0.18 μm 1P6M CMOS process. Measurement results show that the effective number of bits is 14.03 bits, the spurious free dynamic range is 94.62 dB, the signal to noise and distortion ratio is 86.28 dB, and the total harmonic distortion is -91.84 dB for a 5 MHz input signal with 50 MS/s sampling rate. A pipeline ADC with the designed S/H circuit has been implemented. -

References

[1] Sumanen L. Pipeline analog-to-digital converters for wide band wireless communications. Helsinki: Helsinki University of Technology, 2002[2] Abo A M. Design for reliability of low-voltage switched-capacitor circuits. California: University of California-Berkeley, 1999[3] Kelly D, Yang W, Mehr I, et al. A 3 V 340 mW 14 b 75 MSPS CMOS ADC with 85 dB SFDR at Nyquist. IEEE International Solid-State Circuits Conference (ISSCC), 2001:134 http://www.doc88.com/p-579321093131.html[4] Lewis S H, Gray P R. A pipelined 5-Msample/s 9-bit analog-to-digital converter. IEEE J Solid-State Circuits, 1987, 22(6):954 doi: 10.1109/JSSC.1987.1052843[5] Chouia Y, EI-Sankary K, Sale A. et al. 14 b, 50 MS/s CMOS front-end sample and hold module dedicated to a pipelined ADC. IEEE Transactions on Circuits and Systems, 2004:I-353 doi: 10.1007/978-1-4614-1371-4_4/fulltext.html[6] Fu Dawei. Research and design of S/H in high-speed high-resolution ADC. Zhejiang: Zhejiang University, 2012(in Chinese)[7] Jie Y, Farhat N, Van der Spiegel J. GBOPCAD:a synthesis tool for high-performance gain-boosted opamp design. IEEE Trans Circuits Syst I, 2005, 52(8):1535 doi: 10.1109/TCSI.2005.851718[8] Bult K, Geelen G J G M. A fast-settling CMOS op amp for SC Circuits with 90-dB DC gain. IEEE J Solid-State Circuits, 1990, 25(6):1379 doi: 10.1109/4.62165[9] Kamath B Y T, Meyer R G, Gray P R. Relationship between frequency response and settling time of operational amplifiers. IEEE J Solid-State Circuits, 1974, 9(6):347 doi: 10.1109/JSSC.1974.1050527[10] Yang H C, Allstot D J. Considerations for fast settling operational amplifiers. IEEE Trans Circuits Syst, 1990, 37(3):326 doi: 10.1109/31.52726[11] Senderowicz D, Dreyer S F, Huggins J H, et al. A family of differential NMOS analog circuit for a PCM codec filter chip. IEEE J Solid-State Circuits, 1982, 17(6):1014 doi: 10.1109/JSSC.1982.1051855[12] Zhu Xubin, Ni Weining, Shi Yin. A 10-bit 50-MS/s sample-and-hold circuit with low distortion sampling switches. Journal of Semiconductors, 2009, 30(5):055011 doi: 10.1088/1674-4926/30/5/055011[13] Dai Lan, Jiang Yanfeng, Liu Wenkai. Implementation of sample and hold circuit for 12-bit 50 MHz pipeline ADC. Microelectronics, 2010, 40(4):503 https://cds.cern.ch/record/1235855/files/p448.pdf[14] Wang H, Hong H, Sun L, et al. A sample-and-hold circuit for 10-bit 100 MS/s pipelined ADC. IEEE International Conference ASICON: 480 -

Proportional views

DownLoad:

DownLoad: