| Citation: |

Liguo Zhou, Jin Peng, Fang Yuan, Zhi Fang, Jun Yan, Yin Shi. A carrier leakage calibration and compensation technique for wideband wireless transceiver[J]. Journal of Semiconductors, 2014, 35(6): 065003. doi: 10.1088/1674-4926/35/6/065003

****

L G Zhou, J Peng, F Yuan, Z Fang, J Yan, Y Shi. A carrier leakage calibration and compensation technique for wideband wireless transceiver[J]. J. Semicond., 2014, 35(6): 065003. doi: 10.1088/1674-4926/35/6/065003.

|

A carrier leakage calibration and compensation technique for wideband wireless transceiver

DOI: 10.1088/1674-4926/35/6/065003

More Information

-

Abstract

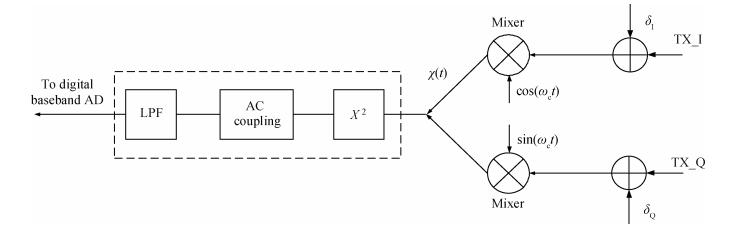

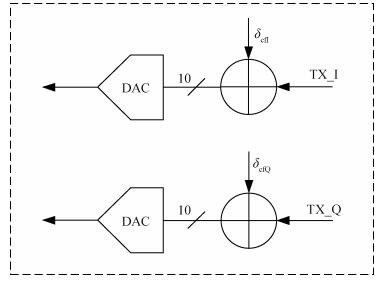

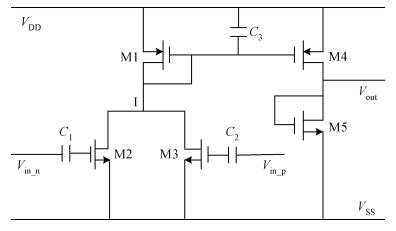

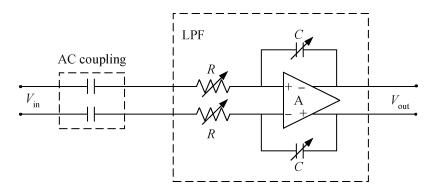

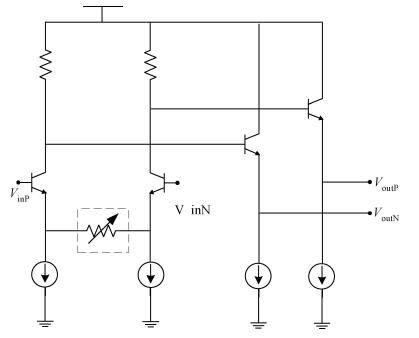

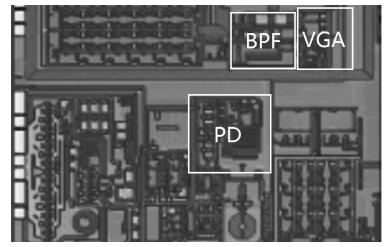

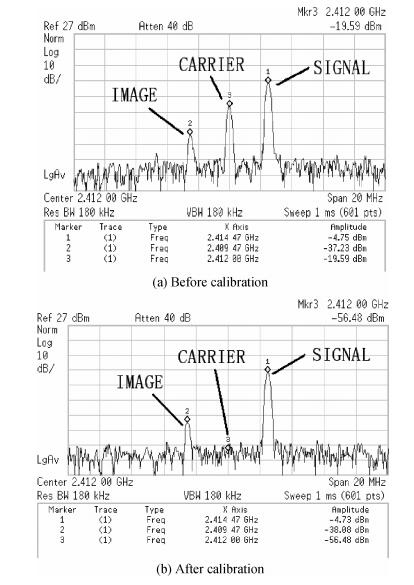

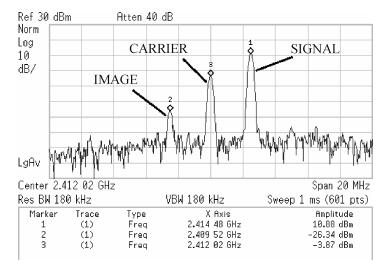

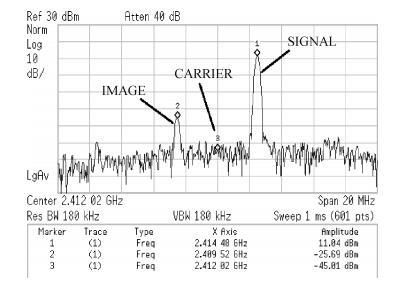

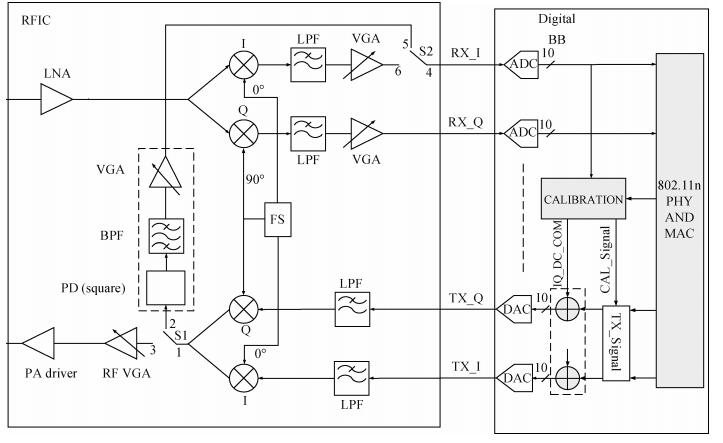

A carrier leakage calibration and compensation technique based on digital baseband for a wideband wireless communication transceiver is proposed. The digital baseband transmits a calibration signal, samples the signal which passes through the transmitter path and the calibration loop in the RF chip, measures the carrier leakage by analyzing the sampled data and compensates it. Compared with a self-calibration technique in the RF chip, the proposed technique saves area and power consumption for the wireless local area network (WLAN) solution. This technique has been successfully used for 802.11n system and satisfies the requirement of the standard by achieving over 50 dB carrier leakage suppression.-

Keywords:

- 802.11n,

- WLAN,

- direct-conversion,

- carrier leakage,

- calibration,

- DC offset

-

References

[1] Zhang P, Der L. A single-chip dual-band direct-conversion IEEE 802.11 a/b/g WLAN transceiver in 0.13-μm CMOS. IEEE J Solid-State circuits, 2005, 40(9):1932 doi: 10.1109/JSSC.2005.848182[2] Brenna G, Tschopp D. A 2-GHz carrier leakage calibrated direct-conversion WCDMA transmitter in 0.13-μm CMOS. IEEE J Solid-State circuits, 2004, 39(8):1253 doi: 10.1109/JSSC.2004.831794[3] Maas S A. Microwave mixers. 2nd ed. Artech House, 1993[4] Minarik R. Circuit for canceling local oscillator leakage through mixers. Microwave Journal, 1985:182 http://www.freepatentsonline.com/5001773.html[5] Wang Y, Shou L. A LO-leakage auto-calibration CMOS IEEE802.11b/g WLAN transceiver. IEEE International Symposium on Circuits and Systems, 2007:3912 http://ieeexplore.ieee.org/xpl/articleDetails.jsp?reload=true&arnumber=4253537[6] Lanschutzer C, Springer A. Integrated adaptive LO leakage cancellation for W-CDMA direct upconversion transceivers. IEEE Radio Frequency Integrated Circuits (RFIC) Symposium, 2003:19 http://ieeexplore.ieee.org/xpls/icp.jsp?arnumber=1213884[7] Fang Yuan. A direct-conversion WLAN transceiver baseband with DC offset compensation and carrier leakage reduction. Journals of Semiconductors, 2010, 31(10):105003 doi: 10.1088/1674-4926/31/10/105003[8] Wireless LAN Medium Access Control (MAC) and Physical Layer (PHY) Specifications, Amendment 5: Enhancements for Higher Throughput. New York: The Institute of Electrical and Electronics Engineers, Inc, 2009 -

Proportional views

DownLoad:

DownLoad: