| Citation: |

Mingyi Chen, Xiaoji Chu, Peng Yu, Jun Yan, Yin Shi. A ΔΣ fractional-N frequency synthesizer for FM tuner using low noise filter and quantization noise suppression technique[J]. Journal of Semiconductors, 2014, 35(7): 075003. doi: 10.1088/1674-4926/35/7/075003

****

M Y Chen, X J Chu, P Yu, J Yan, Y Shi. A ΔΣ fractional-N frequency synthesizer for FM tuner using low noise filter and quantization noise suppression technique[J]. J. Semicond., 2014, 35(7): 075003. doi: 10.1088/1674-4926/35/7/075003.

|

A ΔΣ fractional-N frequency synthesizer for FM tuner using low noise filter and quantization noise suppression technique

DOI: 10.1088/1674-4926/35/7/075003

More Information

-

Abstract

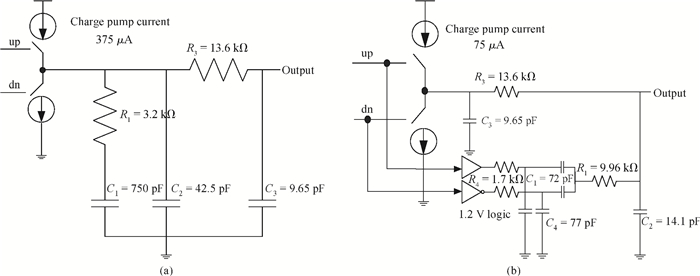

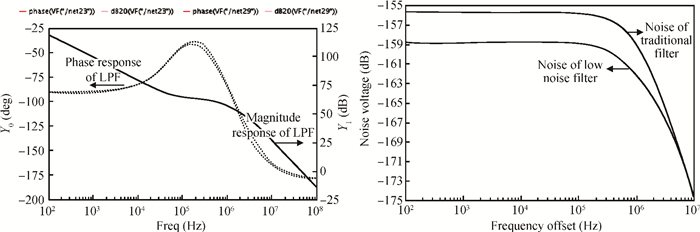

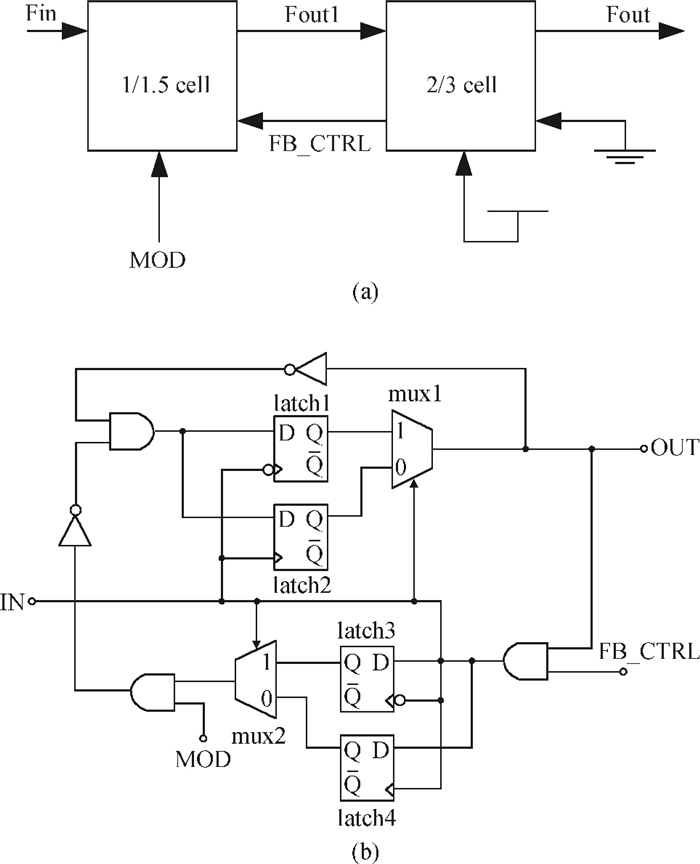

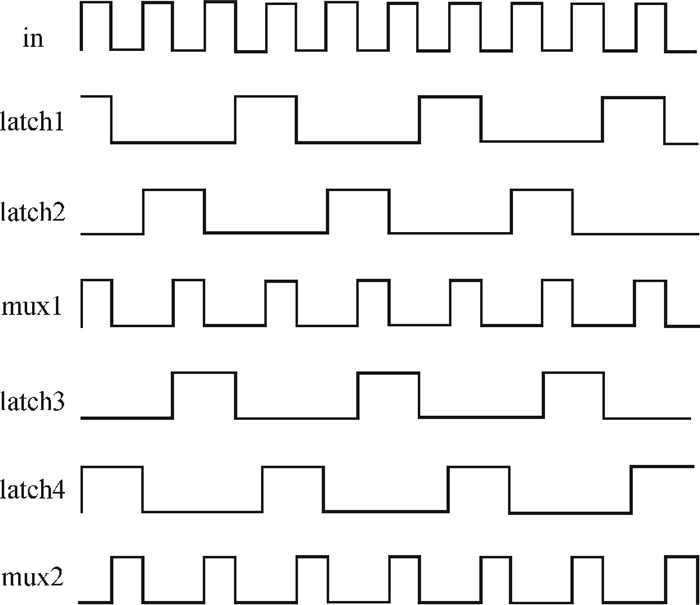

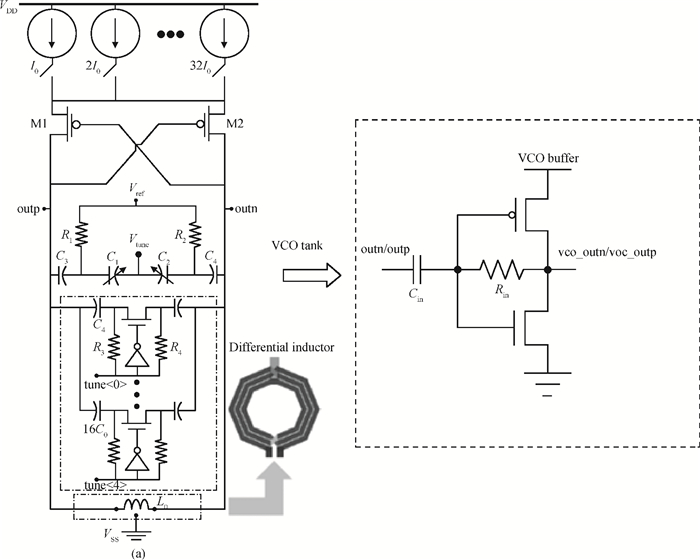

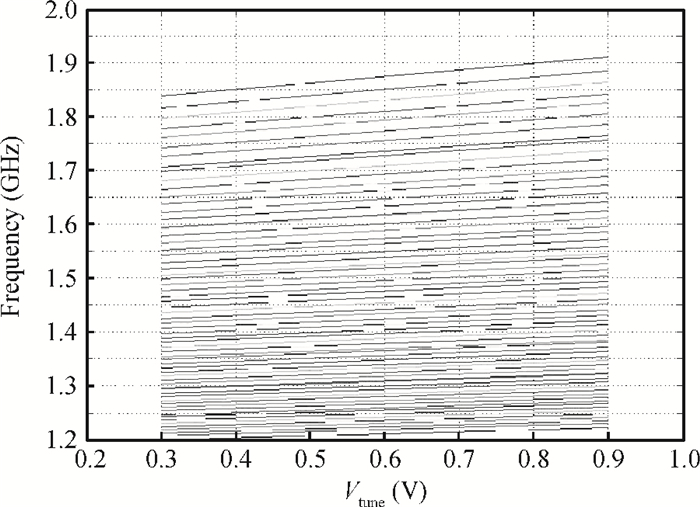

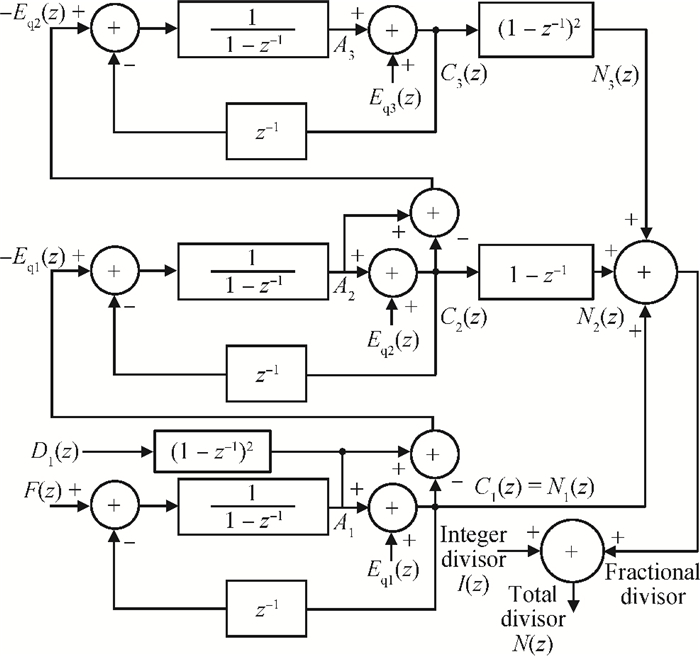

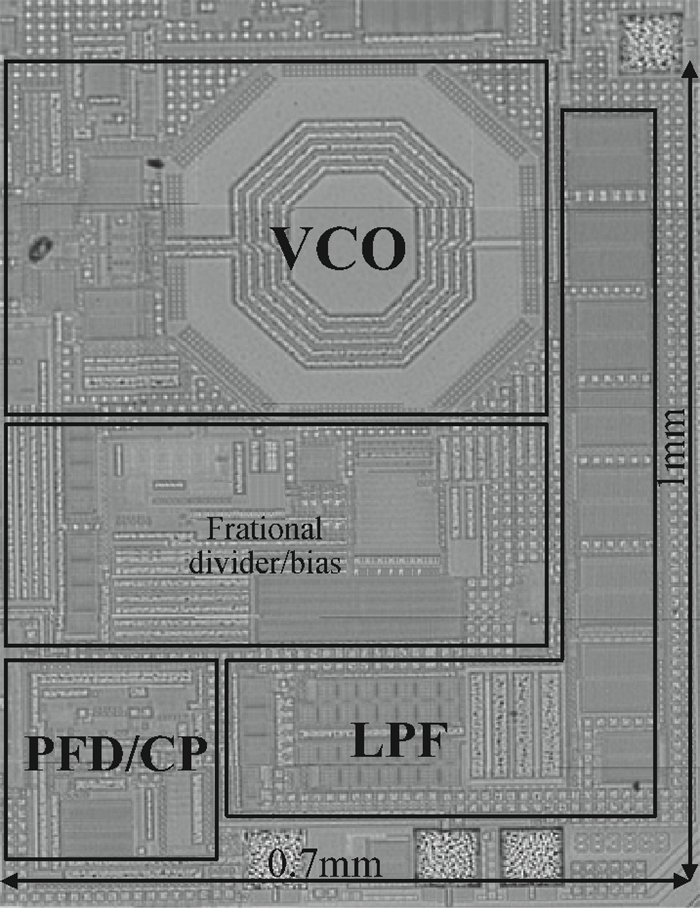

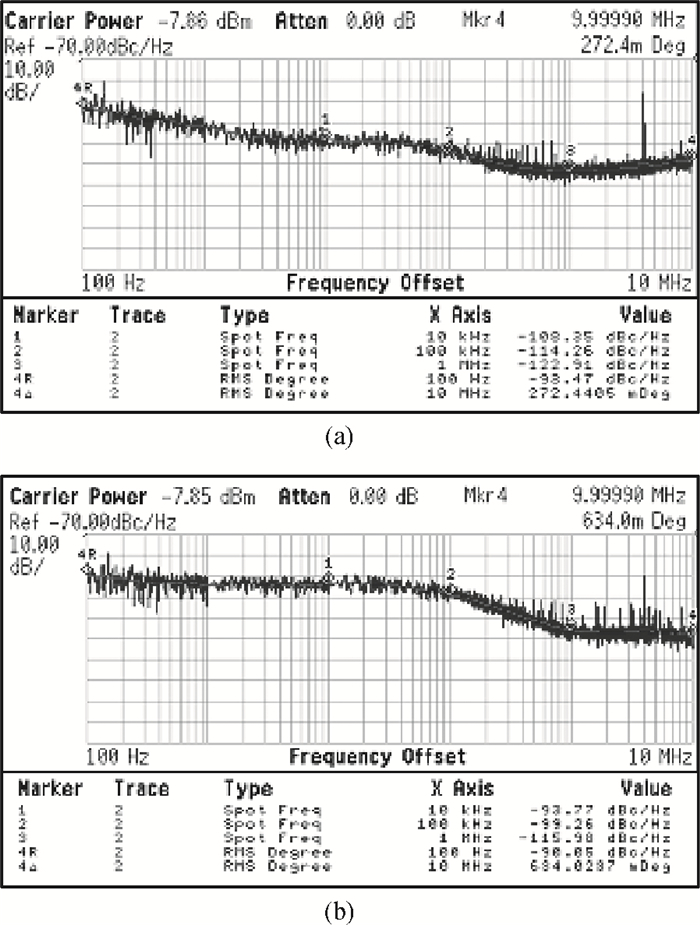

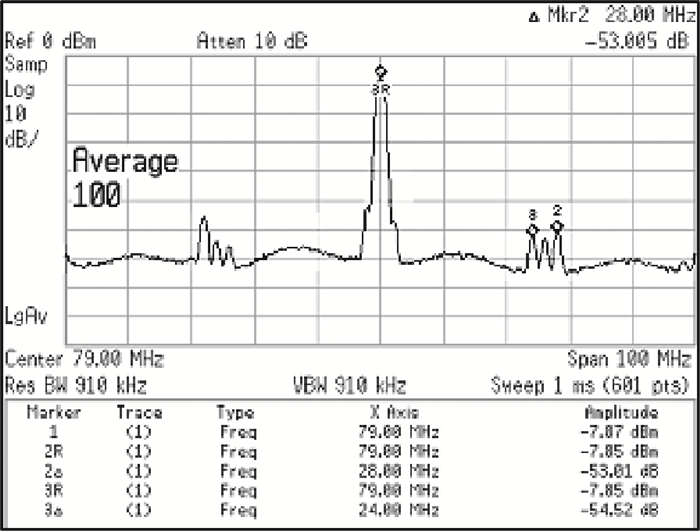

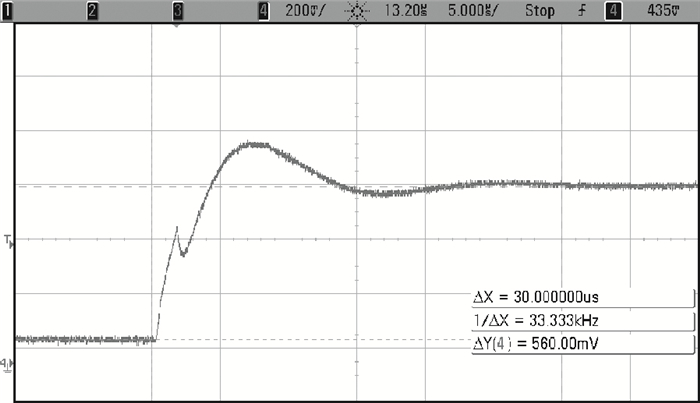

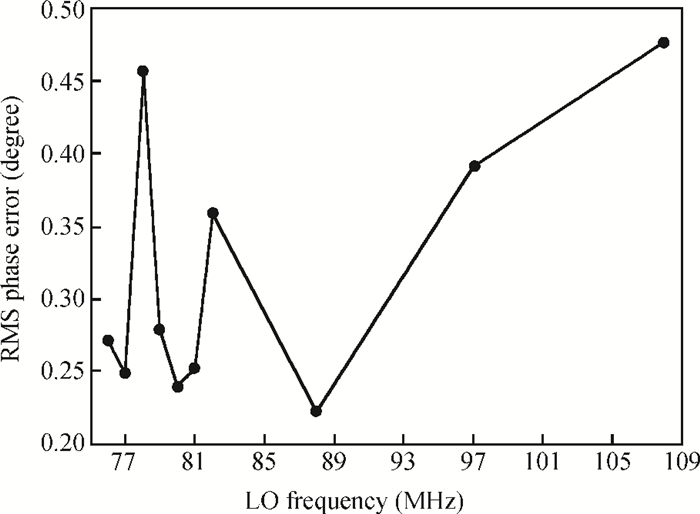

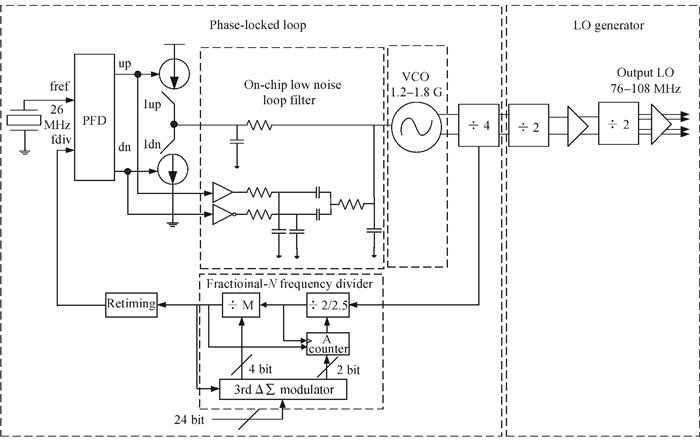

A Δ Σ fractional-N frequency synthesizer fabricated in a 130 nm CMOS technology is presented for the application of an FM tuner. A low noise filter, occupying a small die area and decreasing the output noise, is integrated on a chip. A quantization noise suppression technique, using a reduced step size of the frequency divider, is also adopted. The proposed synthesizer needs no off-chip components and occupies an area of 0.7 mm2. The in-band phase noise (from 10 to 100 kHz) below -108 dBc/Hz and out-of-band phase noise of -122.9 dBc/Hz (at 1 MHz offset) are measured with a loop bandwidth of 200 kHz. The quantization noise suppression technique reduces the in-band and out-of band phase noise by 15 dB and 7 dB respectively. The integrated RMS phase error is no more than 0.48°. The proposed synthesizer consumes a total power of 7.4 mW and the frequency resolution is less than 1 Hz. -

References

[1] Ruffieux D, Melly T, Peiris V, et al. A 1.2-mW RDS receiver for portable applications. IEEE J Solid-State Circuits, 2004, 39(7): 995 doi: 10.1109/JSSC.2004.829971[2] Jones C G, Beghein C C. Low noise filter. US Patent, No.6891412 B1, 2005[3] Chen Mingyi, Chu Xiaojie, Yu Peng, et al. A 55 nm CMOS Δ Σ fractional-N frequency synthesizer for WLAN transceivers with low noise filter. Journal of Semiconductors, 2013, 34(10): 105001 doi: 10.1088/1674-4926/34/10/105001[4] Jin J, Liu X, Mo T, et al. Quantization noise suppression in fractional-N PLLs utilizing glitch-free phase switching multi-modulus frequency divider. IEEE Trans Circuits Syst, 2012, 59(5): 926 doi: 10.1109/TCSI.2012.2189042[5] Yang Y C, Yu S A, Wang T, et al. A dual-mode truly modular programmable fractional divider based on a 1/1.5 divider cell. IEEE Microw Wireless Compon Lett, 2005, 15(11): 754 doi: 10.1109/LMWC.2005.858978[6] Yang Y C, Yu S A, Liu Y H, et al. A quantization noise suppression technique for Δ Σ fractional-N frequency synthesizers. IEEE J Solid -State Circuits, 2006, 41(11): 2500 doi: 10.1109/JSSC.2006.883325[7] Lou Liheng, Sun Lingling, Gao Haijun, et al. A wideband frequency synthesizer with VCO and AFC co-design for fast calibration. Journal of Semiconductors, 2013, 34(1): 015008 doi: 10.1088/1674-4926/34/1/015008[8] Shin J, Shin H. A 1.9-3.8 GHz delta-sigma fractional-N PLL frequency synthesizer with fast auto-calibration of loop bandwidth and VCO frequency. IEEE J Solid-State Circuits, 2012, 47(3): 665 doi: 10.1109/JSSC.2011.2179733 -

Proportional views

DownLoad:

DownLoad: