| Citation: |

Tianqi Liu, Chao Geng, Zhangang Zhang, Fazhan Zhao, Song Gu, Teng Tong, Kai Xi, Gang Liu, Zhengsheng Han, Mingdong Hou, Jie Liu. Impact of temperature on single event upset measurement by heavy ions in SRAM devices[J]. Journal of Semiconductors, 2014, 35(8): 084008. doi: 10.1088/1674-4926/35/8/084008

****

T Q Liu, C Geng, Z G Zhang, F Z Zhao, S Gu, T Tong, K Xi, G Liu, Z S Han, M D Hou, J Liu. Impact of temperature on single event upset measurement by heavy ions in SRAM devices[J]. J. Semicond., 2014, 35(8): 084008. doi: 10.1088/1674-4926/35/8/084008.

|

Impact of temperature on single event upset measurement by heavy ions in SRAM devices

DOI: 10.1088/1674-4926/35/8/084008

More Information

-

Abstract

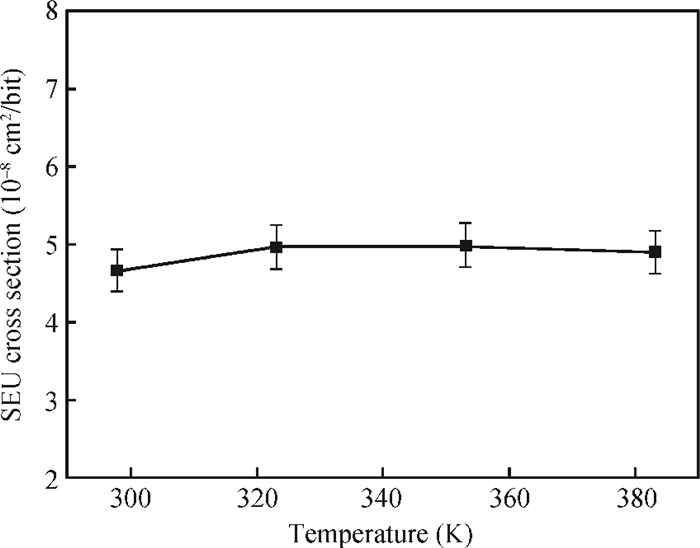

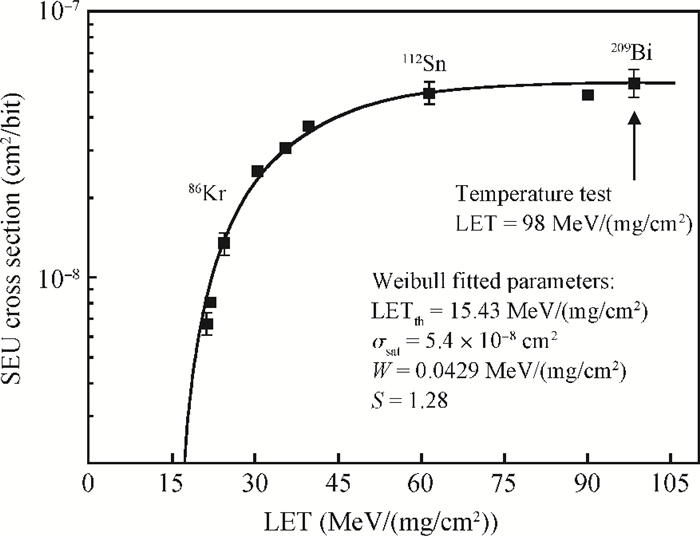

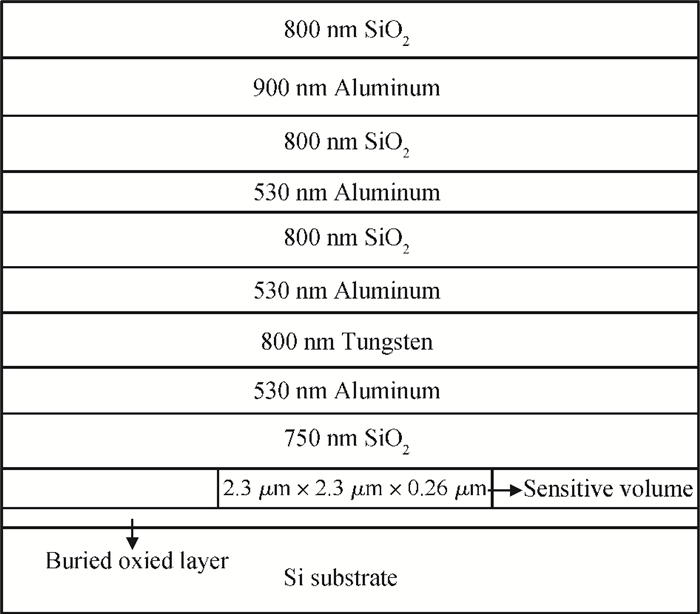

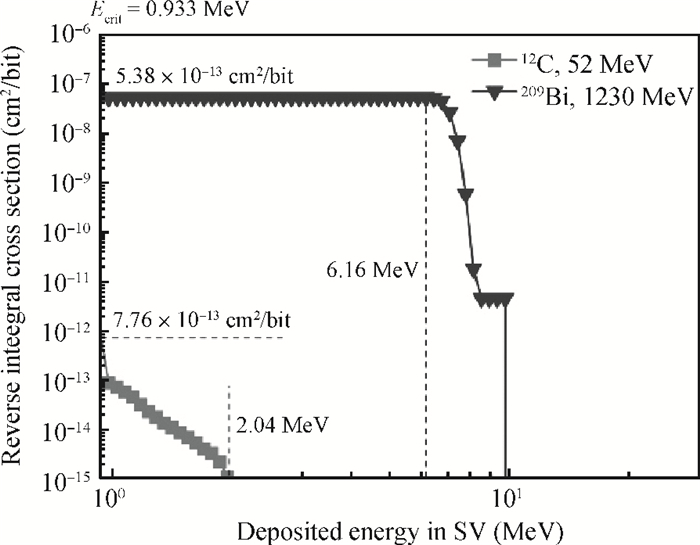

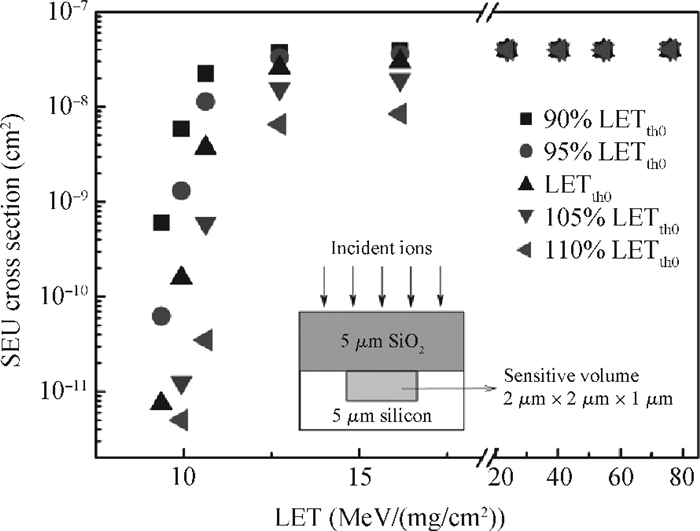

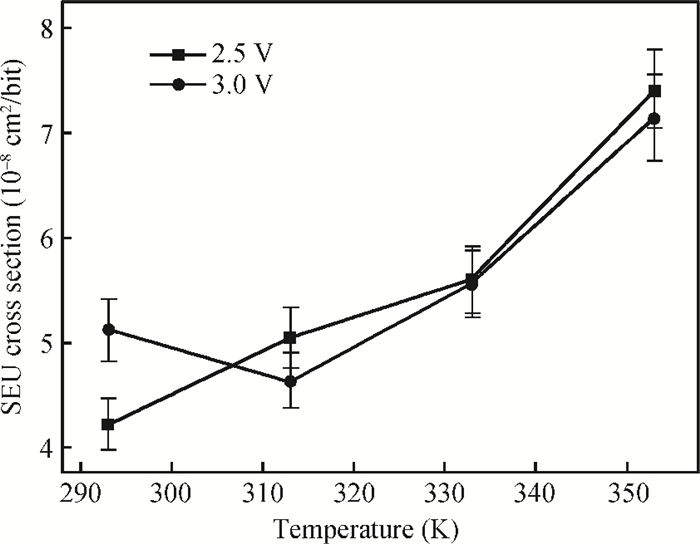

The temperature dependence of single event upset (SEU) measurement both in commercial bulk and silicon on insulator (SOI) static random access memories (SRAMs) has been investigated by experiment in the Heavy Ion Research Facility in Lanzhou (HIRFL). For commercial bulk SRAM, the SEU cross section measured by 12C ions is very sensitive to the temperature. The temperature test of SEU in SOI SRAM was conducted by 209Bi and 12C ions, respectively, and the SEU cross sections display a remarkable growth with the elevated temperature for 12C ions but keep constant for 209Bi ions. The impact of temperature on SEU measurement was analyzed by Monte Carlo simulation. It is revealed that the SEU cross section is significantly affected by the temperature around the threshold linear energy transfer of SEU occurrence. As the SEU occurrence approaches saturation, the SEU cross section gradually exhibits less temperature dependency. Based on this result, the experimental data measured in HIRFL was analyzed, and then a reasonable method of predicting the on-orbit SEU rate was proposed. -

References

[1] Zhang Z G, Liu J, Hou M D, et al. Augular dependence of multiple-bit upset response in static random access memories under heavy ion irradiation. Chin Phys B, 2013, 22(8):086102 doi: 10.1088/1674-1056/22/8/086102[2] Wang Lixin, Lu Jiang, Liu Gang, et al. Simulation of the sensitive region to SEGR in power MOSFETs. Journal of Semiconductors, 2012, 33(5):054008 doi: 10.1088/1674-4926/33/5/054008[3] Yang S Y, Cao Z, Da D A, et al. Equivalent properties of single event burnout induced by different sources. Chin Phys B, 2009, 33(5):369 doi: 10.1088/1674-1137/33/5/010[4] Liu Biwei, Chen Shuming, Liang Bin. Temperature dependence of charge sharing and MBU sensitivity induced by a heavy ion. Journal of Semiconductors, 2009, 30(7):074005 doi: 10.1088/1674-4926/30/7/074005[5] Li Y H, He C H, Zhao F Z, et al. Experimental study on heavy ion single event effects in SOI SRAMs. Nucl Instr And Meth B, 2009, 267:83 doi: 10.1016/j.nimb.2008.10.082[6] Zhang Q X, Hou M D, Liu J, et al. The impact of incidentangle on multiple-bit upset in SRAMs. Nucl Instr and Meth B, 2003, 209:367 doi: 10.1016/S0168-583X(02)02026-8[7] Guo H X, Luo Y H, Yao Z B, et al. Experimental research of SEU and SEL in high density SRAMs with sub-micron feature sizes. Atomic Energy Science and Technology, 2010, 44(12):1498 http://en.cnki.com.cn/Article_en/CJFDTOTAL-YZJS201012018.htm[8] Johnston A H, Hughlock B W, Baze M P, et al. The effect of temperature on single-particle latchup. IEEE Trans Nucl Sci, 1991, 38(6):1435 doi: 10.1109/23.124129[9] Iwata H, Ohzone T. Numerical simulation of single event latchup in the temperature range of 77-450 K. IEEE Trans Nucl Sci, 1995, 42(3):148 doi: 10.1109/23.387354[10] Guo G, Hirao T, Laird J S, et al. Temperature dependence of single-event transient current induced by heavy-ion microbeam on p+/n/n+ epilayer junctions. IEEE Trans Nucl Sci, 2004, 51(5):2834 doi: 10.1109/TNS.2004.835058[11] Stapor W J, McDonald P T, Swickert S L, et al. Low temperature proton induced upsets in NMOS resistive load static RAM. IEEE Trans Nucl Sci, 1988, 35(6):1596 doi: 10.1109/23.25504[12] Sanathanamurthy S. Simulated temperature dependency of SEU sensitivity in a 0.5μm CMOS SRAM. Master Thesis, Vanderbilt University, 2008[13] Alles M L, Masengill L W, Kerns S E, et al. Effect of temperature dependent bipolar gain distribution on SEU vulnerability of SOI CMOS SRAMs. IEEE International SOI Conference Proceedings, 1992:96 http://ieeexplore.ieee.org/xpls/abs_all.jsp?arnumber=664812[14] Truyen D, Boch J, Sagnes B, et al. Temperature effect on heavy-ion induced parasitic current on SRAM by device simulation:effect on SEU sensitivity. IEEE Trans Nucl Sci, 2007, 54(4):1025 doi: 10.1109/TNS.2007.894298[15] Liu B W, Chen S M, Liang B, et al. Temperature dependency of charge sharing and MBU sensitivity in 130-nm CMOS technology. IEEE Trans Nucl Sci, 2009, 56(4):2473 doi: 10.1109/TNS.2009.2022267[16] Weller R A, Mendenhall M H, Reed R A, et al. Monte Carlo simulation of single event effects. IEEE Trans Nucl Sci, 2010, 57(4):1726 doi: 10.1109/TNS.2010.2044807[17] Mendenhall M H, Weller R A. A probability conserving cross section biasing mechanism for variance reduction in Monte Carlo particle transport calculations. Nucl Inst And Meth A, 2011, 667:38 http://www.sciencedirect.com/science/article/pii/S0168900211021541[18] NcNutlty P J, Bearnvais W I, Roth D R. Determination of SEU parameters of NMOS and CMOS SRAMs. IEEE Trans Nucl Sci, 1991, 38(6):1463 doi: 10.1109/23.124133[19] Warren K M, Weller R A, Mendenhall M H, et al. The contribution of nuclear reactions to heavy ion single event upset cross section measurements in a high-density SEU hardened SRAM. IEEE Trans Nucl Sci, 2005, 52(6):2125 doi: 10.1109/TNS.2005.860677[20] Geng C, Liu J, Xi K, et al. Monte Carlo evaluation of spatial multiple-bit upset sensitivity to oblique incidence. Chin Phys B, 2013, 22(5):059501 doi: 10.1088/1674-1056/22/5/059501 -

Proportional views

DownLoad:

DownLoad: