| Citation: |

Feng Zhang, Yusong Qiu. A 3 Gb/s multichannel transceiver in 65 nm CMOS technology[J]. Journal of Semiconductors, 2015, 36(1): 015003. doi: 10.1088/1674-4926/36/1/015003

****

F Zhang, Y S Qiu. A 3 Gb/s multichannel transceiver in 65 nm CMOS technology[J]. J. Semicond., 2015, 36(1): 015003. doi: 10.1088/1674-4926/36/1/015003.

|

A 3 Gb/s multichannel transceiver in 65 nm CMOS technology

DOI: 10.1088/1674-4926/36/1/015003

More Information

-

Abstract

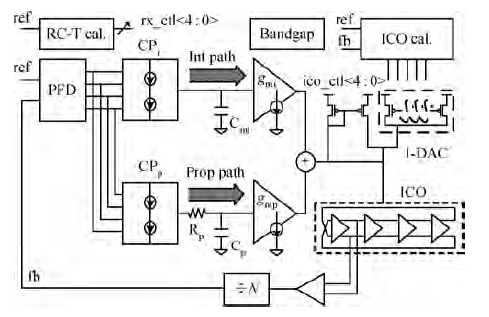

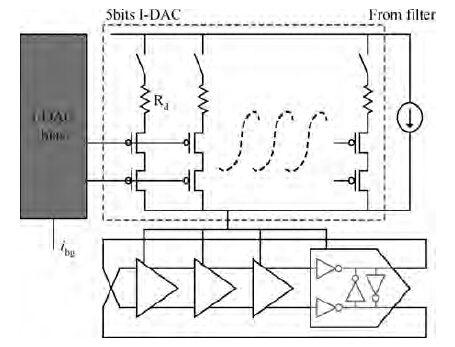

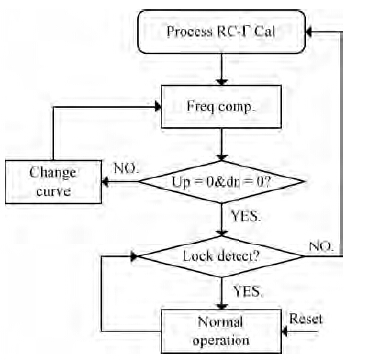

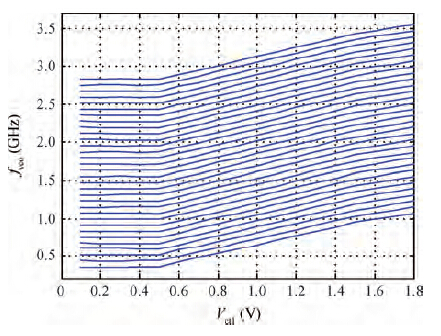

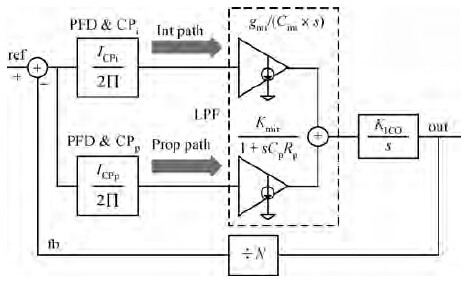

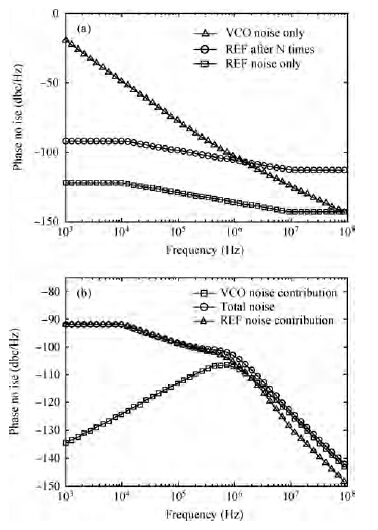

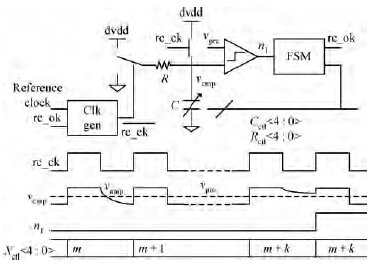

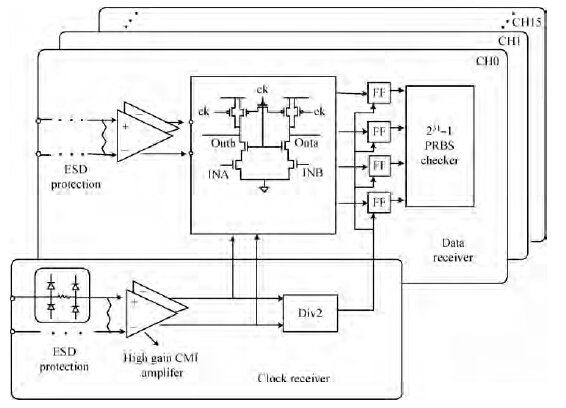

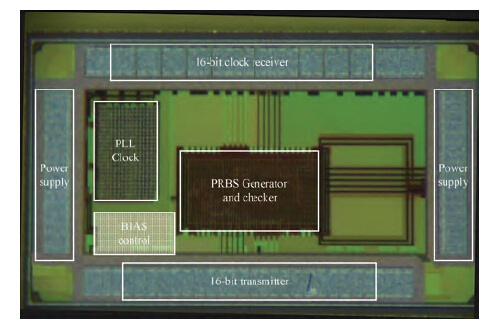

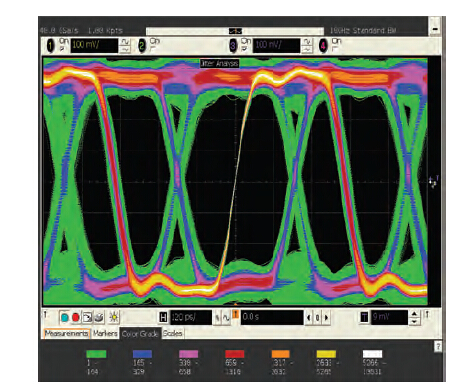

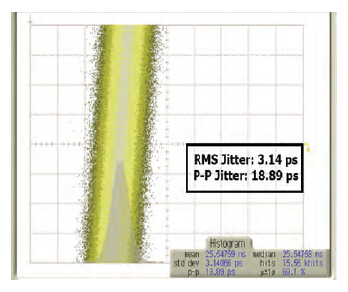

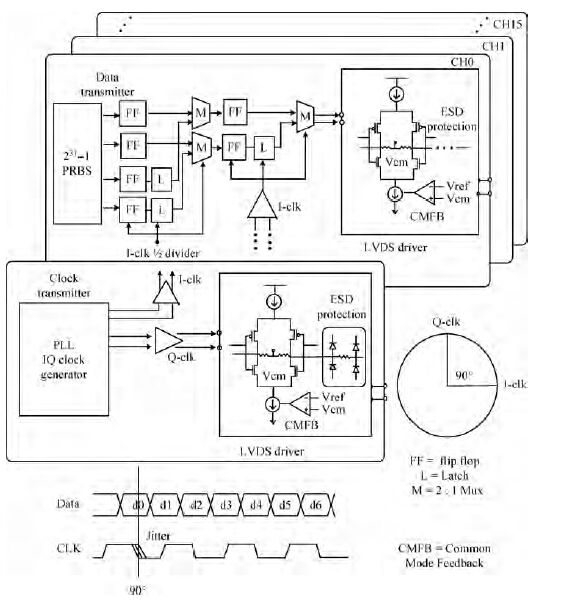

This paper describes a 65 nm 16-bit parallel transceiver IP macro, whose rate is 3 Gb/s with a 5 pF load including the HBM 2000 V ESD protection. Equalizers and clock data recovery modules, CRC checkers and 8 b/10 b encoders are not added in the design for reducing the latency, and the whole latency is 7 ns without cables. Since the transceiver has many robust features including a process, voltage and temperature independent phase-locked loop with calibrations, the low skew differential clock tree, and a stable current mode driver with common mode feedback, the transceiver can work properly at different process corners and extreme temperatures, and also can tolerate 20% power supply variations. The transceiver can be applied for the interface of sub-100 nm high performance processors, which require low latency and high stability. The transceiver shows a bitter error ratio of less than 10-15 at 3 Gbps.-

Keywords:

- transceiver,

- process variation,

- low latency,

- PLL

-

References

[1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] -

Proportional views

DownLoad:

DownLoad: