| Citation: |

Shiromani Balmukund Rahi, Bahniman Ghosh, Bhupesh Bishnoi. Temperature effect on hetero structure junctionless tunnel FET[J]. Journal of Semiconductors, 2015, 36(3): 034002. doi: 10.1088/1674-4926/36/3/034002

****

S B Rahi, B Ghosh, B Bishnoi. Temperature effect on hetero structure junctionless tunnel FET[J]. J. Semicond., 2015, 36(3): 034002. doi: 10.1088/1674-4926/36/3/034002.

|

Temperature effect on hetero structure junctionless tunnel FET

DOI: 10.1088/1674-4926/36/3/034002

More Information

-

Abstract

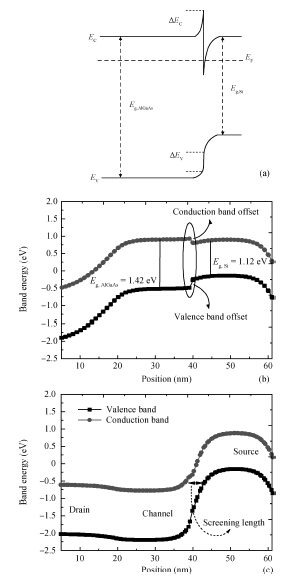

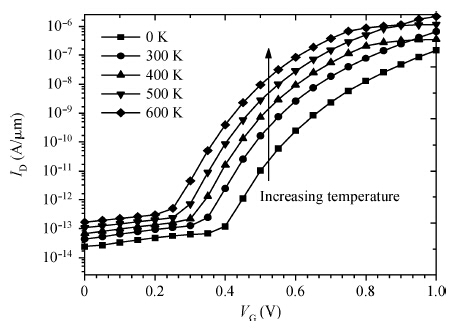

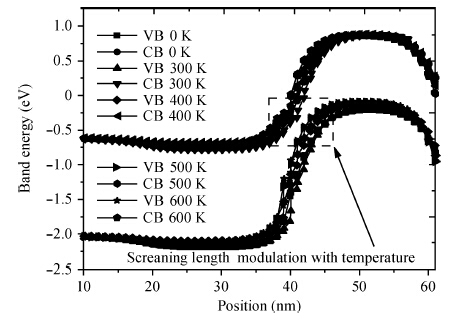

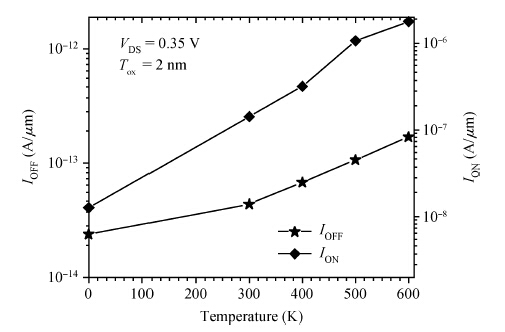

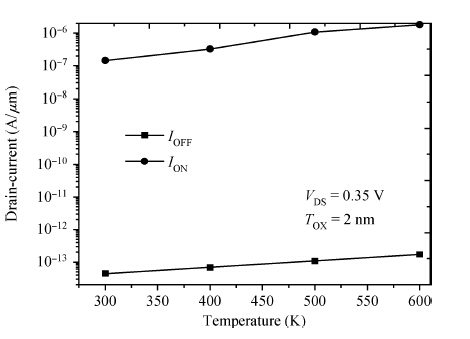

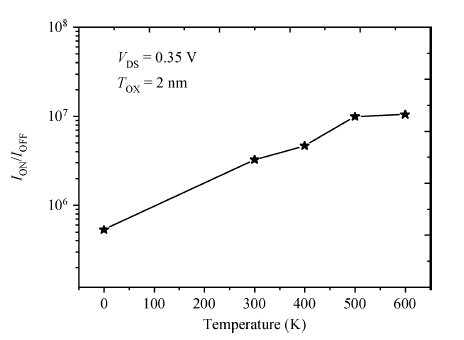

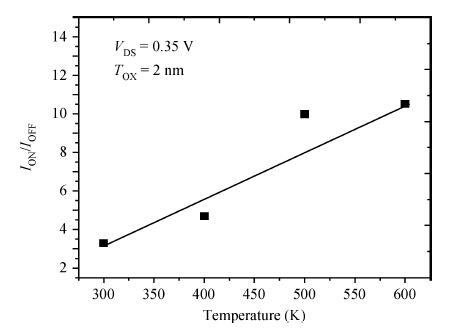

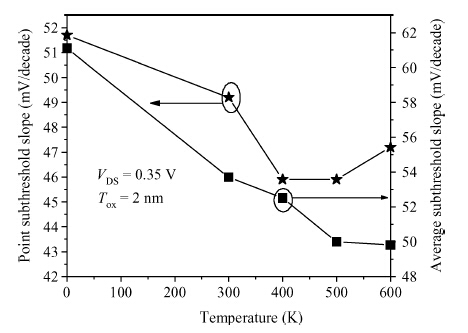

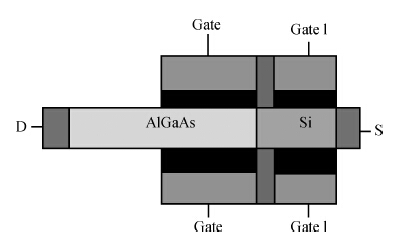

For the first time, we investigate the temperature effect on AlGaAs/Si based hetero-structure junctionless double gate tunnel field effect transistor. Since junctionless tunnel FET is an alternative substitute device for ultra scaled deep-submicron CMOS technology, having very good device characteristics such as an improved subthreshold slope (<60 mV/decade at 300 K) and very small static leakage currents. The improved subthreshold slope and static leakage current confirms that it will be helpful for the development of future low power switching circuits. The 2-D computer based simulation results show that OFF-state leakage current is almost temperature independent for the proposed device structure. -

References

[1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] [26] [27] [28] [29] [30] [31] [32] -

Proportional views

DownLoad:

DownLoad: