| Citation: |

Tao Yang, Yu Jiang, Shengyou Liu, Guiliang Guo, Yuepeng Yan. A low-power CMOS WIA-PA transceiver with a high sensitivity GFSK demodulator[J]. Journal of Semiconductors, 2015, 36(6): 065005. doi: 10.1088/1674-4926/36/6/065005

****

T Yang, Y Jiang, S Y Liu, G L Guo, Y P Yan. A low-power CMOS WIA-PA transceiver with a high sensitivity GFSK demodulator[J]. J. Semicond., 2015, 36(6): 065005. doi: 10.1088/1674-4926/36/6/065005.

|

A low-power CMOS WIA-PA transceiver with a high sensitivity GFSK demodulator

DOI: 10.1088/1674-4926/36/6/065005

More Information

-

Abstract

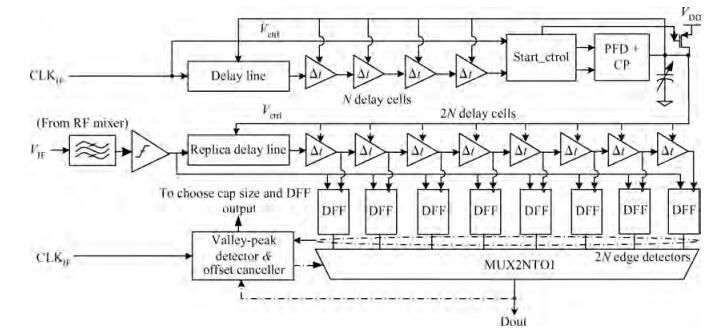

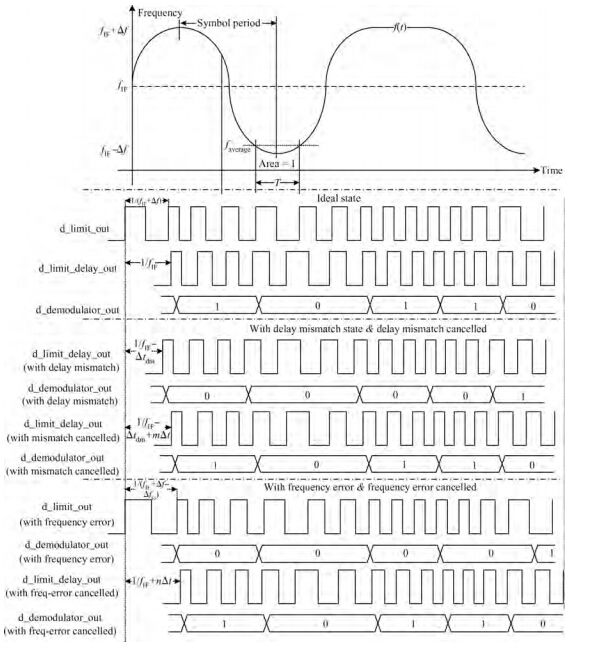

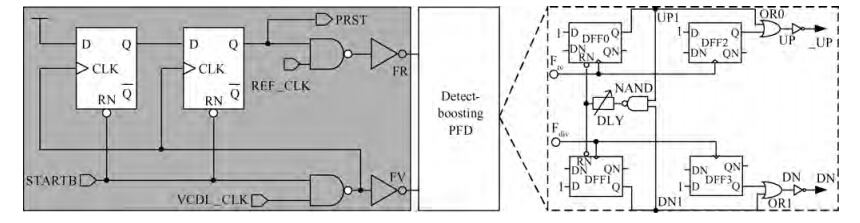

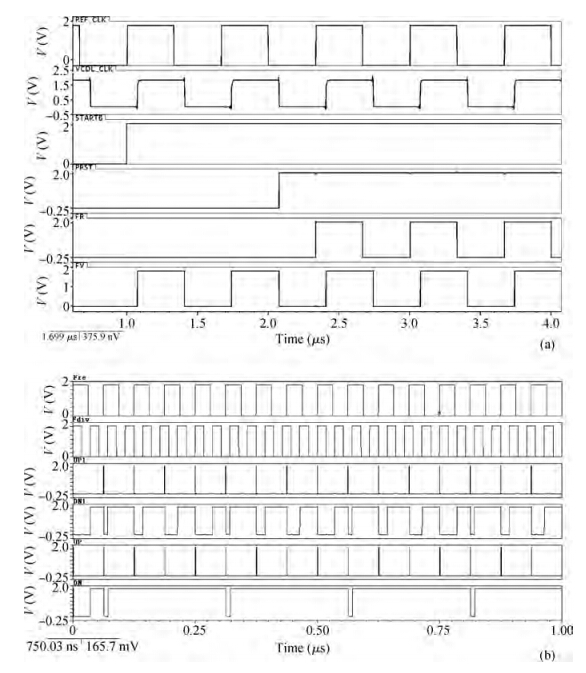

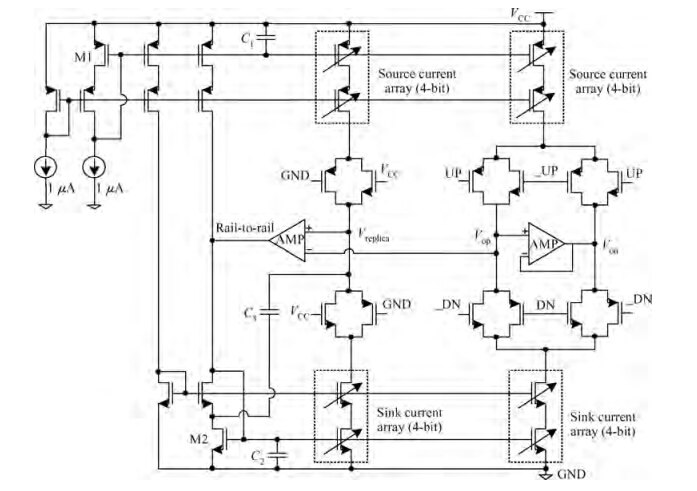

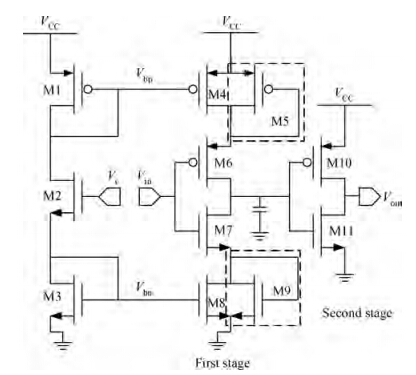

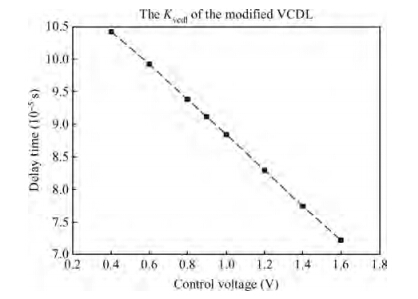

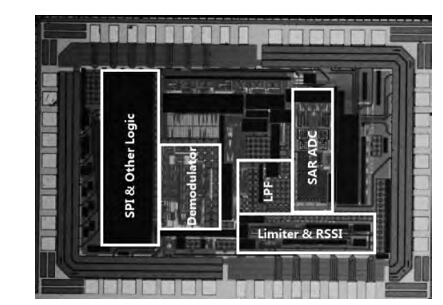

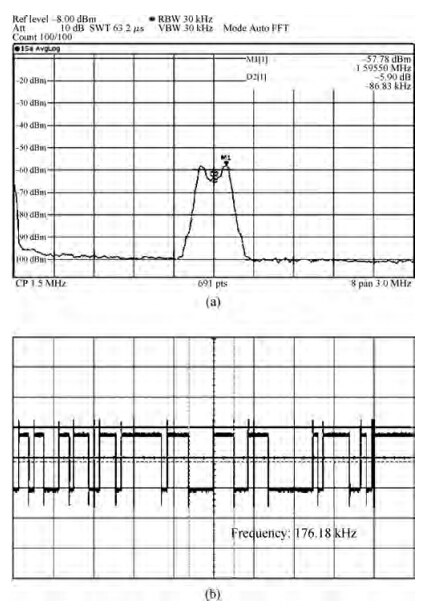

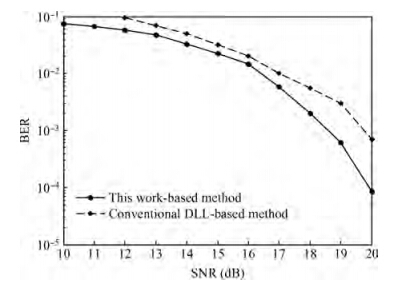

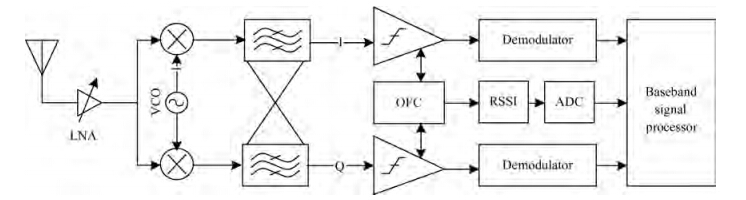

This paper presents a low power, high sensitivity Gaussian frequency shift keying (GFSK) demodulator with a flexible frequency offset canceling method for wireless networks for industrial automation process automation (WIA-PA) transceiver fabricated in 0.18 μm CMOS technology. The receiver uses a low-IF (1.5 MHz) architecture, and the transmitter uses a sigma delta PLL based modulation with Gaussian low-pass filter for low power consumption. The active area of the demodulator is 0.14 mm2. Measurement results show that the proposed demodulator operates without harmonic distortion, deals with ± 180 kHz frequency offset, needs SNR only 18.5 dB at 0.1% bit-error rate (BER), and consumes no more than 0.26 mA from a 1.8 V power supply.-

Keywords:

- GFSK,

- demodulator,

- DLL,

- charge pump,

- PFD,

- VCDL

-

References

[1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] -

Proportional views

DownLoad:

DownLoad: