| Citation: |

Tao Yang, Yu Jiang, Jie Li, Jiangfei Guo, Hua Chen, Jingyu Han, Guiliang Guo, Yuepeng Yan. A CMOS high resolution, process/temperature variation tolerant RSSI for WIA-PA transceiver[J]. Journal of Semiconductors, 2015, 36(8): 085005. doi: 10.1088/1674-4926/36/8/085005

****

T Yang, Y Jiang, J Li, J F Guo, H Chen, J Y Han, G L Guo, Y P Yan. A CMOS high resolution, process/temperature variation tolerant RSSI for WIA-PA transceiver[J]. J. Semicond., 2015, 36(8): 085005. doi: 10.1088/1674-4926/36/8/085005.

|

A CMOS high resolution, process/temperature variation tolerant RSSI for WIA-PA transceiver

DOI: 10.1088/1674-4926/36/8/085005

More Information

-

Abstract

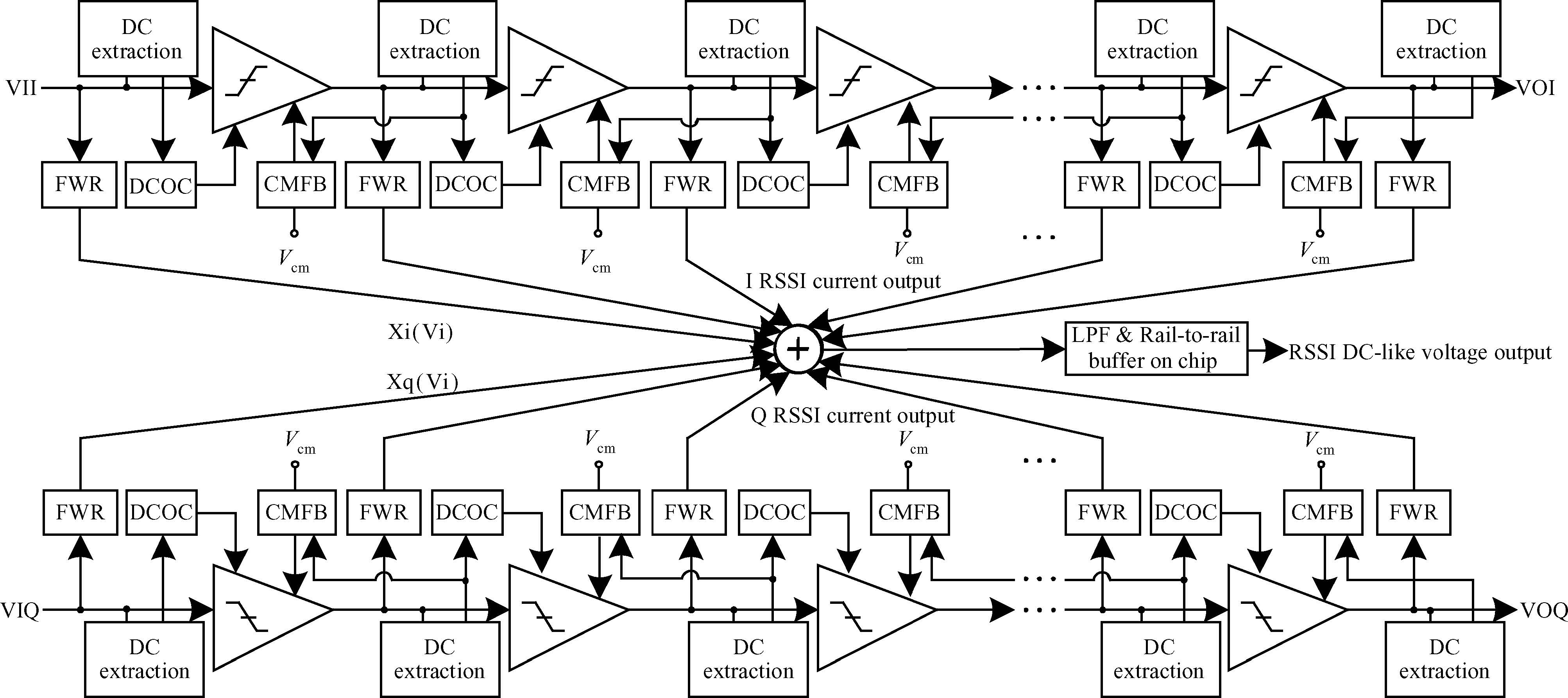

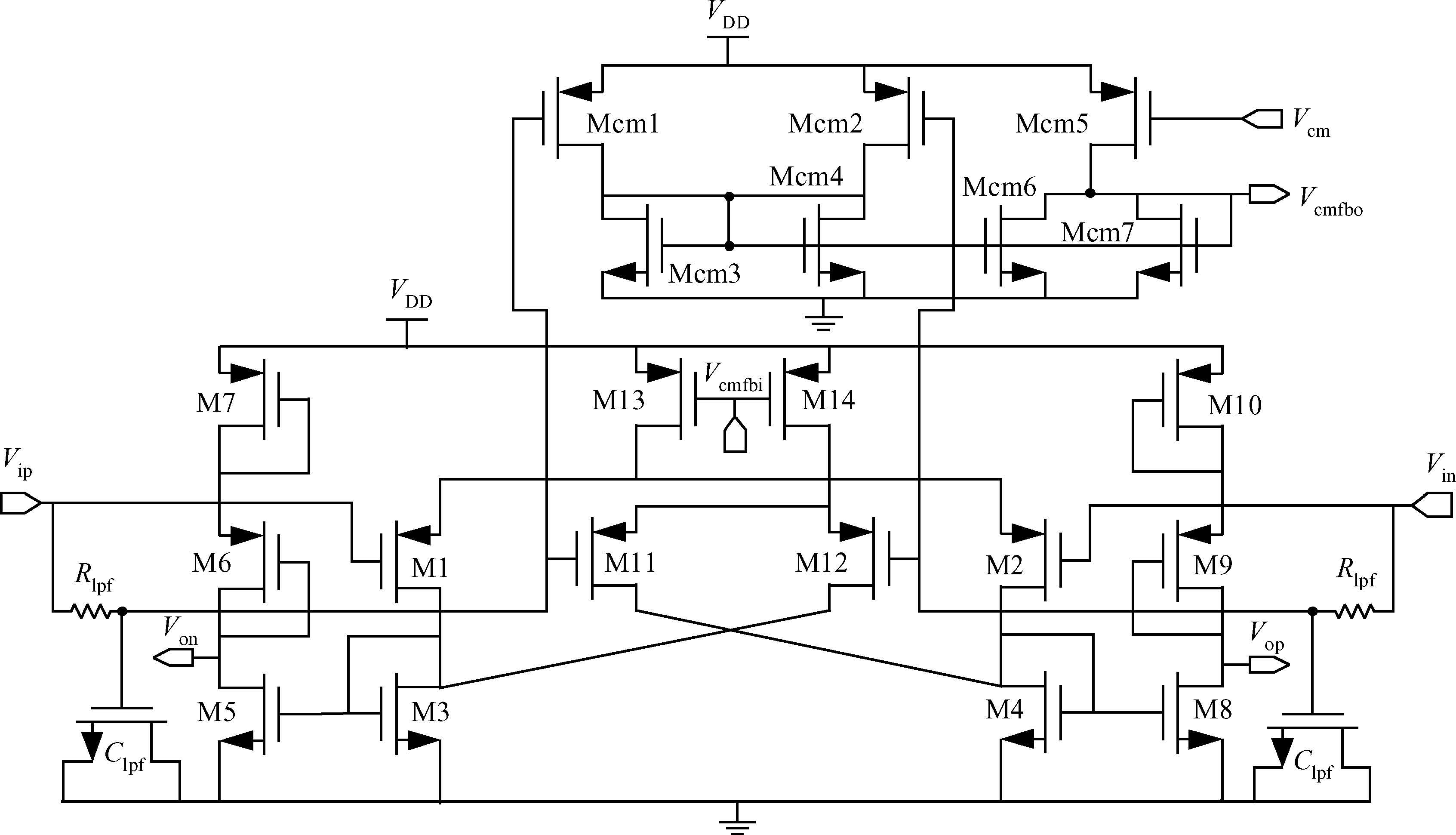

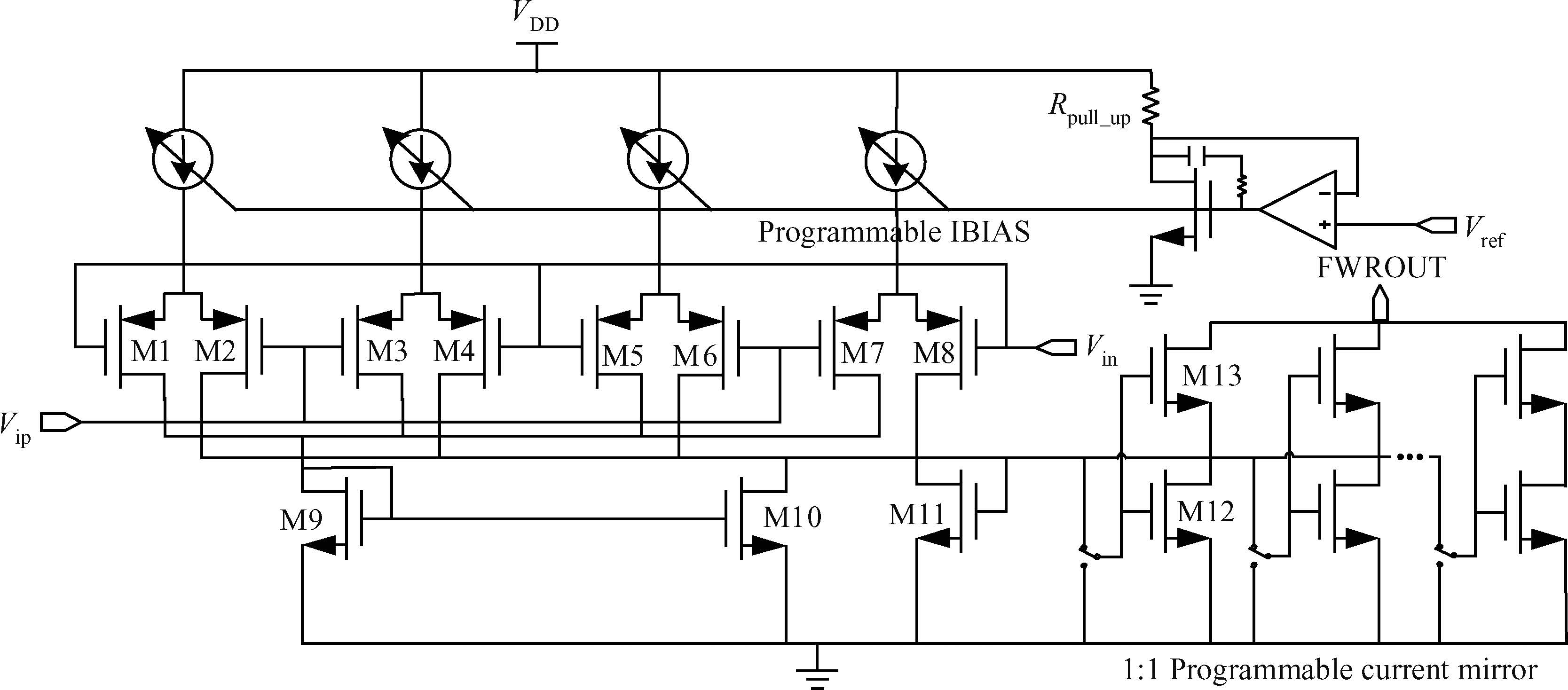

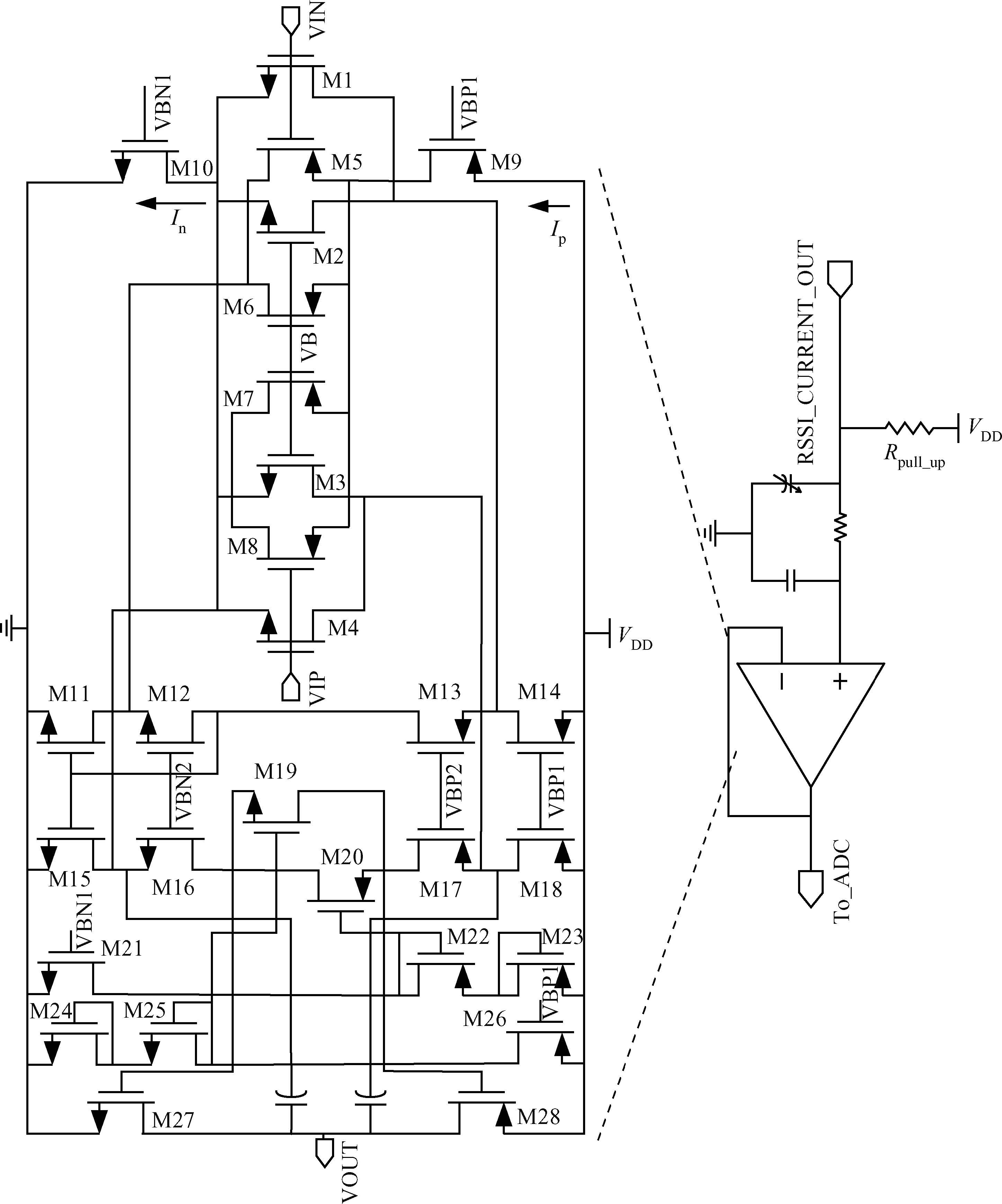

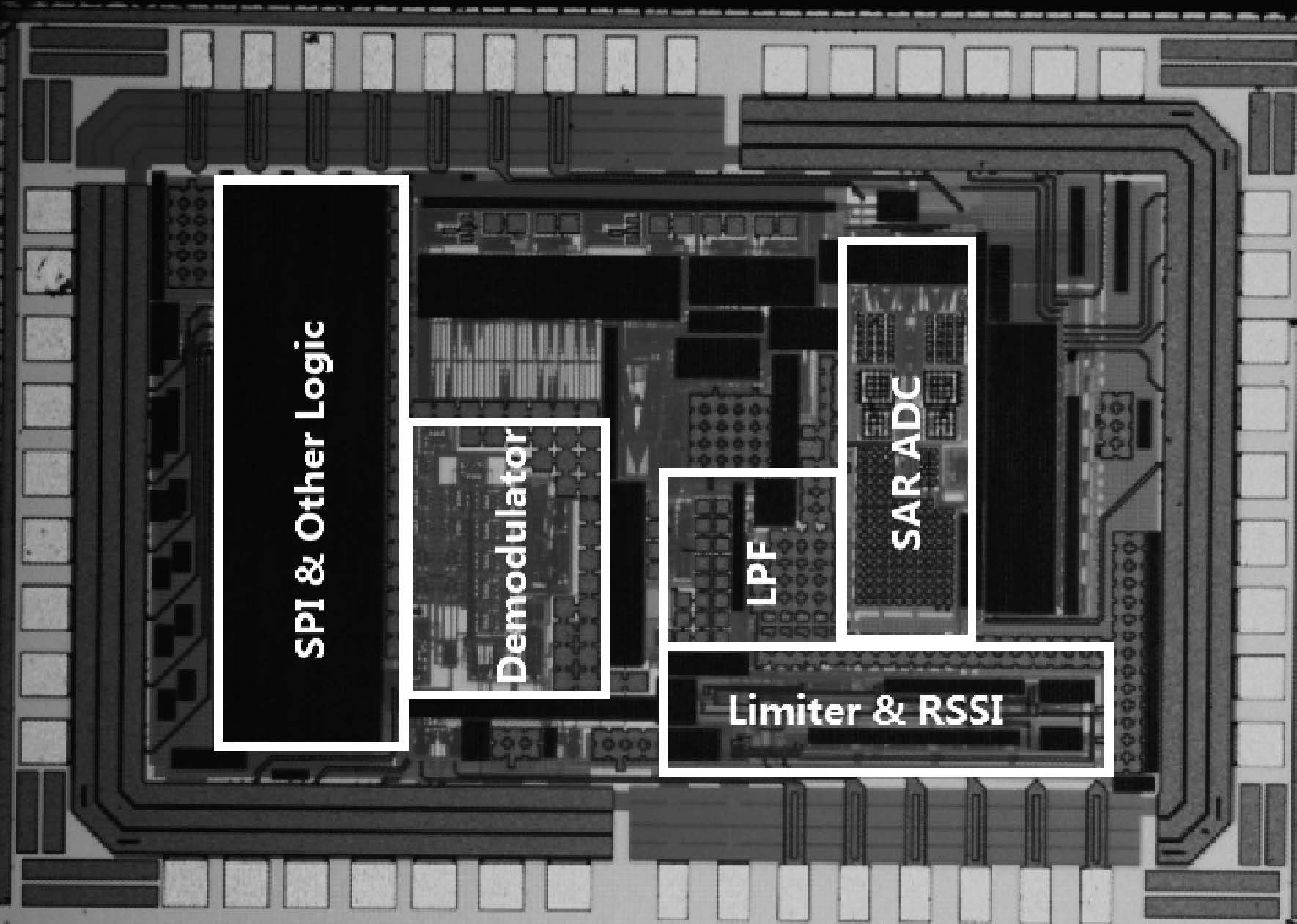

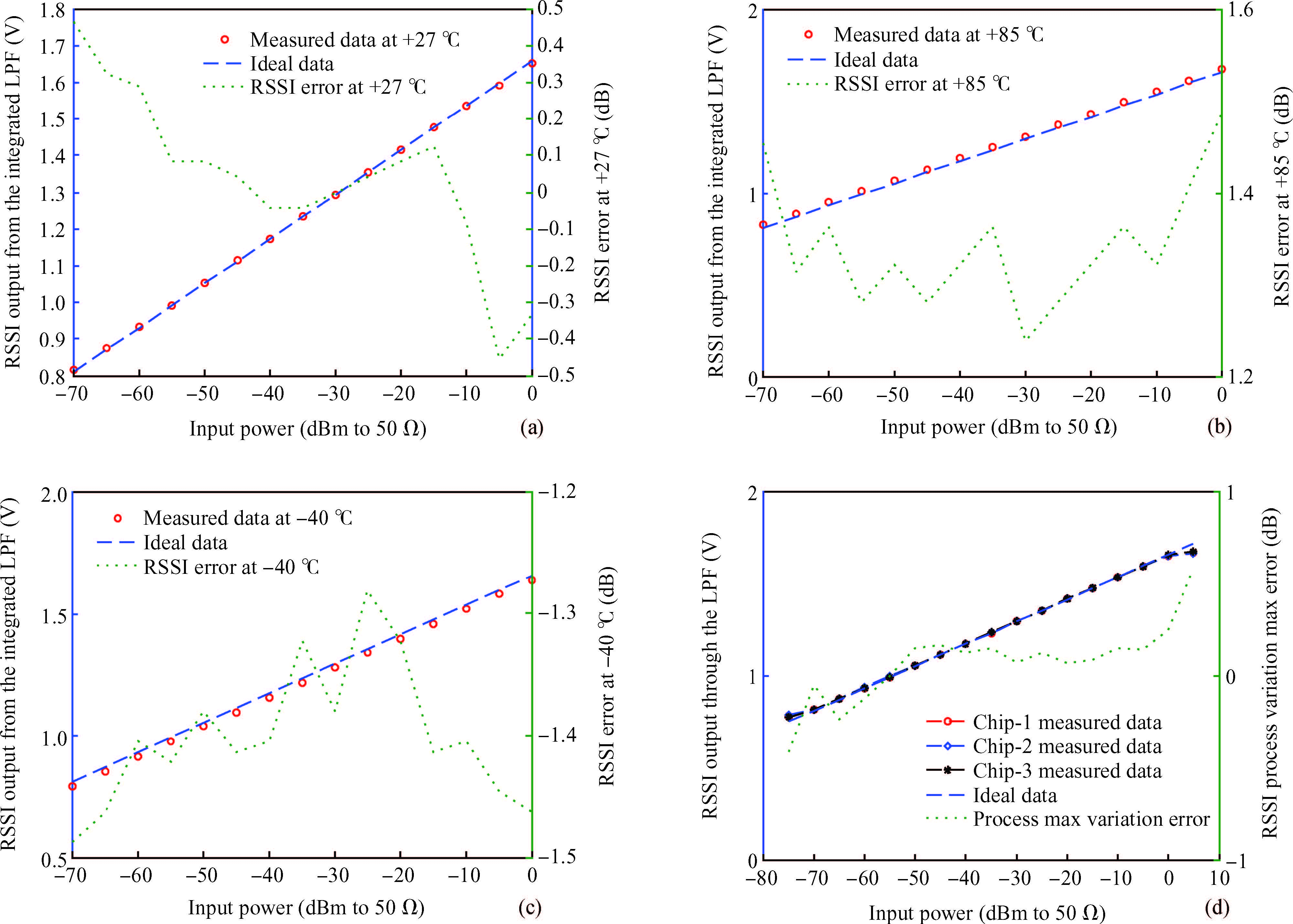

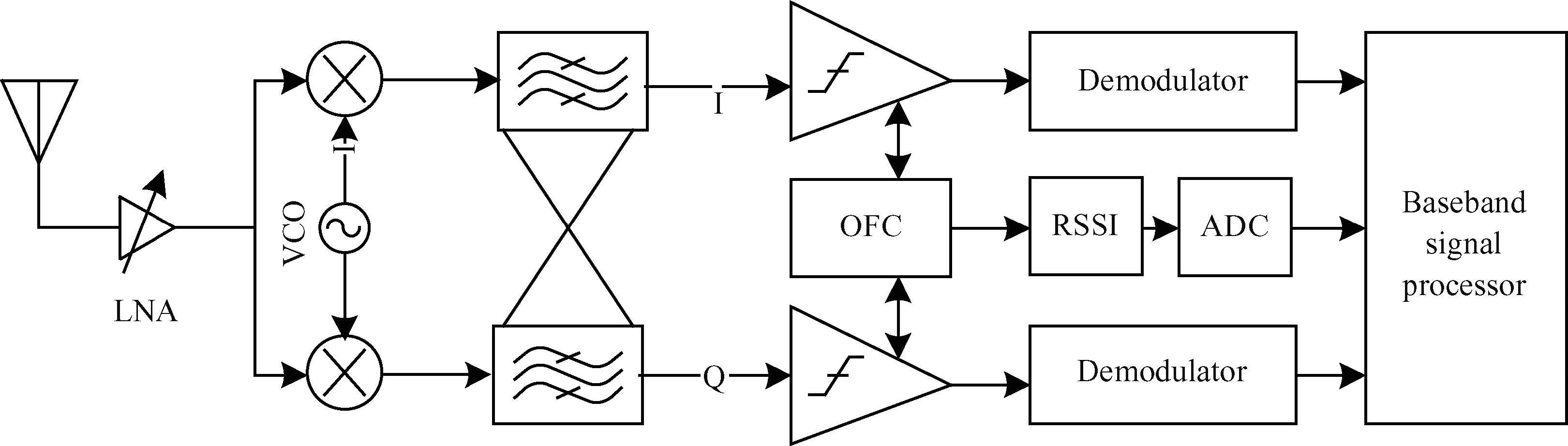

This paper presents a high resolution, process/temperature variation tolerant received signal strength indicator (RSSI) for wireless networks for industrial automation process automation (WIA-PA) transceiver fabricated in 0.18μm CMOS technology. The active area of the RSSI is 0.24 mm2. Measurement results show that the proposed RSSI has a dynamic range more than 70 dB and the linearity error is within ± 0.5 dB for an input power from -70 to 0 dBm (dBm to 50 Ω ), the corresponding output voltage is from 0.81 to 1.657 V and the RSSI slope is 12.1 mV/dB while consuming all of 2 mA from a 1.8 V power supply. Furthermore, by the help of the integrated compensation circuit, the proposed RSSI shows the temperature error within ± 1.5 dB from -40 to 85 ℃, and process variation error within ± 0.25 dB, which exhibits good temperature-independence and excellent robustness against process variation characteristics.-

Keywords:

- limiter,

- RSSI,

- high resolution,

- dynamic range,

- detection sensitivity,

- rail-to-rail buffer

-

References

[1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] -

Proportional views

DownLoad:

DownLoad: