| Citation: |

Swina Narula, Sujata Pandey. High performance 14-bit pipelined redundant signed digit ADC[J]. Journal of Semiconductors, 2016, 37(3): 035001. doi: 10.1088/1674-4926/37/3/035001

****

S Narula, Sujata Pandey. High performance 14-bit pipelined redundant signed digit ADC[J]. J. Semicond., 2016, 37(3): 035001. doi: 10.1088/1674-4926/37/3/035001.

|

High performance 14-bit pipelined redundant signed digit ADC

DOI: 10.1088/1674-4926/37/3/035001

More Information

-

Abstract

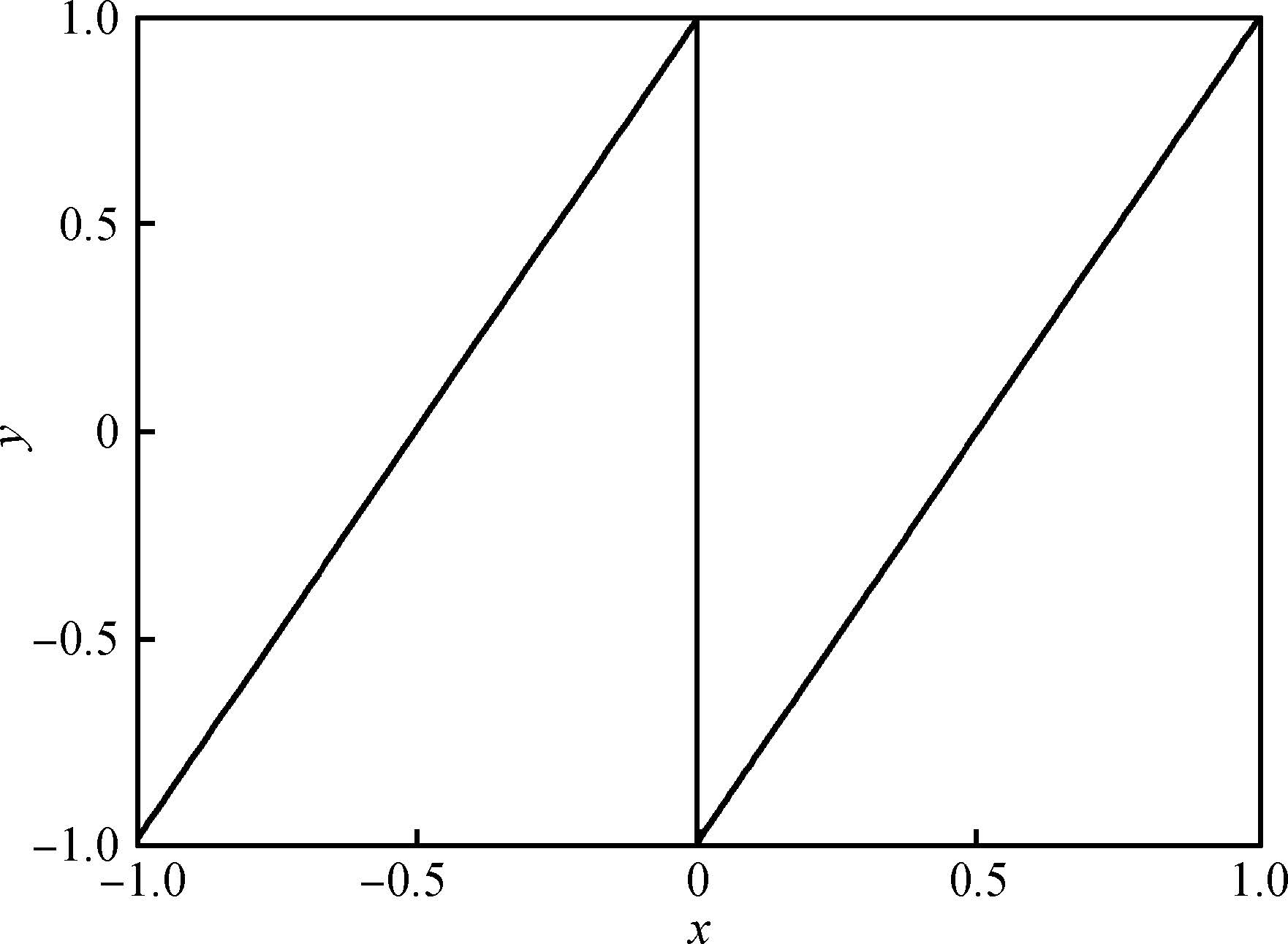

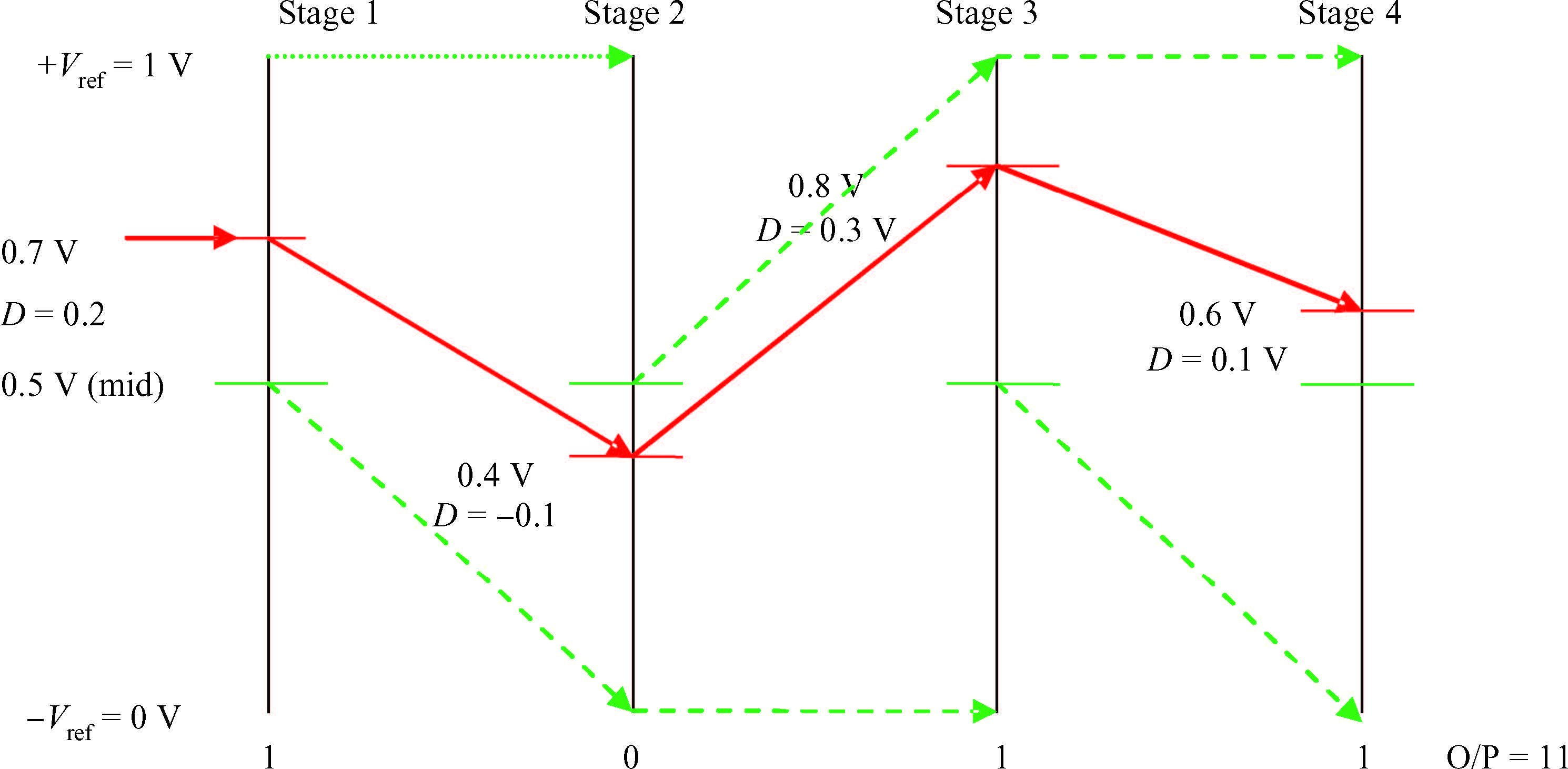

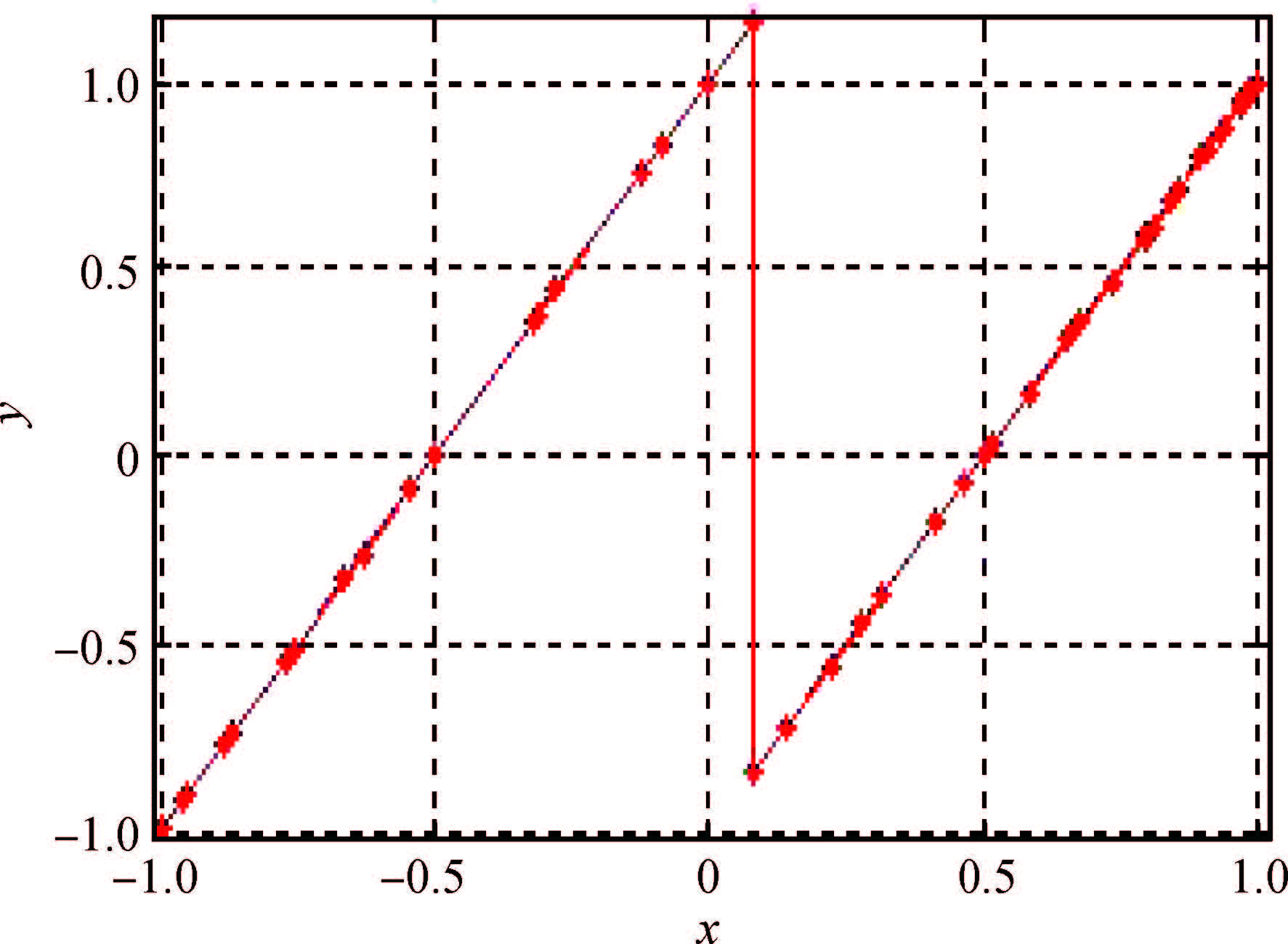

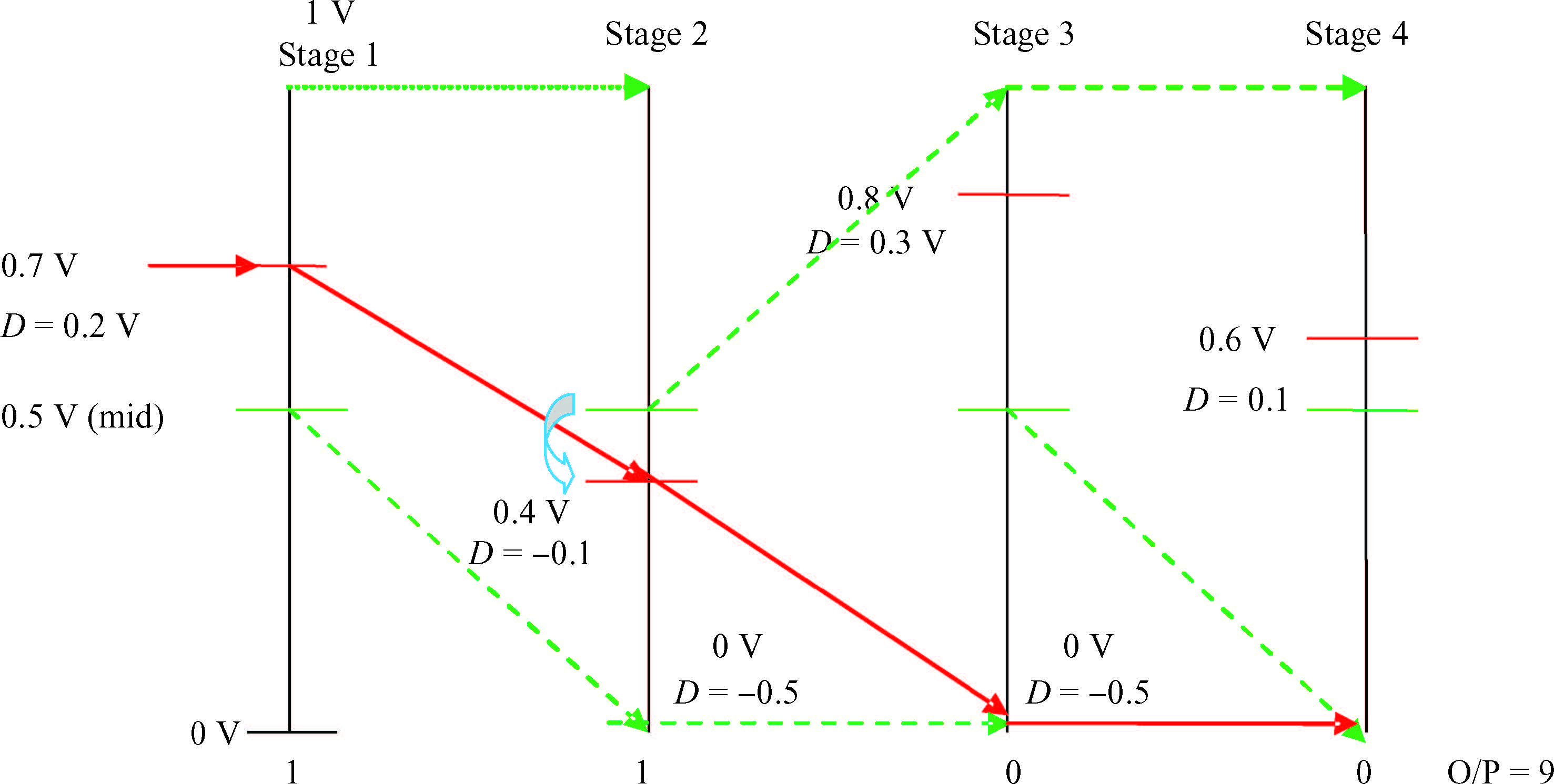

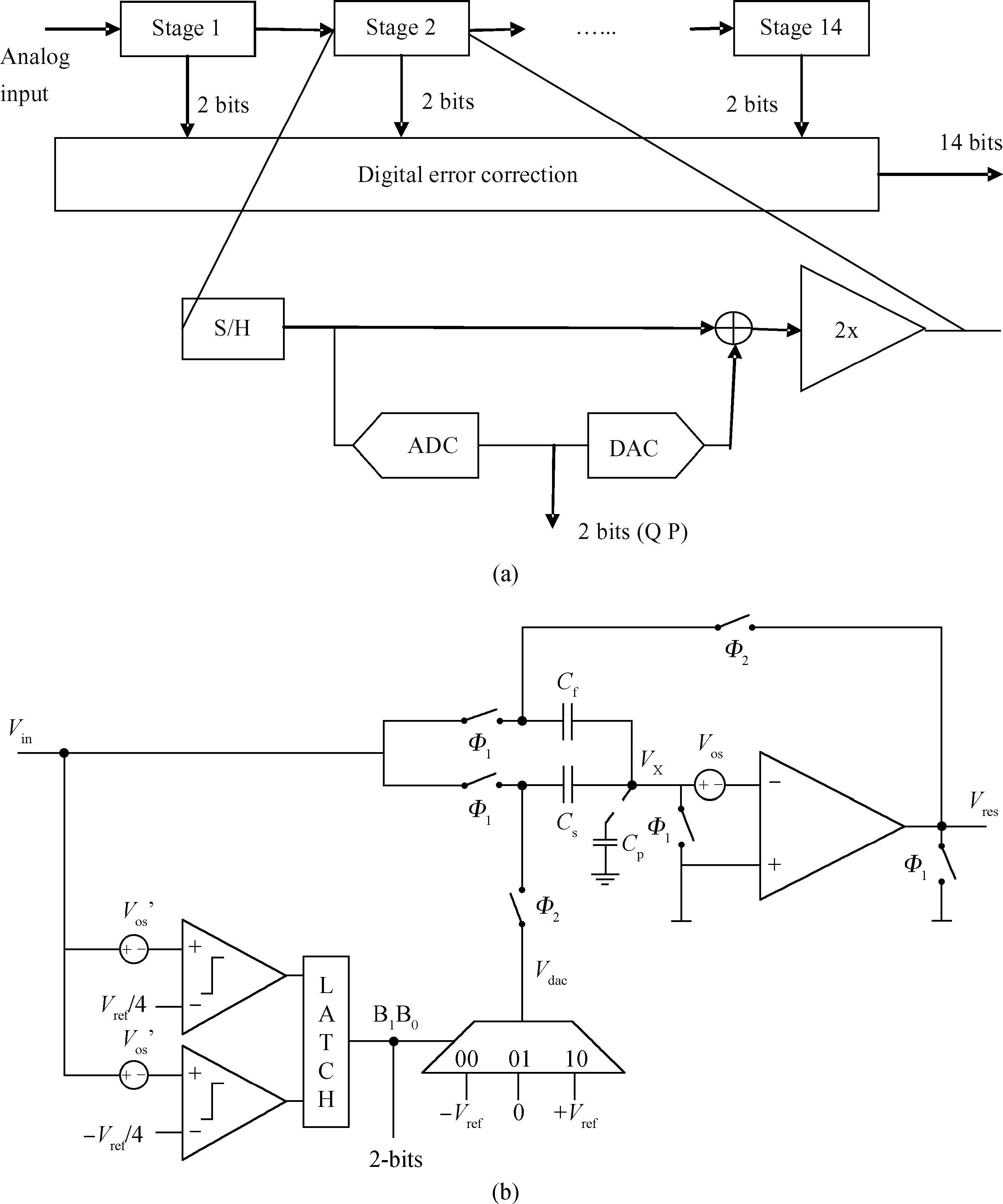

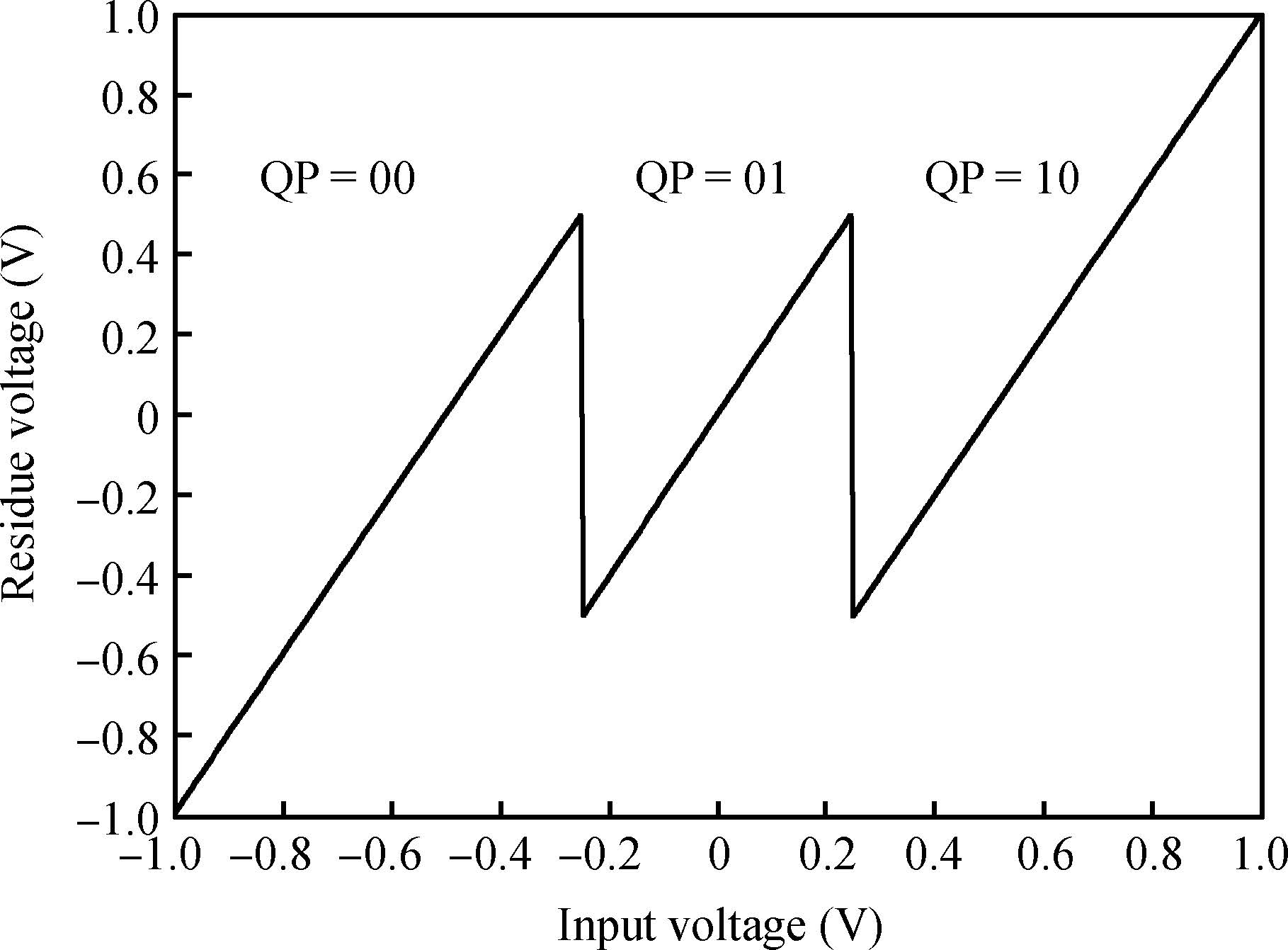

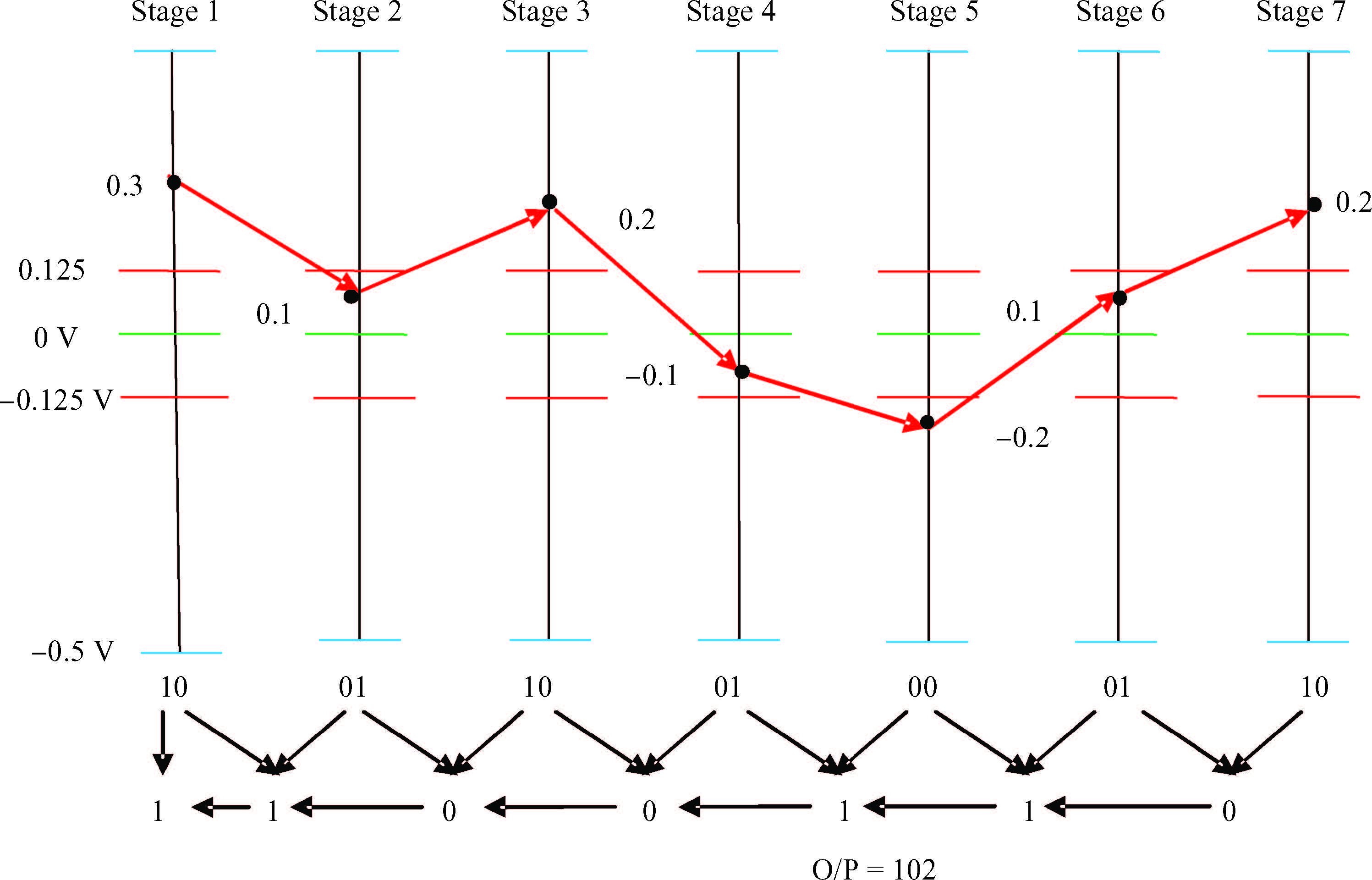

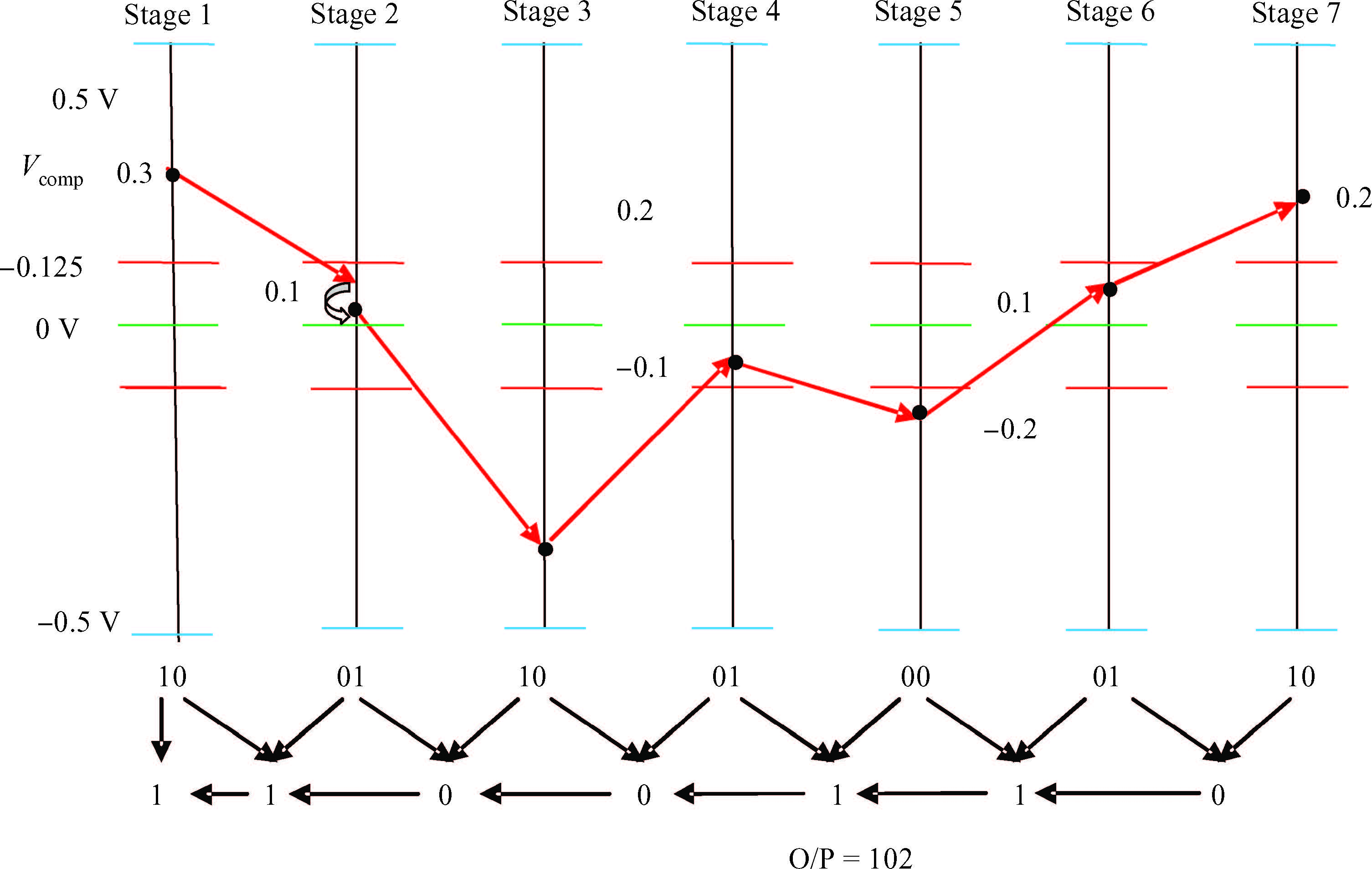

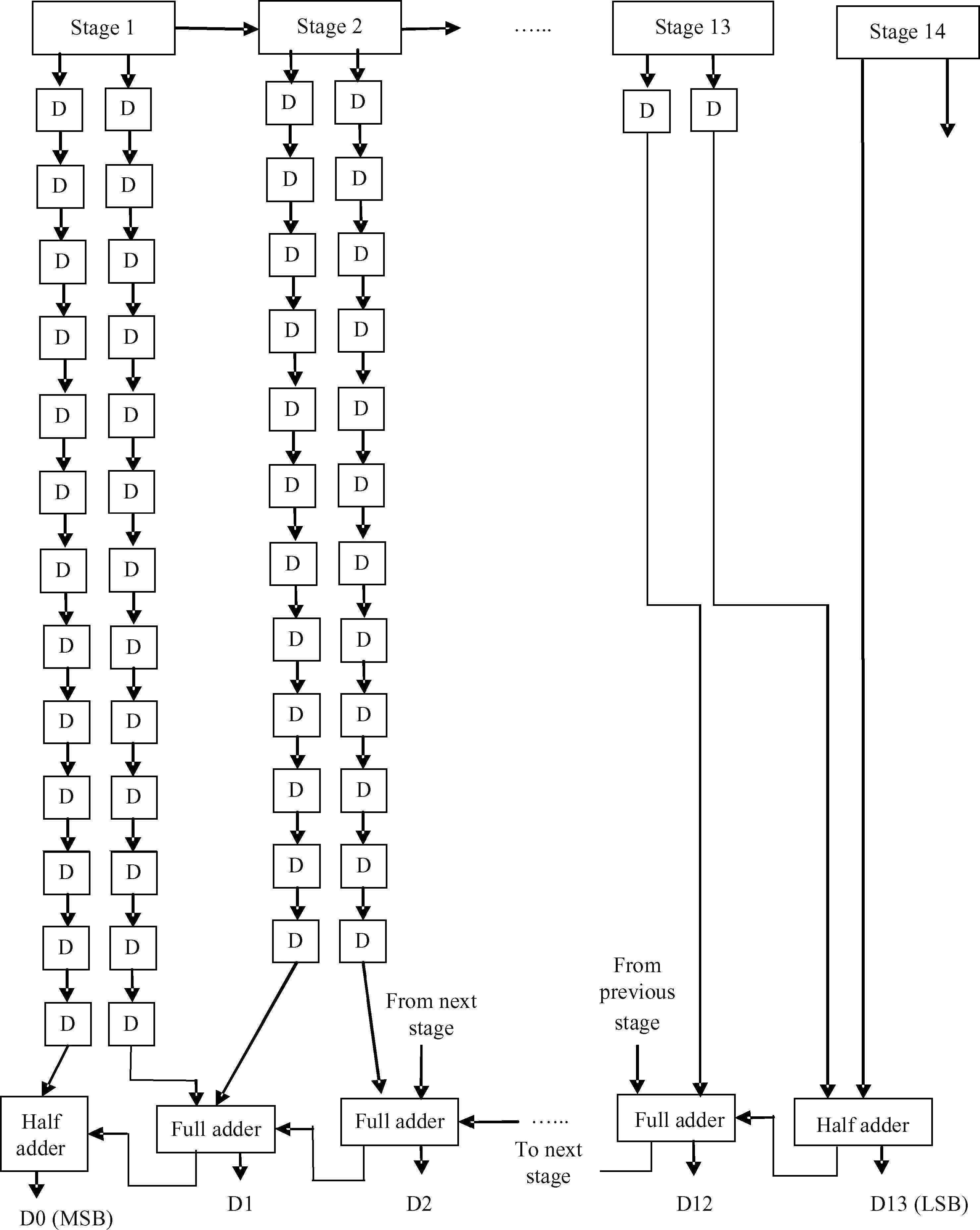

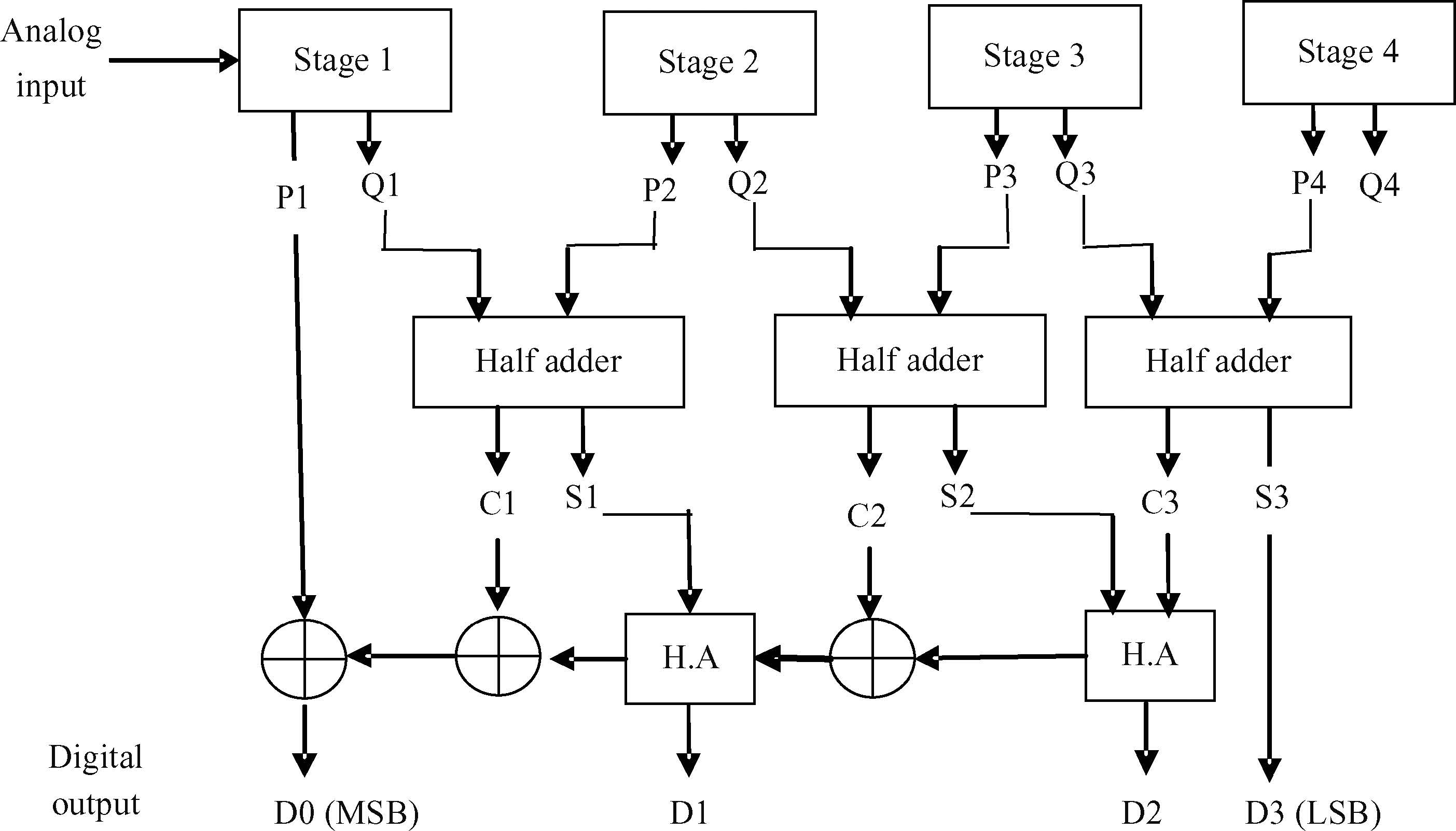

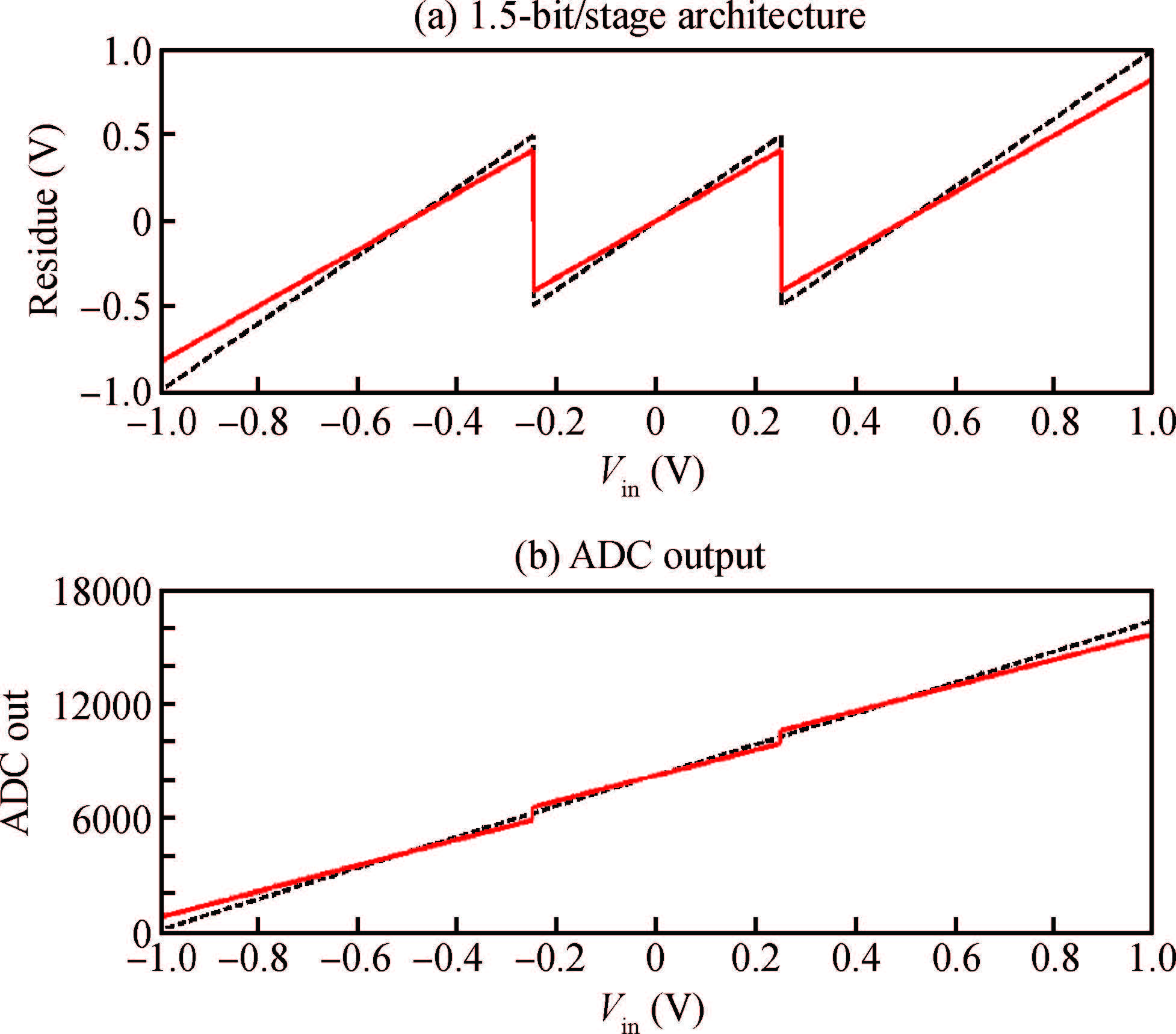

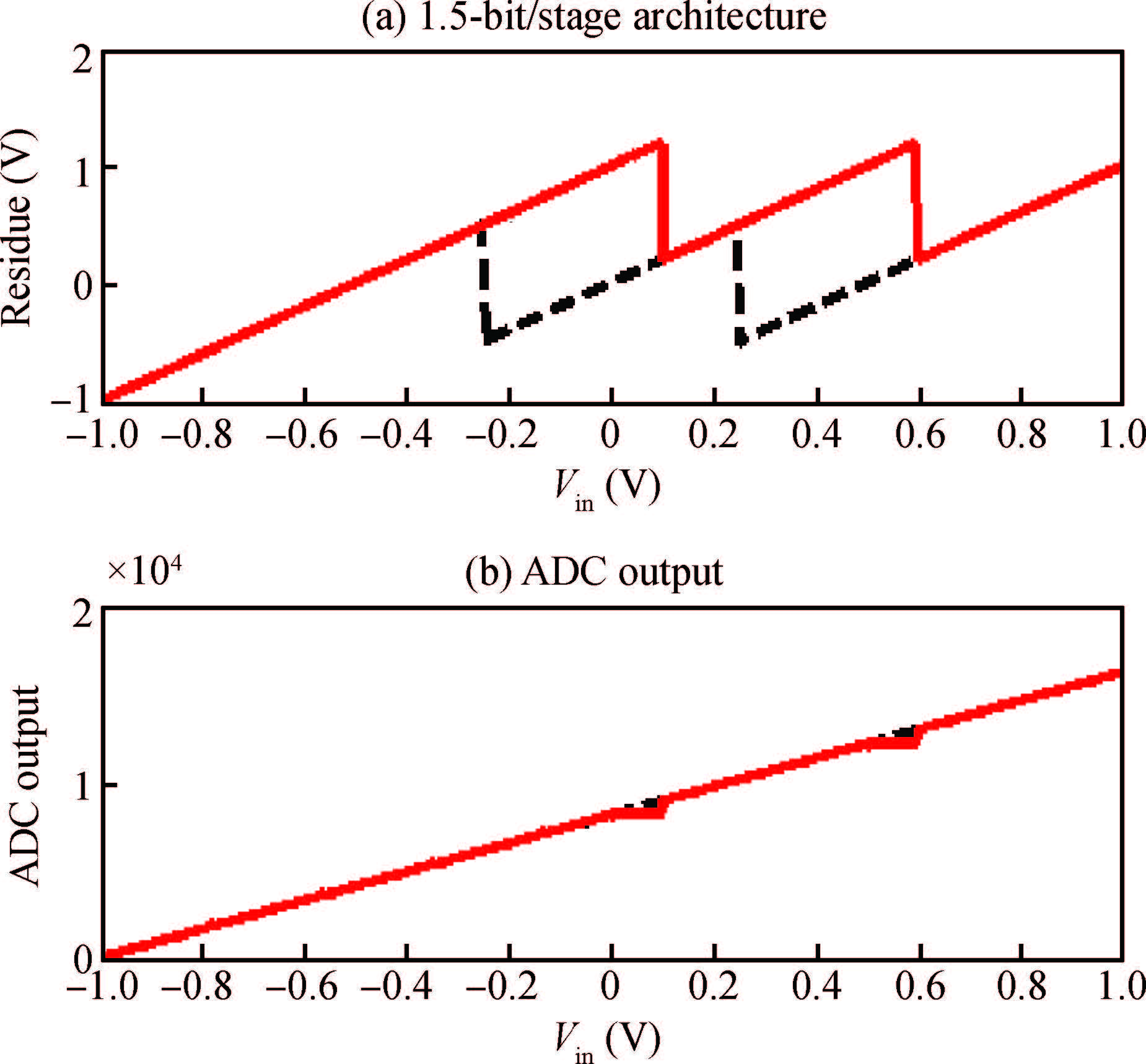

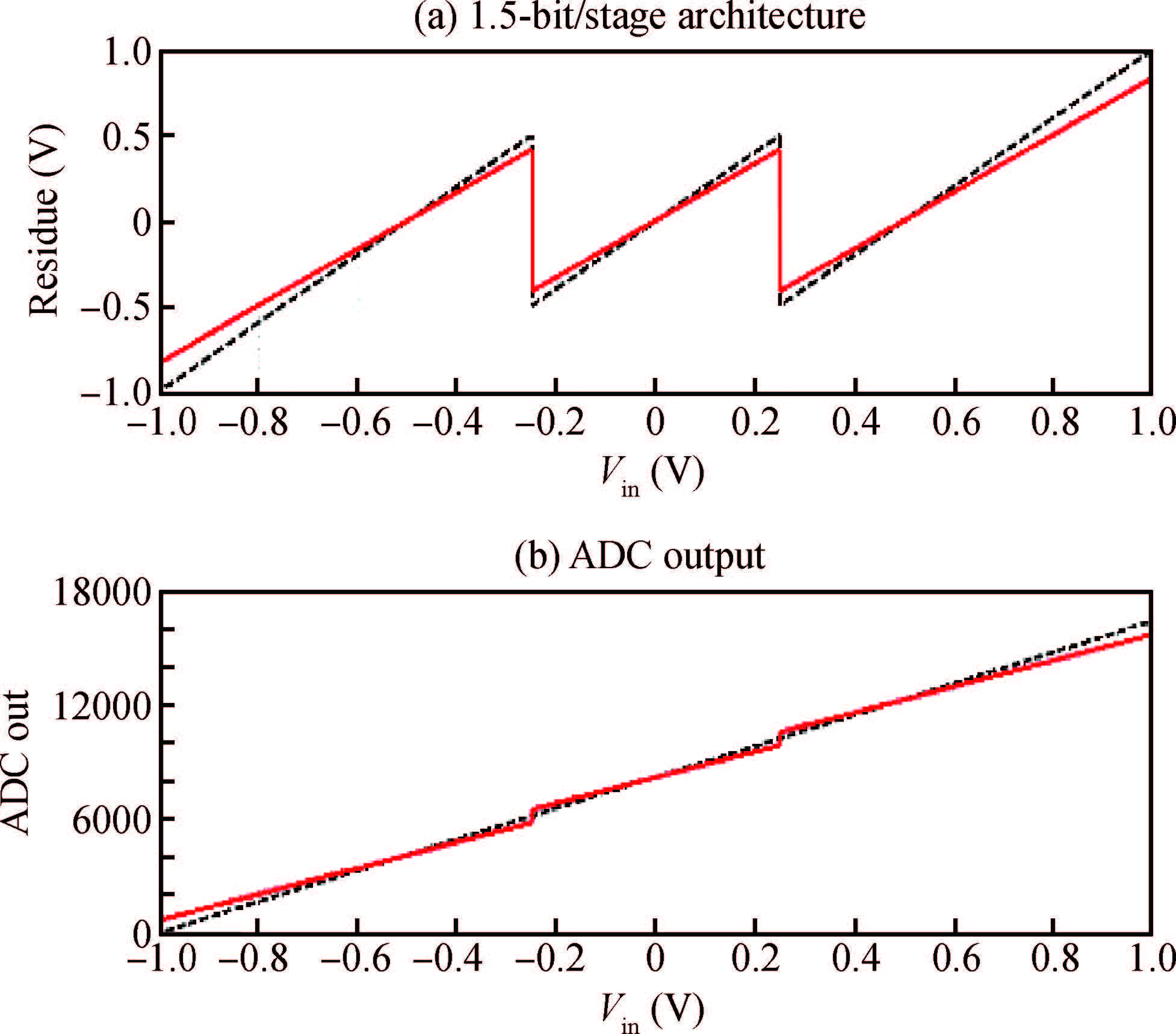

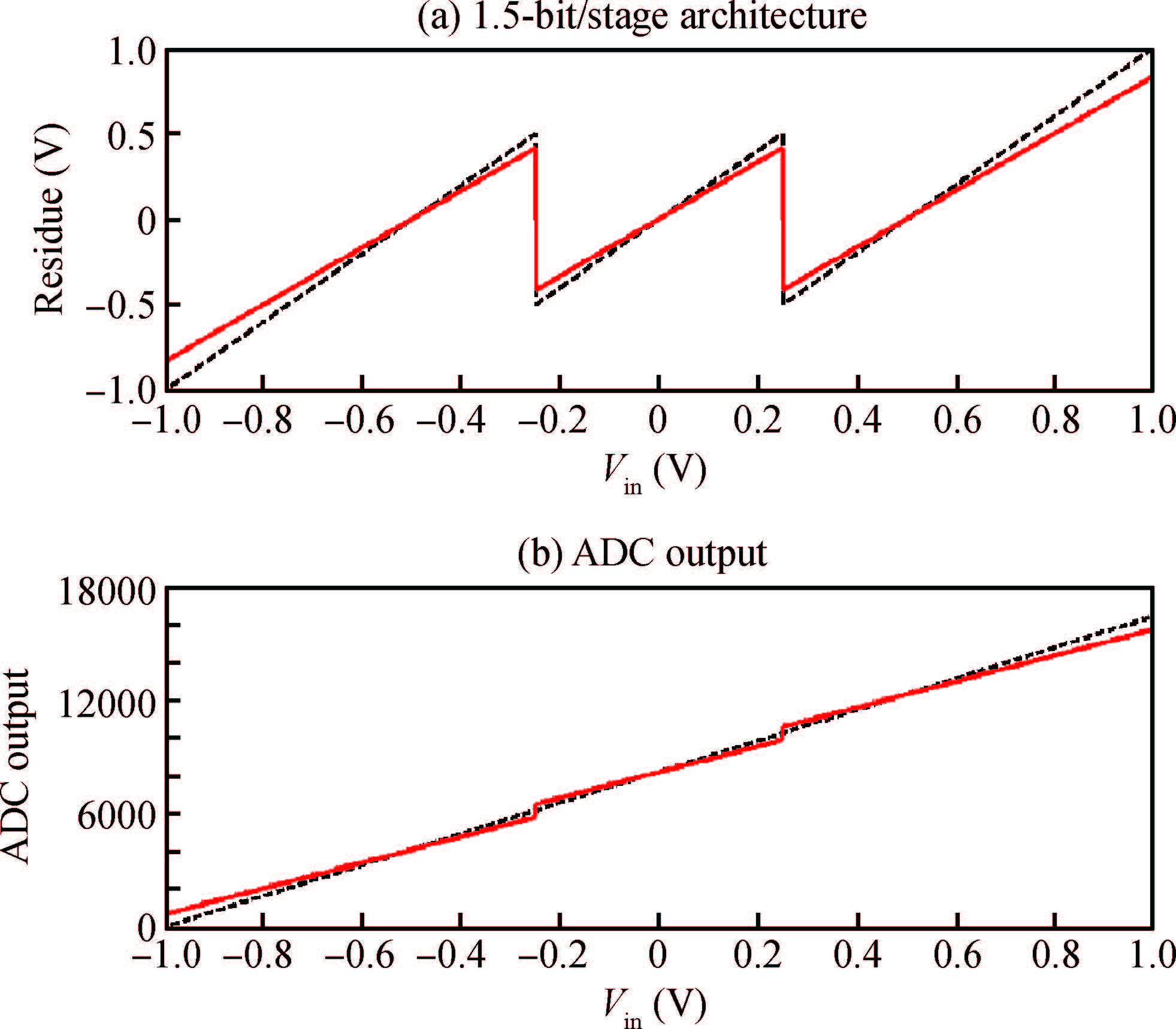

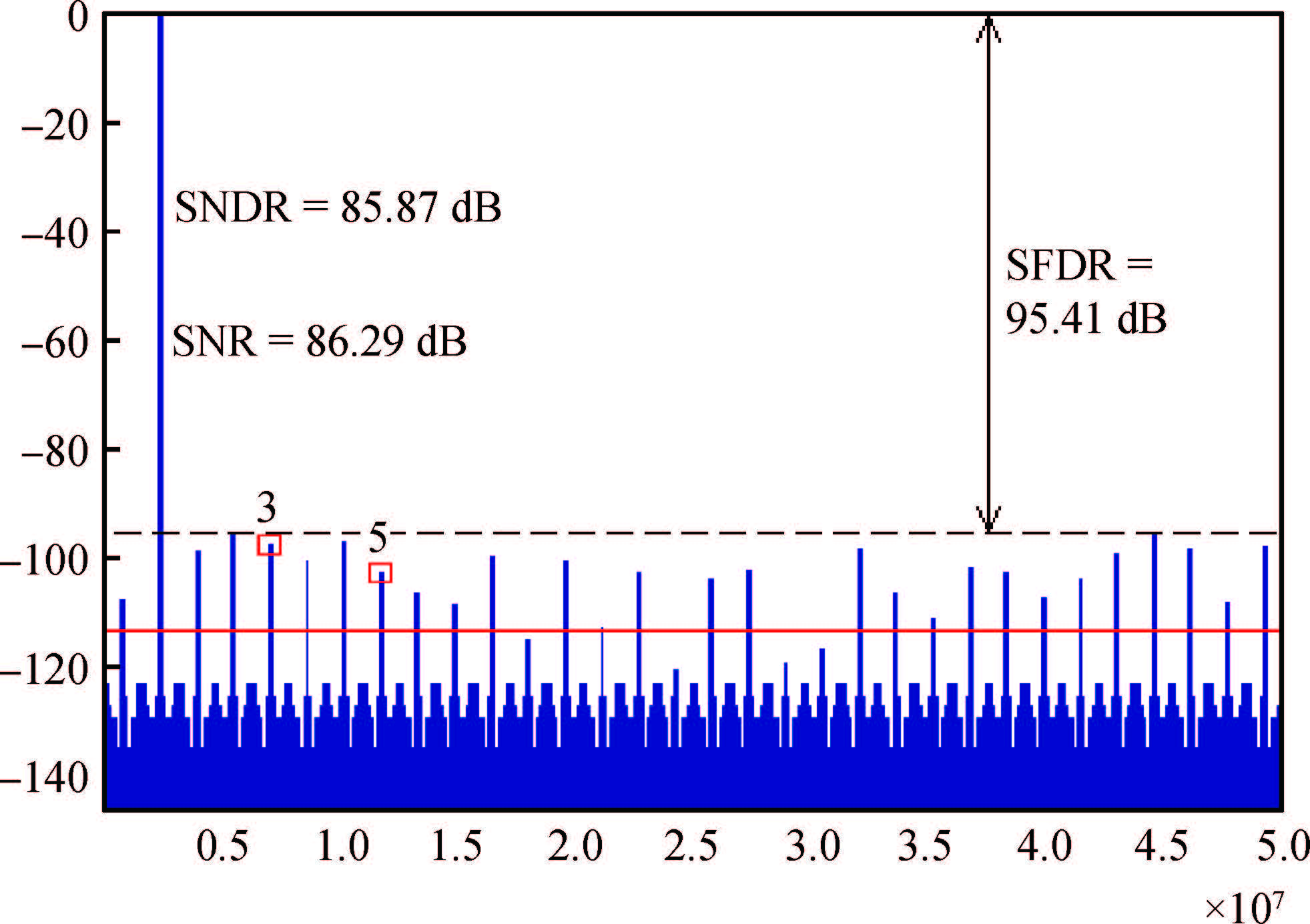

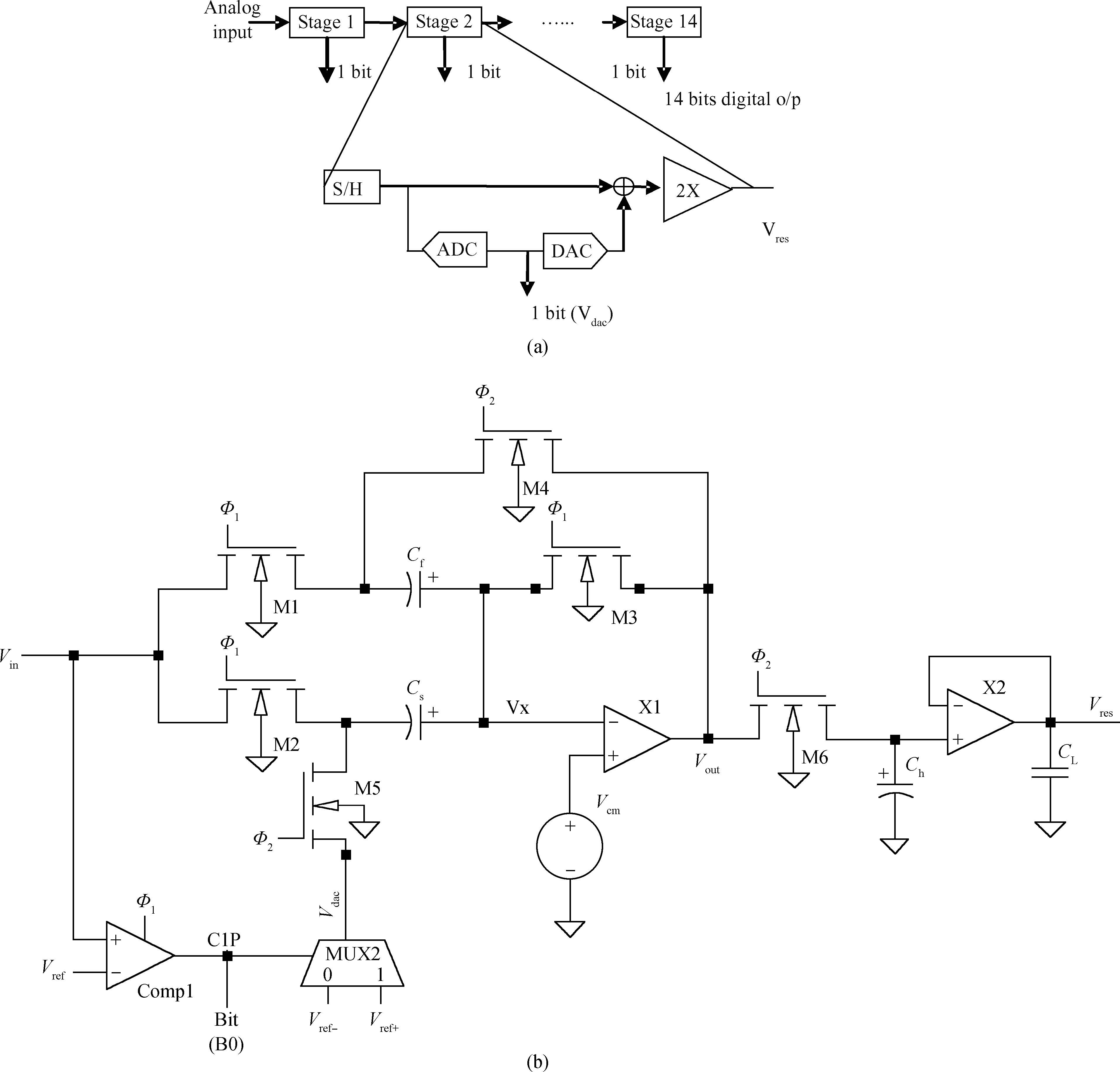

A novel architecture of a pipelined redundant-signed-digit analog to digital converter(RSD-ADC) is presented featuring a high signal to noise ratio(SNR), spurious free dynamic range(SFDR) and signal to noise plus distortion(SNDR) with efficient background correction logic. The proposed ADC architecture shows high accuracy with a high speed circuit and efficient utilization of the hardware. This paper demonstrates the functionality of the digital correction logic of 14-bit pipelined ADC at each 1.5 bit/stage. This prototype of ADC architecture accounts for capacitor mismatch, comparator offset and finite Op-Amp gain error in the MDAC(residue amplification circuit) stages. With the proposed architecture of ADC, SNDR obtained is 85.89 dB, SNR is 85.9 dB and SFDR obtained is 102.8 dB at the sample rate of 100 MHz. This novel architecture of digital correction logic is transparent to the overall system, which is demonstrated by using 14-bit pipelined ADC. After a latency of 14 clocks, digital output will be available at every clock pulse. To describe the circuit behavior of the ADC, VHDL and MATLAB programs are used. The proposed architecture is also capable of reducing the digital hardware. Silicon area is also the complexity of the design. -

References

[1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] [22] [23] [24] [25] -

Proportional views

DownLoad:

DownLoad: