| Citation: |

Weiyi Li, Zhili Zhang, Kai Fu, Guohao Yu, Xiaodong Zhang, Shichuang Sun, Liang Song, Ronghui Hao, Yaming Fan, Yong Cai, Baoshun Zhang. Design and simulation of a novel E-mode GaN MIS-HEMT based on a cascode connection for suppression of electric field under gate and improvement of reliability[J]. Journal of Semiconductors, 2017, 38(7): 074001. doi: 10.1088/1674-4926/38/7/074001

****

W Y Li, Z L Zhang, K Fu, G H Yu, X D Zhang, S C Sun, L Song, R H Hao, Y M Fan, Y Cai, B S Zhang. Design and simulation of a novel E-mode GaN MIS-HEMT based on a cascode connection for suppression of electric field under gate and improvement of reliability[J]. J. Semicond., 2017, 38(7): 074001. doi: 10.1088/1674-4926/38/7/074001.

|

Design and simulation of a novel E-mode GaN MIS-HEMT based on a cascode connection for suppression of electric field under gate and improvement of reliability

DOI: 10.1088/1674-4926/38/7/074001

More Information

-

Abstract

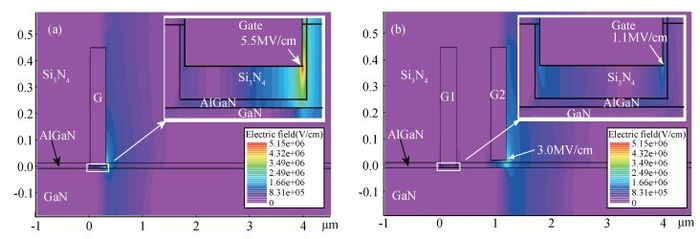

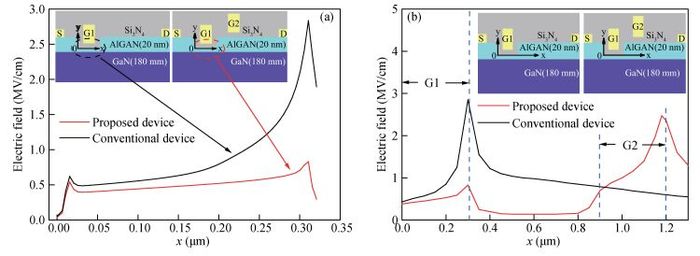

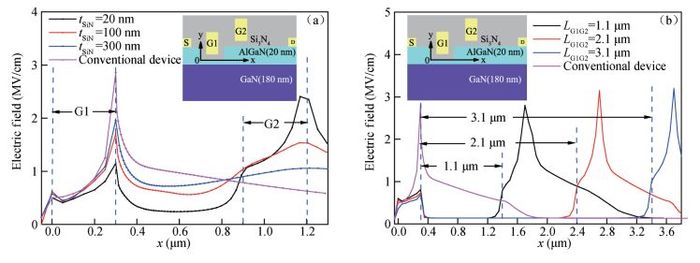

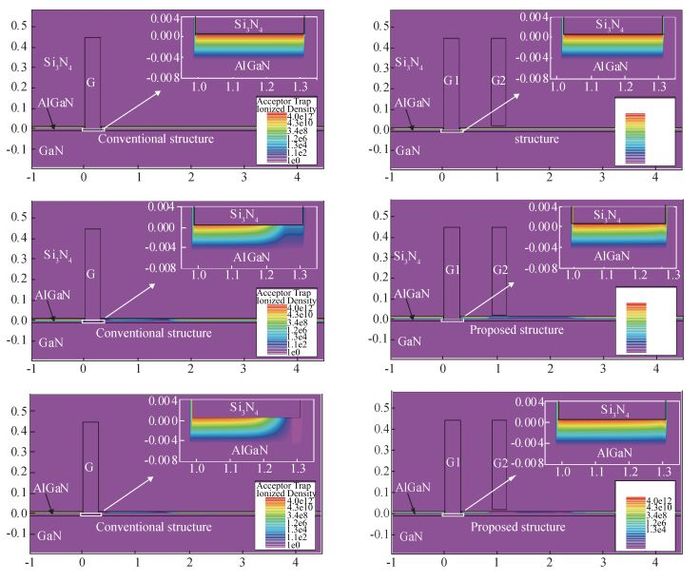

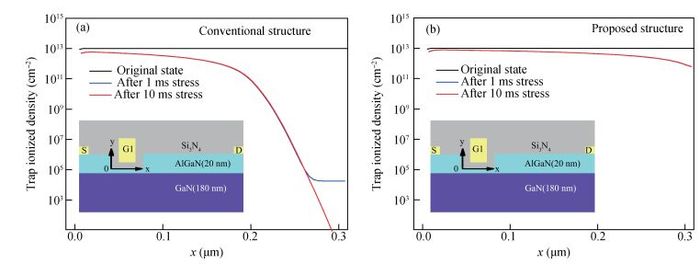

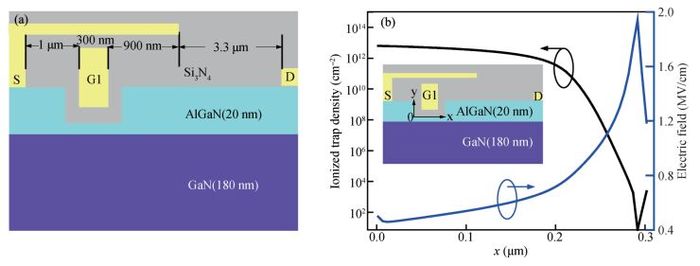

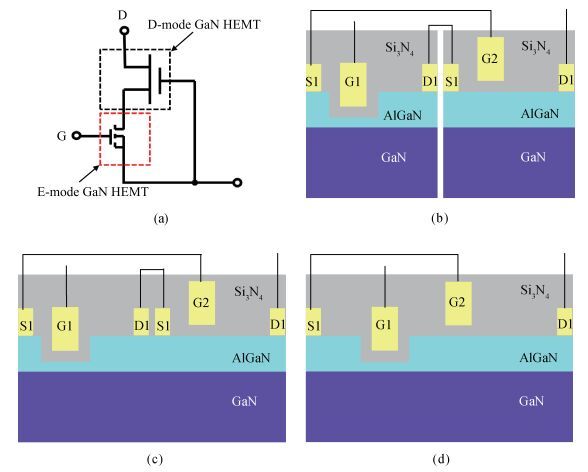

We proposed a novel AlGaN/GaN enhancement-mode (E-mode) high electron mobility transistor (HEMT) with a dual-gate structure and carried out the detailed numerical simulation of device operation using Silvaco Atlas. The dual-gate device is based on a cascode connection of an E-mode and a D-mode gate. The simulation results show that electric field under the gate is decreased by more than 70% compared to that of the conventional E-mode MIS-HEMTs (from 2.83 MV/cm decreased to 0.83 MV/cm). Thus, with the discussion of ionized trap density, the proposed dual-gate structure can highly improve electric field-related reliability, such as, threshold voltage stability. In addition, compared with HEMT with field plate structure, the proposed structure exhibits a simplified fabrication process and a more effective suppression of high electric field. -

References

[1] Karmalkar S, Mishra U K. Enhancement of breakdown voltage in AlGaN/GaN high electron mobility transistors using a field plate. IEEE Trans Electron Devices, 2001, 48: 1515 doi: 10.1109/16.936500[2] Dong Z, Hao R, Zhang Z, et al. Impact of N-plasma treatment on the current collapse of ALGAN/GAN HEMTs. 12th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT), 2014: 1 http://ieeexplore.ieee.org/abstract/document/7021380[3] Wang Z, Zhou J, Kong Y, et al. Thin-barrier enhancement-mode AlGaN/GaN MIS-HEMT using ALD Al2O3 as gate insulator. J Semicond, 2015, 36: 094004 doi: 10.1088/1674-4926/36/9/094004[4] Saito W, Takada Y, Kuraguchi M, et al. Recessed-gate structure approach toward normally off high-voltage AlGaN/GaN HEMT for power electronics applications. IEEE Trans Electron Devices, 2006, 53: 356 doi: 10.1109/TED.2005.862708[5] Xu Z, Wang J, Cai Y, et al. Enhancement mode (E-mode) AlGaN/GaN MOSFET with A/mm leakage current and ON/OFF current ratio. IEEE Electron Device Lett, 2014, 35: 1200 doi: 10.1109/LED.2014.2360541[6] Wang Y, Wang M, Xie B, et al. High-performance normally-off MOSFET using a wet etching-based gate recess technique. IEEE Electron Device Lett, 2013, 34: 1370 doi: 10.1109/LED.2013.2279844[7] Cai Y, Zhou Y, Lau K M, et al. Control of threshold voltage of AlGaN/GaN HEMTs by fluoride-based plasma treatment: from depletion mode to enhancement mode. IEEE Trans Electron Devices, 2006, 53: 2207 doi: 10.1109/TED.2006.881054[8] Zhang Z, Fu K, Deng X, et al. Normally off AlGaN/GaN MIS-high-electron mobility transistors fabricated by using low pressure chemical vapor deposition Si3N4 gate dielectric and standard fluorine ion implantation. IEEE Electron Device Lett, 2015, 36: 1128 doi: 10.1109/LED.2015.2483760[9] Chen Y, Zheng X, Zhang J, et al. Monolithically integrated enhancement/depletion-mode AlGaN/GaN HEMTs SRAM unit and voltage level shifter using fluorine plasma treatment. J Semicond, 2016, 37: 055002 doi: 10.1088/1674-4926/37/5/055002[10] Uemoto Y, Hikita M, Ueno V, et al. Gate injection transistor (GIT)-a normally-off AlGaN/GaN power transistor using conductivity modulation. IEEE Trans Electron Devices, 2007, 54: 3393 doi: 10.1109/TED.2007.908601[11] Meneghesso G, Meneghini M, Zanoni E. Reliability and instabilities in GaN-based HEMTs. IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC), 2014: 1 http://ieeexplore.ieee.org/document/7061275/[12] Yi C, Wang R, Huang W, et al. Reliability of enhancement-mode AlGaN/GaN HEMTs fabricated by fluorine plasma treatment. 2007 IEEE International Electron Devices Meeting, 2007: 389 http://ieeexplore.ieee.org/document/4418954/?reload=true&arnumber=4418954&sortType%3Dasc_p_Sequence%26filter%3DAND%28p_IS_Number%3A4418848%29%26pageNumber%3D2%26rowsPerPage%3D100[13] Shockley W, Read W Jr. Statistics of the recombinations of holes and electrons. Phys Rev, 1952, 87: 835 doi: 10.1103/PhysRev.87.835[14] Hall R N. Electron--hole recombination in germanium. Phys Rev, 1952, 87: 387 doi: 10.1103/PhysRev.87.387[15] Caughey D M, Thomas R E. Carrier mobilities in silicon empirically related to doping and field. Proc IEEE, 1967, 55: 2192 doi: 10.1109/PROC.1967.6123[16] Piprek J. Semiconductor optoelectronic devices: introduction to physics and simulation. Academic Press, 2013[17] Ambacher O, Foutz B, Smart J, et al. Two dimensional electron gases induced by spontaneous and piezoelectric polarization in undoped and doped AlGaN/GaN heterostructures. J Appl Phys, 2000, 87: 334 doi: 10.1063/1.371866[18] Simmons J, Taylor G. Nonequilibrium steady-state statistics and associated effects for insulators and semiconductors containing an arbitrary distribution of traps. Phys Rev B, 1971, 4: 502 doi: 10.1103/PhysRevB.4.502[19] Wu T L, Marcon D, Bakeroot B, et al. Correlation of interface states/border traps and threshold voltage shift on AlGaN/GaN metal-insulator-semiconductor high-electron-mobility transistors. Appl Phys Lett, 2015, 107: 4 https://biblio.ugent.be/publication/6972789/file/6972802.pdf[20] Zhang Z, Yu G, Zhang X, et al. Studies on high-voltage GaN-on-Si MIS-HEMTs using LPCVD Si3N4 as gate dielectric and passivation layer. IEEE Trans Electron Devices, 2016, 63: 731 doi: 10.1109/TED.2015.2510445[21] Meneghini M, Rossetto I, Bisi D, et al. Negative bias-induced threshold voltage instability in GaN-on-Si power HEMTs. IEEE Electron Device Lett, 2016, 37: 474 doi: 10.1109/LED.2016.2530693[22] Saito W, Kuraguchi M, Takada Y, et al. Design optimization of high breakdown voltage AlGaN-GaN power HEMT on an insulating substrate for RONAVB tradeoff characteristics. IEEE Trans Electron Devices, 2005, 52: 106 doi: 10.1109/TED.2004.841338 -

Proportional views

DownLoad:

DownLoad: