| Citation: |

Yuejun Zhang, Pengjun Wang, Gang Li. An isolated SNM model for high-stability multi-port register file in 65 nm CMOS[J]. Journal of Semiconductors, 2017, 38(9): 095002. doi: 10.1088/1674-4926/38/9/095002

****

Y J Zhang, P J Wang, G Li. An isolated SNM model for high-stability multi-port register file in 65 nm CMOS[J]. J. Semicond., 2017, 38(9): 095002. doi: 10.1088/1674-4926/38/9/095002.

|

An isolated SNM model for high-stability multi-port register file in 65 nm CMOS

DOI: 10.1088/1674-4926/38/9/095002

More Information

-

Abstract

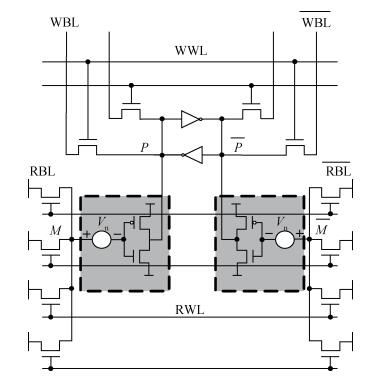

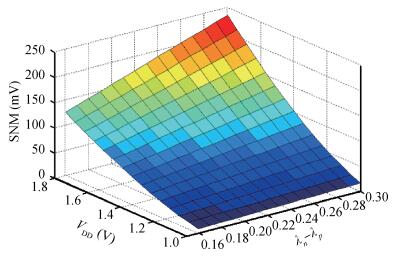

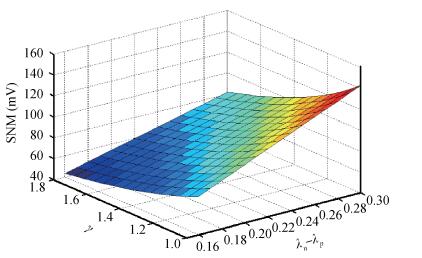

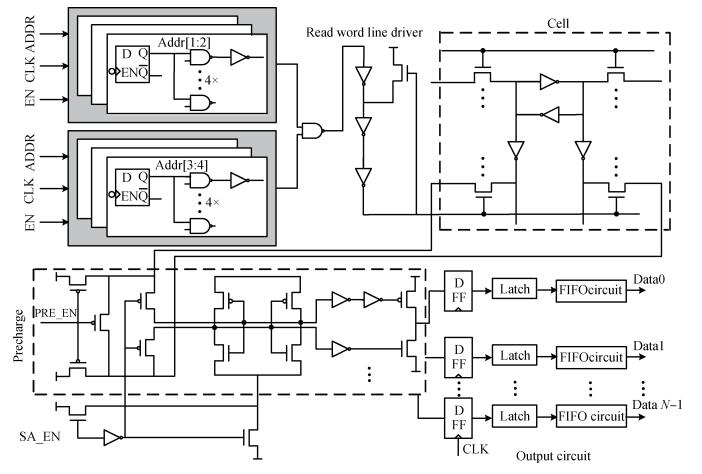

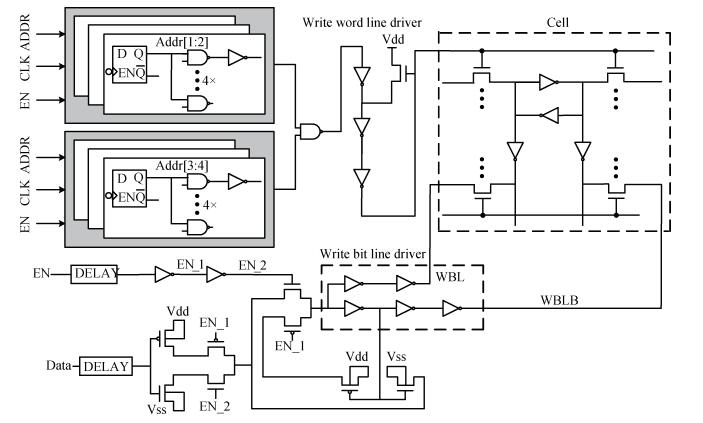

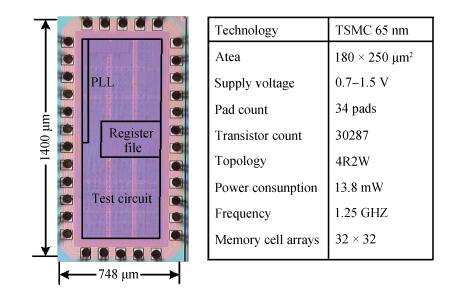

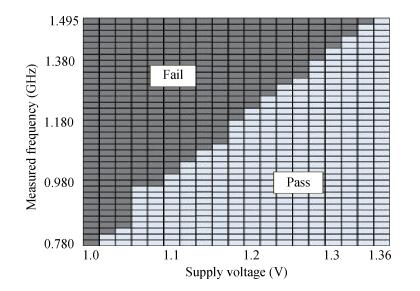

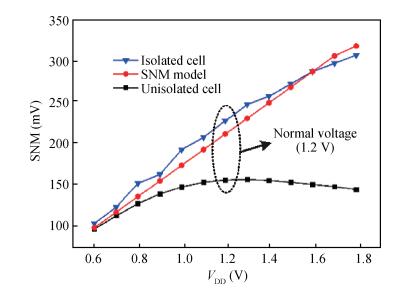

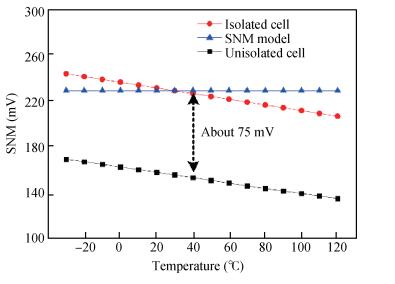

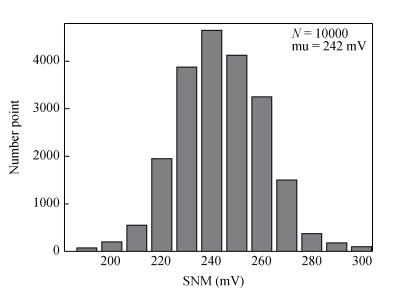

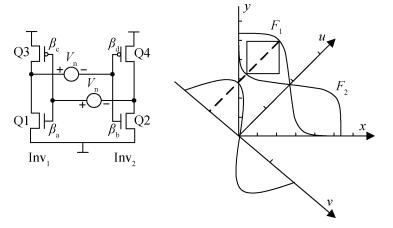

In modern microprocessors, the multi-port register file is one of the key modules which provides fast and multiple data access for instructions. As the number of access ports in register files increases, stability becomes a key issue due to the voltage fluctuation on bit lines. We propose to apply an isolated inverter to address the voltage fluctuation. To assess the register stability, we derive a closed-form expression of static noise margin (SNM) for our register file. The proposed SNM model can be used as a guideline to predict the impact of several register parameters on the stability and optimize register file designs. To validate the proposed SNM model, we fabricated a test chip of two-write-four-read (2W4R) 1024 bits register file in a TSMC 65 nm low-power CMOS technology. The experimental result shows that the stability of our register file cells with an isolated inverter improve the conventional cells by approximately 2.4 times. Also, the supply voltage causes a fluctuation of SNM of about 65%, while temperature and transistor mismatch cause a fluctuation of SNM of about 20%. -

References

[1] St B, Wendel D, Kalla R, et al. POWER7TM, a highly parallel, scalable multi-core high end server processor. IEEE J Solid-State Circuits, 2011, 46(1):145 doi: 10.1109/JSSC.2010.2080611[2] Stolt B, Mittlefehldt Y, Dubey S. Design and implementation of the POWER6 microprocessor. IEEE J Solid-State Circuits, 2008, 43(1):21 doi: 10.1109/JSSC.2007.910963[3] Thimbleby H. Modes, wysiwyg and the von neumann bottleneck. 1988 IEE Colloquium on Formal Methods and Human-Computer Interaction Ⅱ, 1988:4 http://ieeexplore.ieee.org/document/209312/[4] Asgari B, Fazeli M, Patooghy A, et al. Micro-architectural approach to the efficient employment of STTRAM cells in a microprocessor register file. IET Comput Dig Tech, 2017, 11(1):1 doi: 10.1049/iet-cdt.2015.0155[5] Gong N, Wang J, Jiang S, et al. TM-RF:aging-aware powerefficient register file design for modern microprocessors. IEEE Trans Very Large Scale Integr (VLSI) Syst, 2015, 23(7):1196 doi: 10.1109/TVLSI.2014.2334136[6] Hsieh H, Dhong S H, Lin C C, et al. Custom 6-R, 2-or 4-W multi-port register files in an ASIC SOC with a DVFS window of 0. 5 V, 130 MHz to 0. 96 V, 3. 2 GHz in a 28-nm HKMG CMOS technology. 2015 IEEE Custom Integrated Circuits Conference (CICC), 2015: 1[7] Ditlow G, Montoye R, Storino S. A 4R2W register file for a 2. 3GHz wire-speed POWERTM processor with double-pumped write operation. 2011 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2011: 256[8] Sarfraz K, Chan M. A 1.2 V-to-0.4 V 3.2 GHz-to-14.3 MHz power-efficient 3-port register file in 65-nm CMOS. IEEE Trans Circuits Syst I, 2017, 64(2):360 doi: 10.1109/TCSI.2016.2613282[9] Yang T, Kinget P, Seok M. Register file circuits and postdeployment framework to monitor aging effects in field. 42nd European Solid-State Circuits Conference (ESSCIRC), 2016:425 http://www.ee.columbia.edu/~mgseok/[10] Yang T, Kim D, Kinget P, et al. 14. 7 in-situ techniques for infield sensing of NBTI degradation in an SRAM register file. 2015 IEEE International Solid-State Circuits Conference-(ISSCC) Digest of Technical Papers, 2015: 1[11] Burda G, Kolla Y, Dieffenderfer J, et al. A 45 nm CMOS 13-port 64-word 41b fully associative content-addressable register file. 2010 IEEE International Solid-State Circuits Conference-(ISSCC) Digest of Technical Papers, 2010:286 http://ieeexplore.ieee.org/xpl/tocresult.jsp?sortType%3Dasc_p_Sequence%26filter%3DAND%28p_IS_Number%3A5433812%29%26rowsPerPage%3D100&pageNumber=2[12] Lei W, Patel N. Improving error tolerance for multithreaded register files. IEEE Trans Very Large Scale Integr (VLSI) Syst, 2008, 16(8):1009 doi: 10.1109/TVLSI.2008.2000521[13] Jongeun L, Shrivastava A. Static analysis of register file vulnerability. IEEE Tran Comput-Aided Des Integr Circuits Syst, 2011, 30(4):607 doi: 10.1109/TCAD.2010.2095630[14] Sharifkhani M, Sachdev M. SRAM cell stability:a dynamic perspective. IEEE J Solid-State Circuits, 2009, 44(2):609 doi: 10.1109/JSSC.2008.2010818[15] Jan M, Anantha C. Digital integrated circuits: a design perspective. 2nd ed. Beijing: Publishing House of Electronics Industry, 2007[16] Cai B J. Design optimization of static random access memory bit cell and test chip. MS Dissertation, Shanghai Jiao Tong University, 2007(in Chinese)[17] Balkan D, Sharkey J, Ponomarev D, et al. Selective writeback:reducing register file pressure and energy consumption. IEEE Trans Very Large Scale Integr (VLSI) Syst, 2008, 16(6):650 doi: 10.1109/TVLSI.2008.2000243[18] Konstadinidis G, Tremblay M, Chaudhry S. Architecture and physical implementation of a third generation 65 nm, 16 core, 32 thread chip-multithreading SPARC processor. IEEE J SolidState Circuits, 2009, 44(1):7 doi: 10.1109/JSSC.2008.2007144 -

Proportional views

DownLoad:

DownLoad: