| Citation: |

Hui Xu, Jianwei Zhu, Xiaoping Lu, Jingzhao Li. An advanced SEU tolerant latch based on error detection[J]. Journal of Semiconductors, 2018, 39(5): 055003. doi: 10.1088/1674-4926/39/5/055003

****

H Xu, J W Zhu, X P Lu, J Z Li. An advanced SEU tolerant latch based on error detection[J]. J. Semicond., 2018, 39(5): 055003. doi: 10.1088/1674-4926/39/5/055003.

|

An advanced SEU tolerant latch based on error detection

DOI: 10.1088/1674-4926/39/5/055003

More Information

-

Abstract

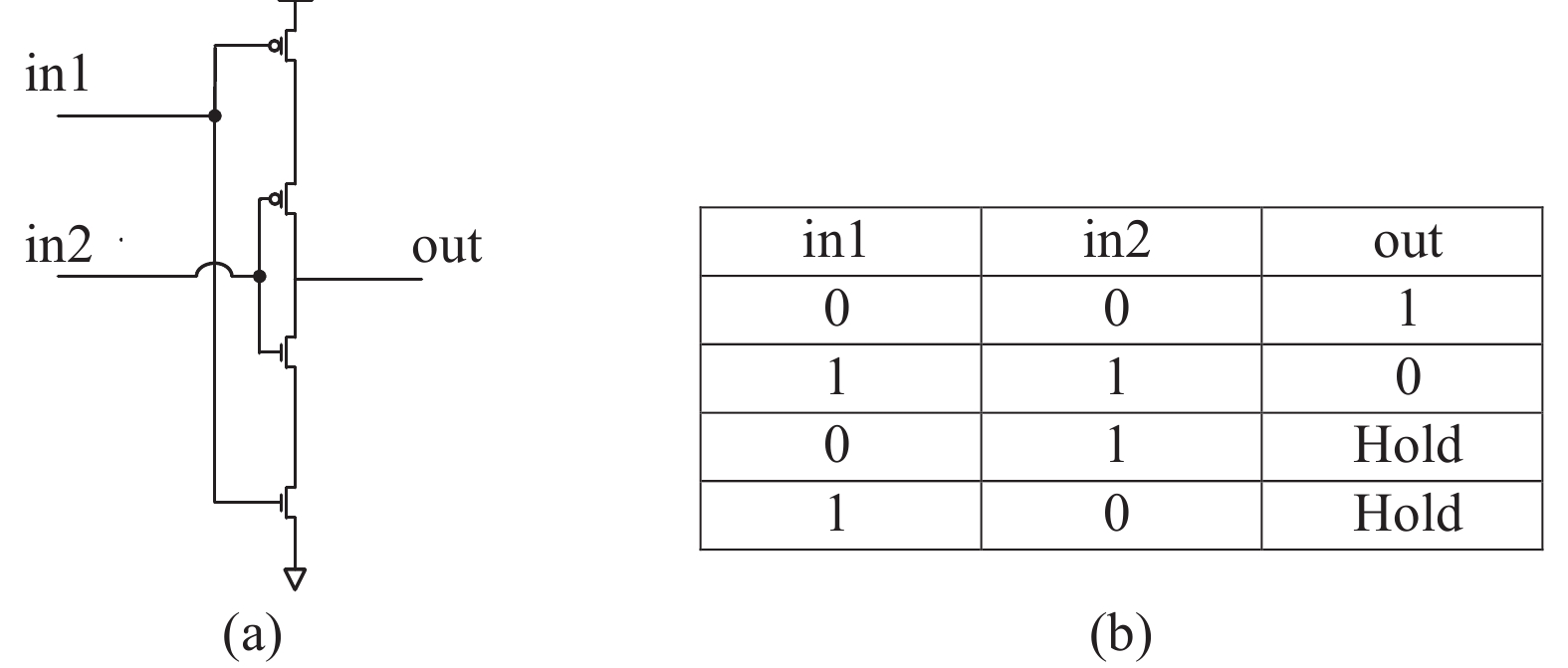

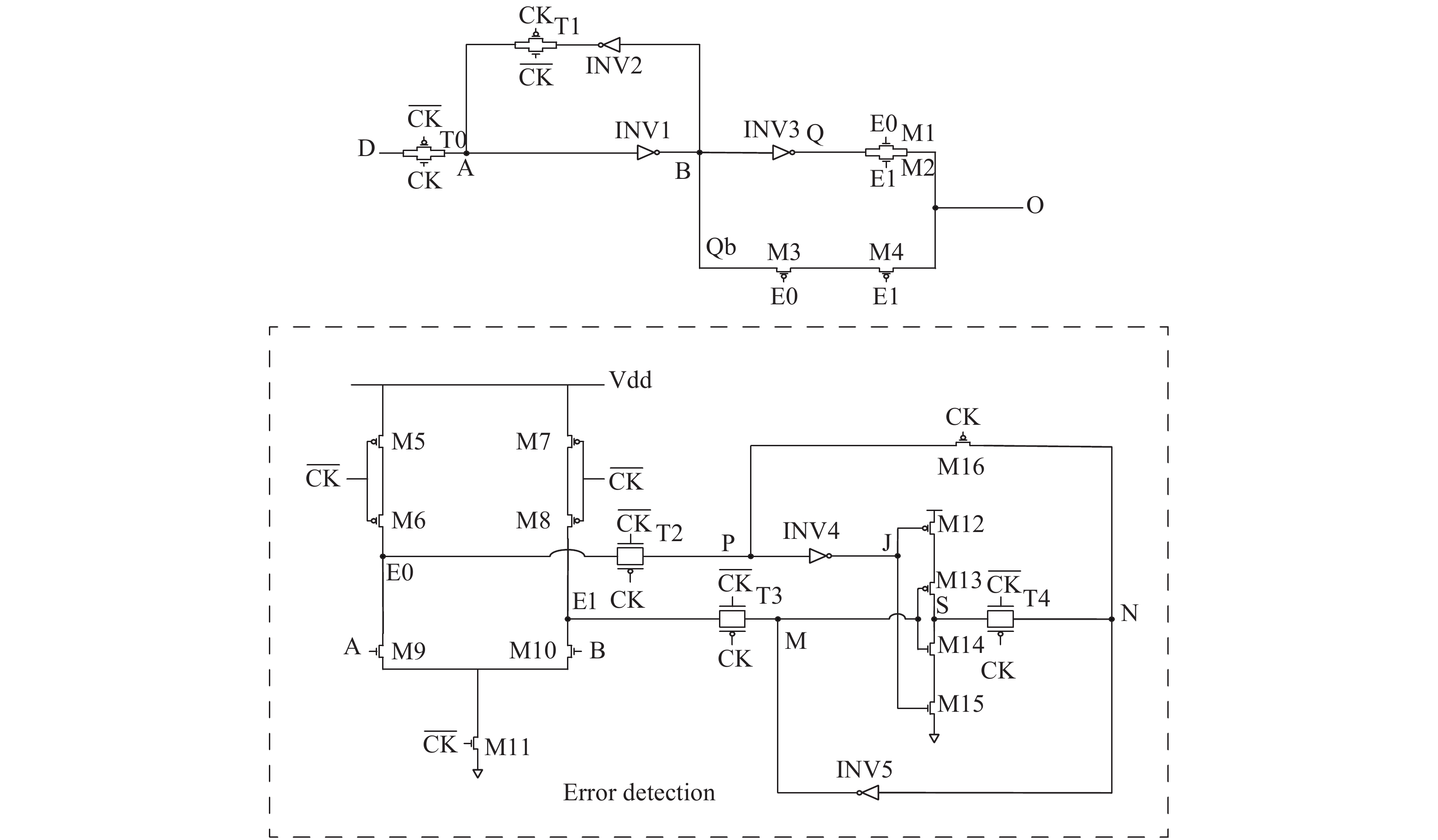

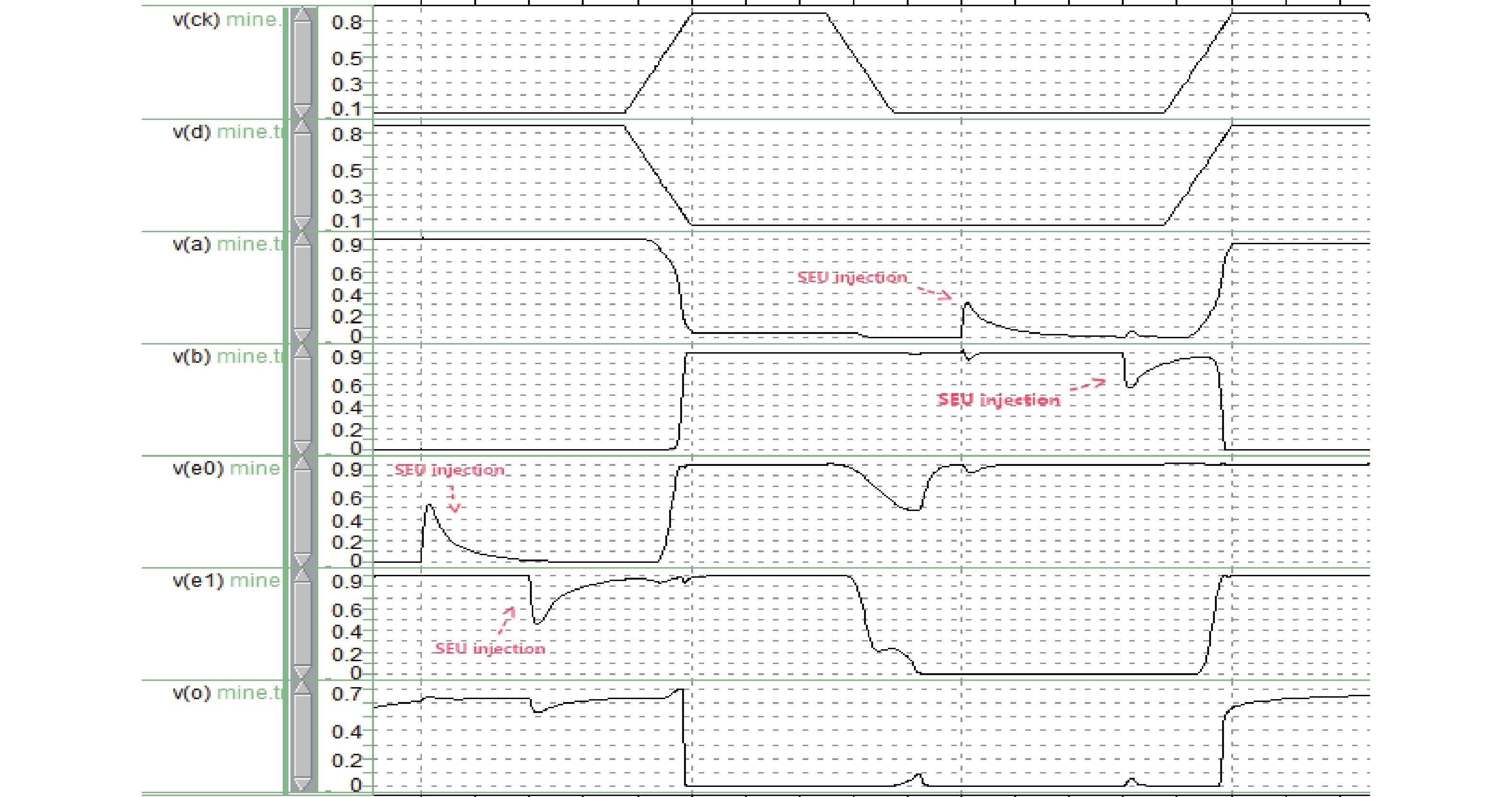

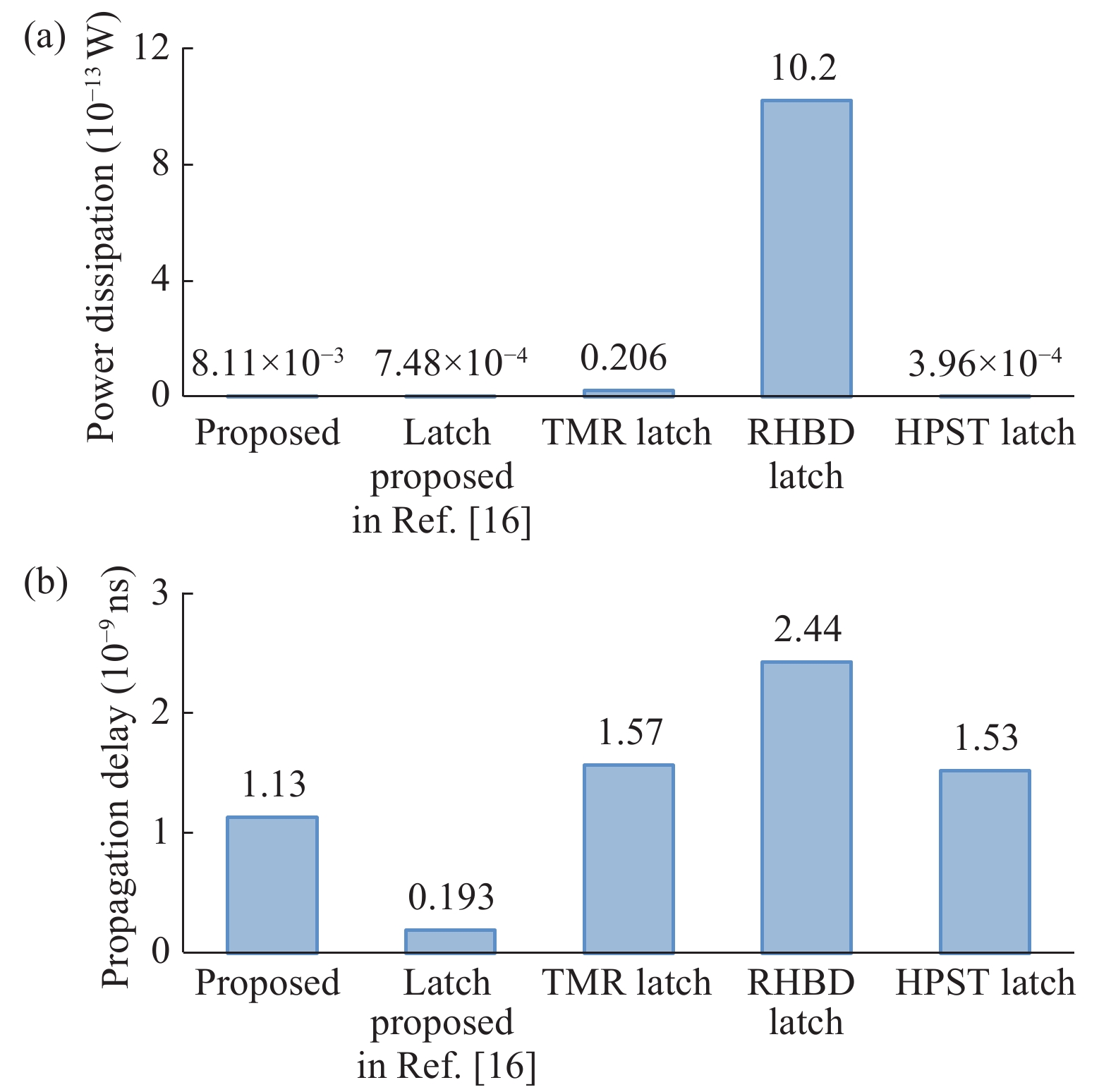

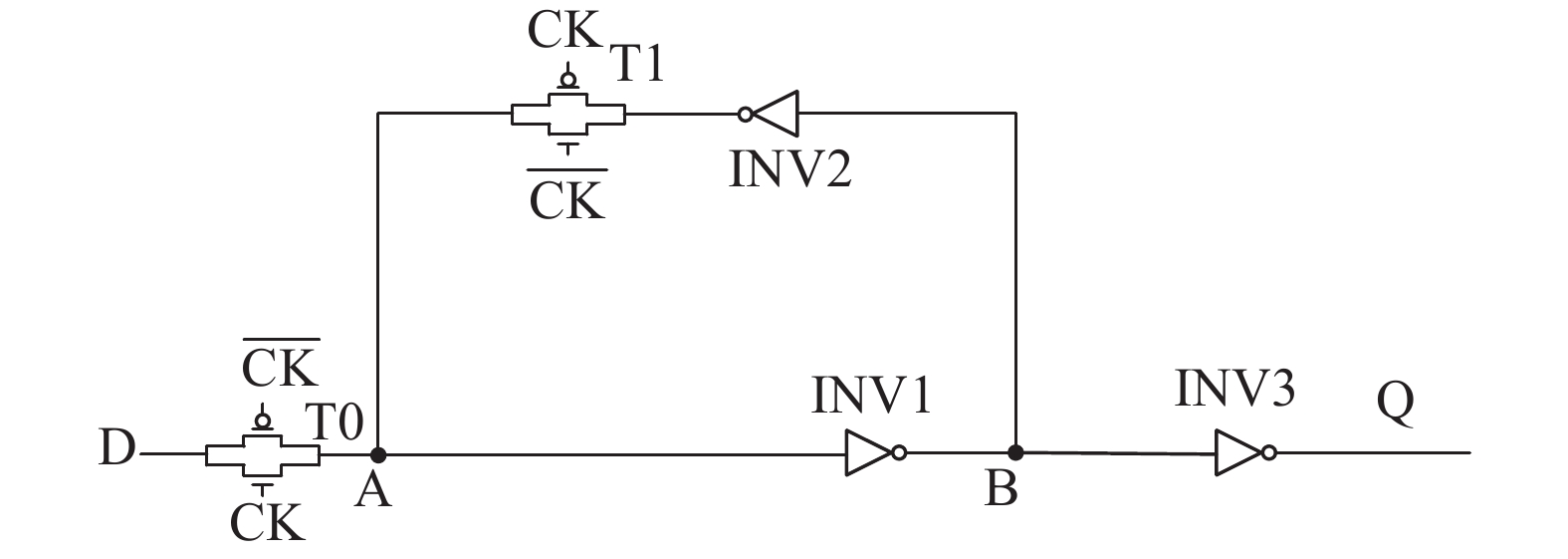

This paper proposes a latch that can mitigate SEUs via an error detection circuit. The error detection circuit is hardened by a C-element and a stacked PMOS. In the hold state, a particle strikes the latch or the error detection circuit may cause a fault logic state of the circuit. The error detection circuit can detect the upset node in the latch and the fault output will be corrected. The upset node in the error detection circuit can be corrected by the C-element. The power dissipation and propagation delay of the proposed latch are analyzed by HSPICE simulations. The proposed latch consumes about 77.5% less energy and 33.1% less propagation delay than the triple modular redundancy (TMR) latch. Simulation results demonstrate that the proposed latch can mitigate SEU effectively.-

Keywords:

- single event upset (SEU),

- latch,

- error detection,

- stacked

-

References

[1] Karnik T, Hazucha P. Characterization of soft errors caused by single event upsets in CMOS processes. IEEE Trans Depend Secure Comput, 2004, 1(2): 128 doi: 10.1109/TDSC.2004.14[2] Schrimpf R D, Warren K M, Weller R A, et al. Reliability and radiation effects in IC technologies. IEEE International Reliability Physics Symposium, 2008: 97[3] Ueno H, Namba K. Construction of a soft error (SEU) hardened latch with high critical charge. IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems, 2016: 27[4] The international technology roadmap for semiconductors. [Online]. Available: http://www.itrs.net/Links/2001ITRS/ Design.pdf[5] Wang H B, Li Y Q, Chen L, et al. An SEU-tolerant DICE latch design with feedback transistors. IEEE Trans Nucl Sci, 2015, 62(2): 548 doi: 10.1109/TNS.2015.2399019[6] Nicolaidis M. Design for soft error mitigation. IEEE Trans Device Mater Reliab, 2005, 5: 405 doi: 10.1109/TDMR.2005.855790[7] Pontes J, Calazans N, Vivet P. Adding temporal redundancy to delay insensitive codes to mitigate single event effects. IEEE International Symposium on Asynchronous Circuits and Systems, 2012: 142[8] Carmichael C, Fuller E, Blain P, et al. SEU mitigation techniques for Virtex FPGAs in space applications. Proc Military and Aerospace Programmable Logic Devices Int Conf, 1999: C2[9] Calin T, Nicolaidis M, Velazco R. Upset hardened memory design for submicron CMOS technology. IEEE Trans Nucl Sci, 1996, 43(6): 2874 doi: 10.1109/23.556880[10] Huang Z F, Liang H G. A novel radiation hardened by design latch. J Semicond, 2009, 30(3): 035007 doi: 10.1088/1674-4926/30/3/035007[11] Makihara A, Yamaguchi T, Asai H, et al. Optimization for SEU/SET immunity on 0.15 μm fully depleted CMOS/SOI digital logic devices. IEEE Trans Nucl Sci, 2006, 53(6): 3422 doi: 10.1109/TNS.2006.885166[12] Rodbell K P, Heidel D F, Pellish J A, et al. 32 and 45 nm radiation-hardened-by-design (RHBD) SOI latches. IEEE Trans Nucl Sci, 2011, 58(6): 2702 doi: 10.1109/TNS.2011.2171715[13] Kauppila J S, Loveless T D, Quinn R C, et al. Utilizing device stacking for area efficient hardened SOI flip-flop designs. IEEE International Reliability Physics Symposium, 2014: SE.4.1[14] Wang H B, Chen L, Liu R, et al. An area efficient stacked latch design tolerant to SEU in 28 nm FDSOI technology. IEEE Trans Nucl Sci, 2016, 63(6): 3003 doi: 10.1109/TNS.2016.2627003[15] Zhao W, Cao Y. New generation of predictive technology model for sub-45 nm early design exploration. IEEE Trans Electron Devices, 2006, 53(11): 2816 doi: 10.1109/TED.2006.884077[16] She X, Li N, Tong J. SEU tolerant latch based on error detection. IEEE Trans Nucl Sci, 2012, 59(1): 211 doi: 10.1109/TNS.2011.2178265[17] Oliveira R, Jagirdar A, Chakraborty T J. A TMR scheme for SEU mitigation in scan flip-flops. Proc 8th Int Symp Qual Electron Des, 2007: 905[18] Iturbe X, Azkarate M, Martinez I, et al. A novel SEU, MBU and SHE handling strategy for xilinx virtex-4 FPGAs. Proc Int Conf Field Program Logic Appl, 2009: 569[19] Tanoue S, Ishida T, Ichinomiya Y, et al. A novel states recovery technique for the TMR softcore processor. Proc Int Conf Field Program Logic Appl, 2009: 543[20] Stroud C E. Reliability of majority voting based VLSI fault-tolerant circuits. IEEE Trans VLSI Syst, 1994, 2: 516 doi: 10.1109/92.335020[21] Huang Z. A high performance SEU-tolerant latch for nanoscale CMOS technology. J Electron Test, 2015, 31(4): 1[22] Rajaei R, Tabandeh M, Rashidian B. Single event upset immune latch circuit design using C-element. IEEE 9th International Conference on ASIC (ASICON), 2011: 252 -

Proportional views

DownLoad:

DownLoad: