| Citation: |

Gang Li, Pengjun Wang, Yaopeng Kang, Yuejun Zhang. A low standby-power fast carbon nanotube ternary SRAM cell with improved stability[J]. Journal of Semiconductors, 2018, 39(8): 085002. doi: 10.1088/1674-4926/39/8/085002

****

G Li, P J Wang, Y P Kang, Y J Zhang, A low standby-power fast carbon nanotube ternary SRAM cell with improved stability[J]. J. Semicond., 2018, 39(8): 085002. doi: 10.1088/1674-4926/39/8/085002.

|

A low standby-power fast carbon nanotube ternary SRAM cell with improved stability

DOI: 10.1088/1674-4926/39/8/085002

More Information

-

Abstract

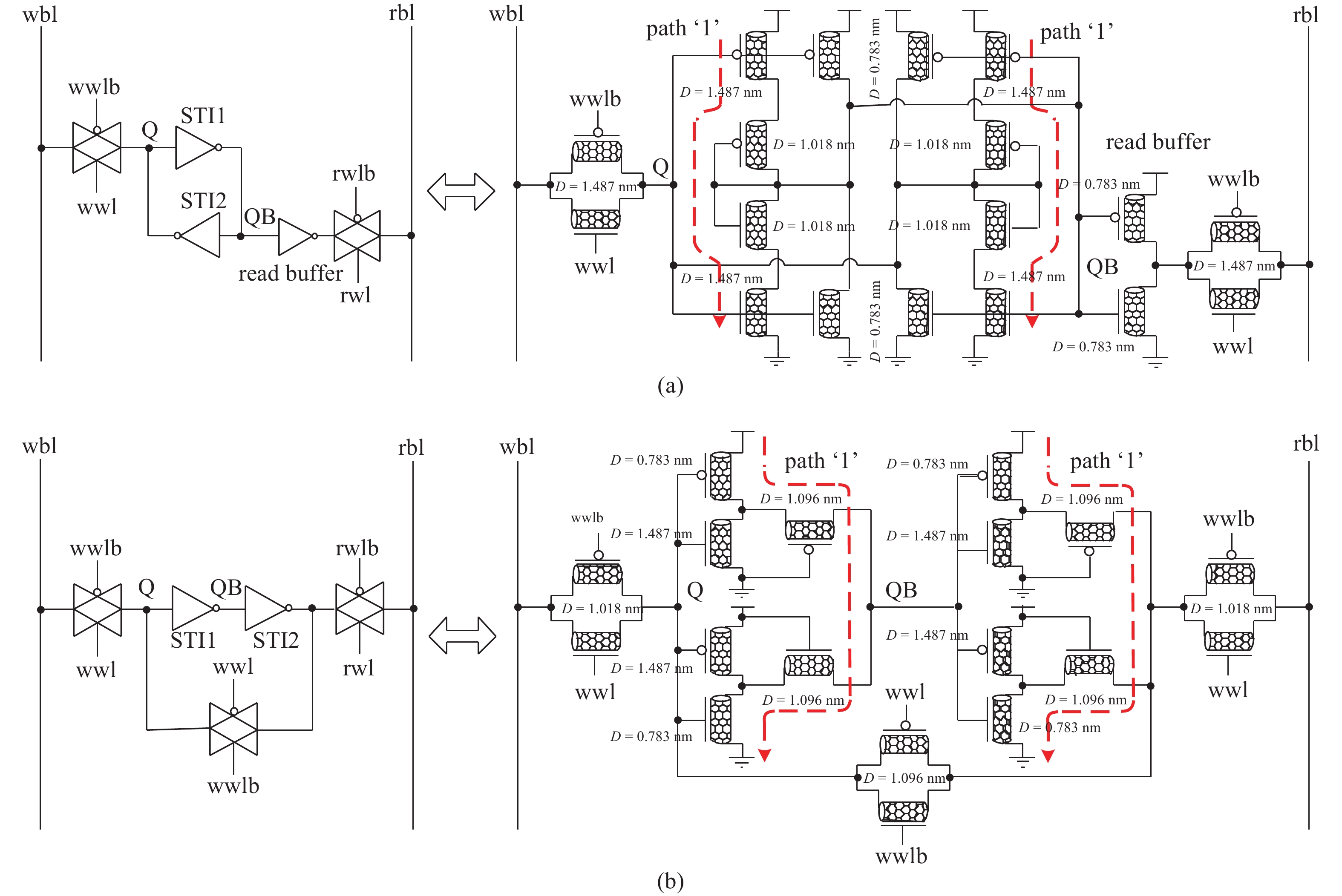

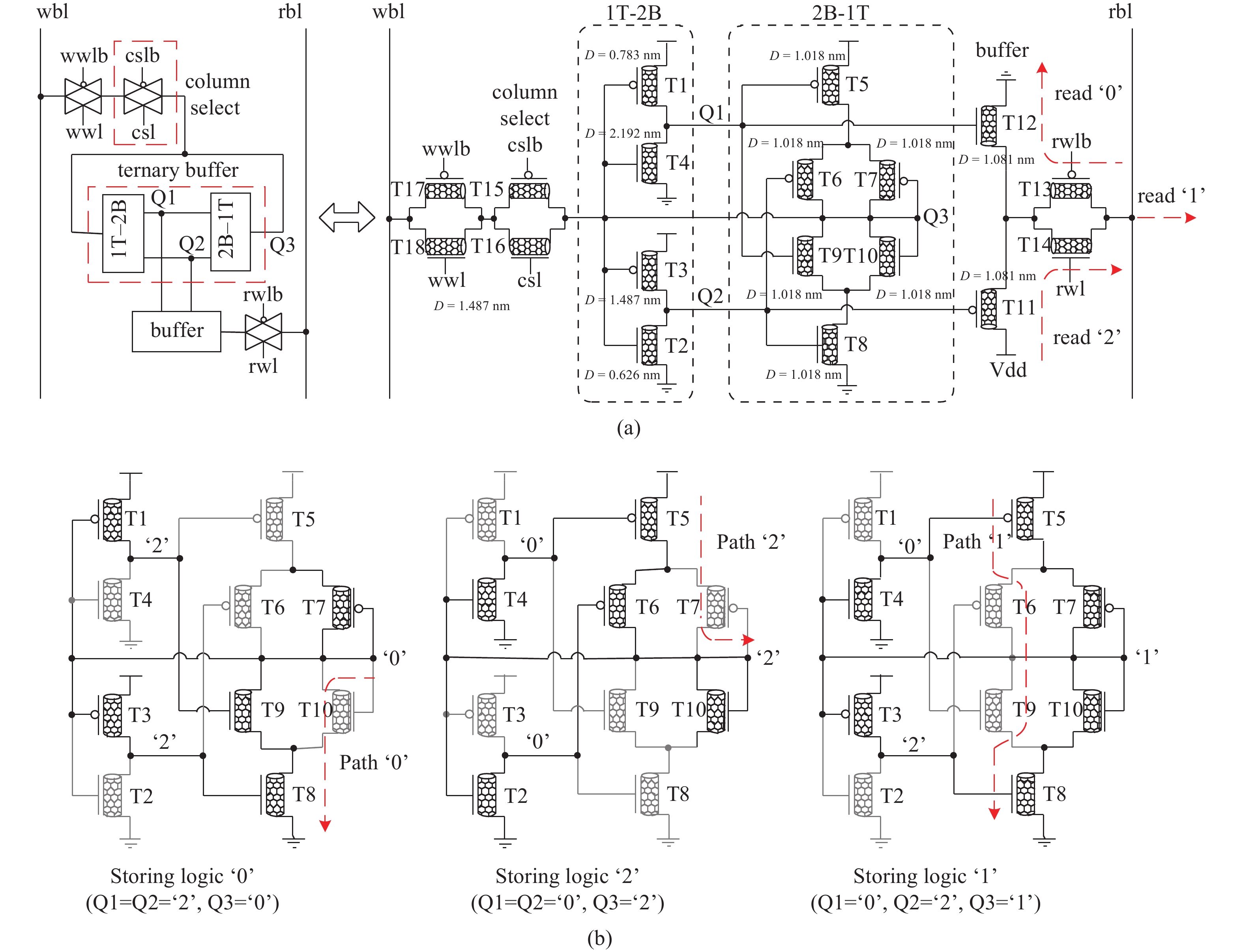

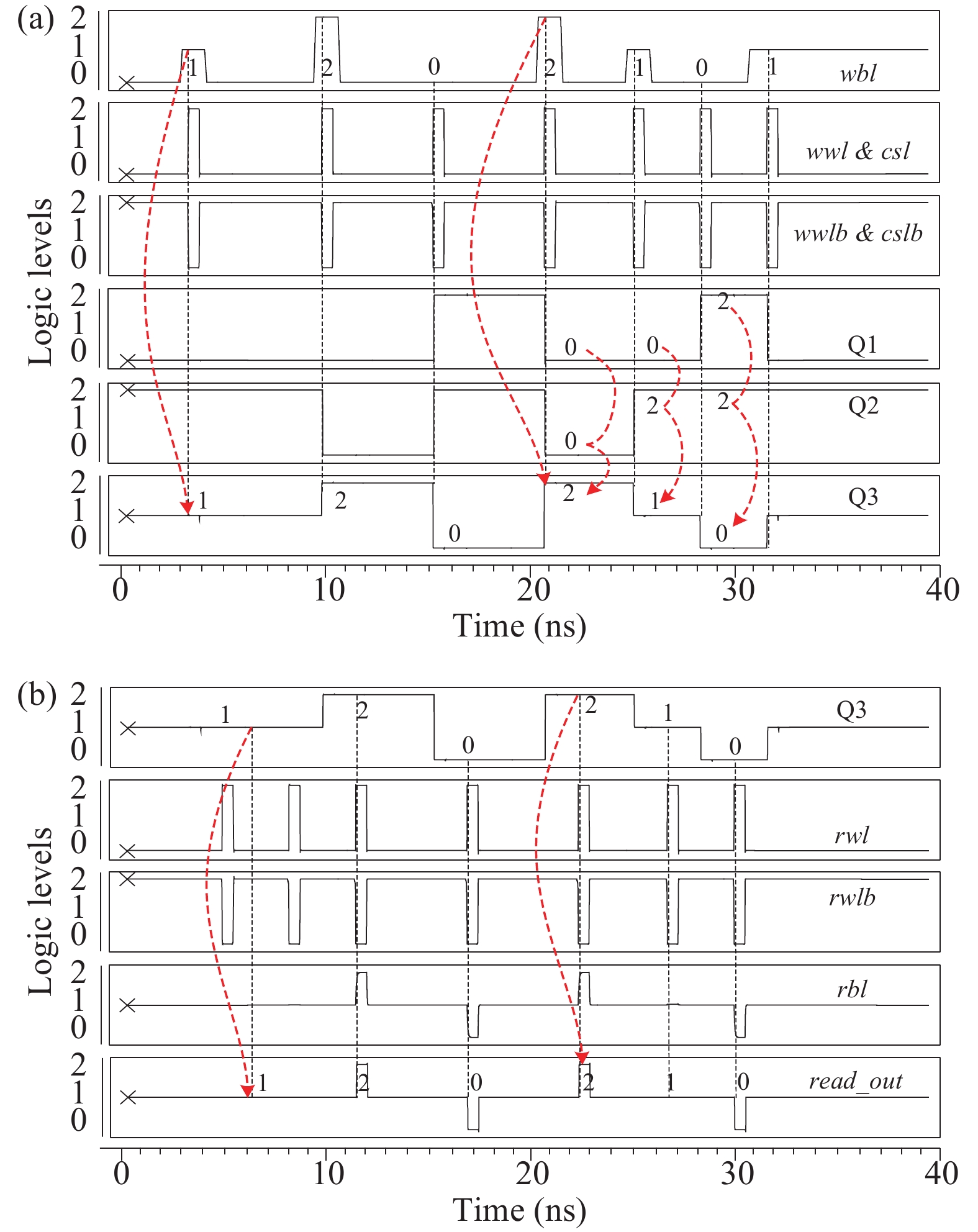

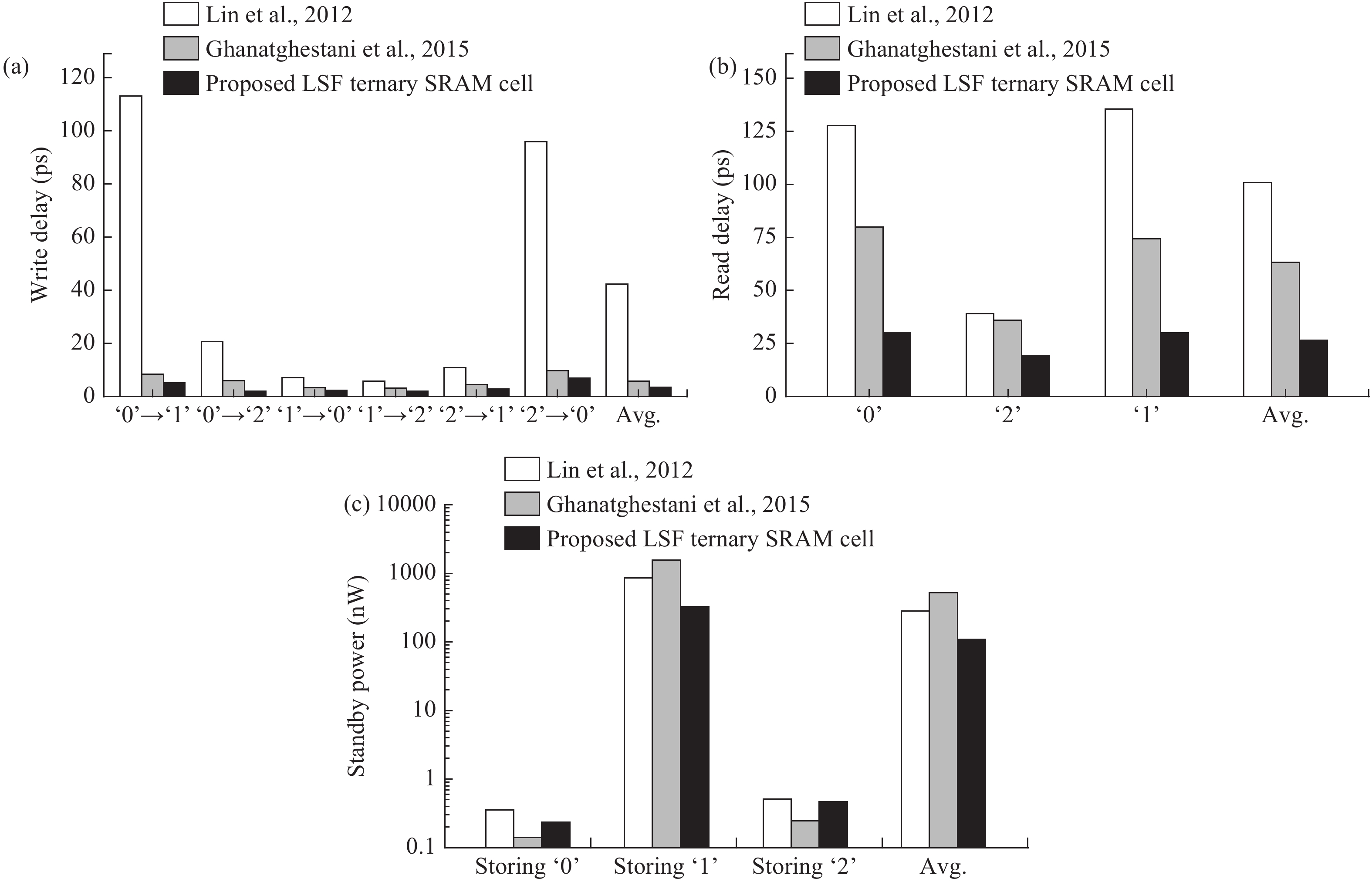

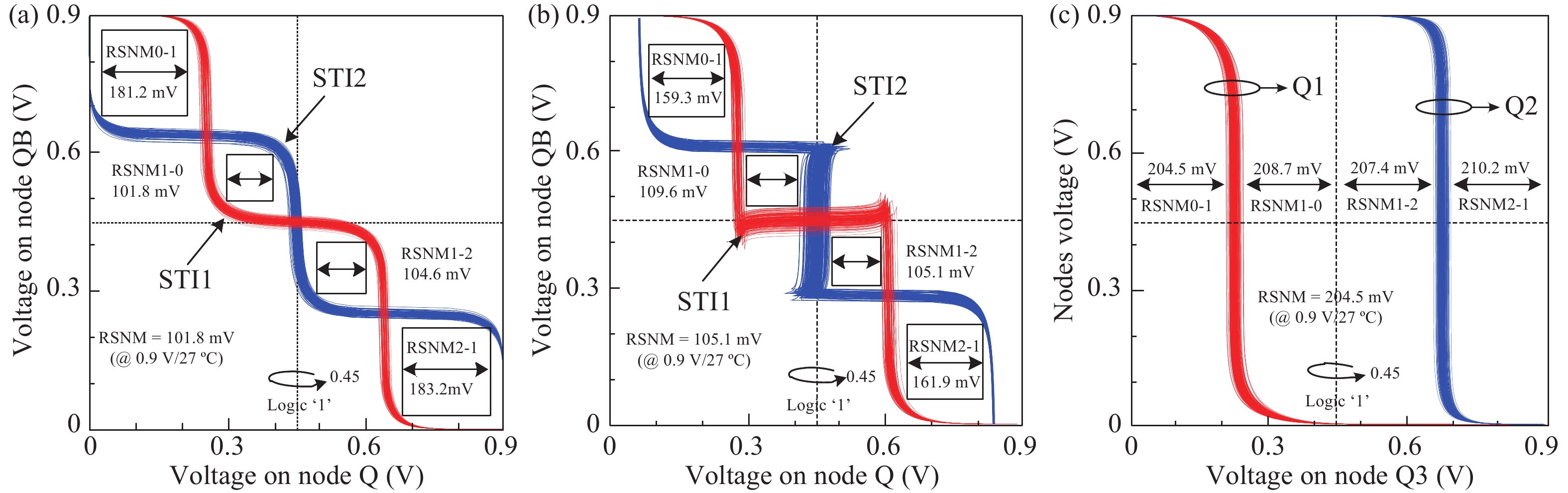

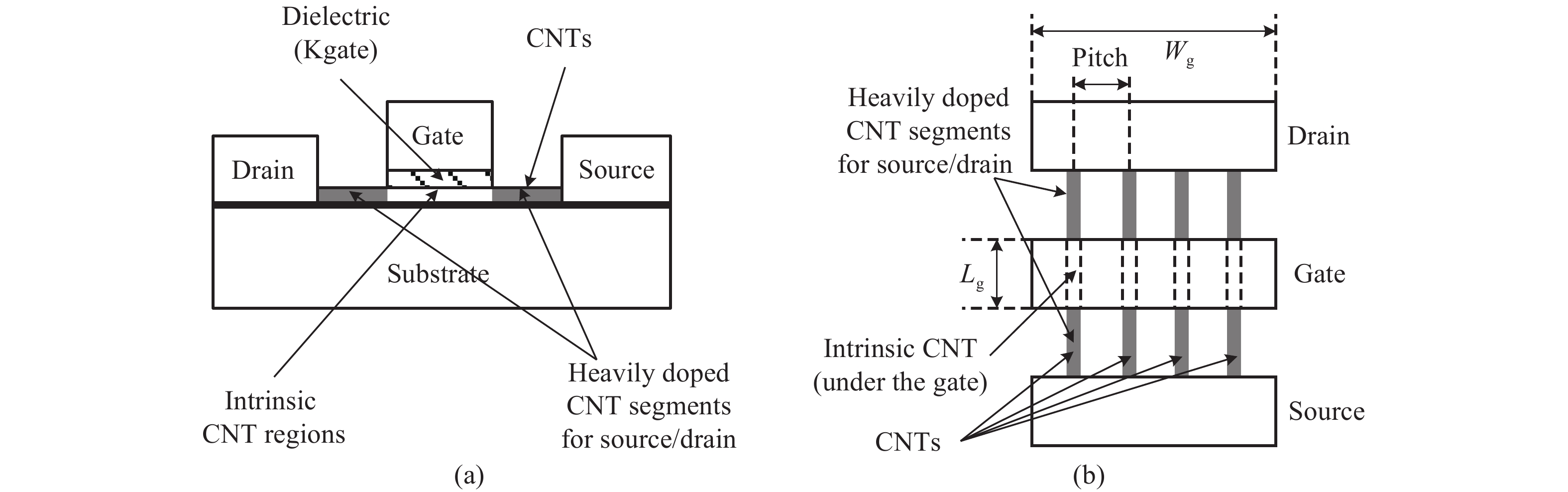

Power dissipation, speed and stability are the most important parameters for multiple-valued SRAM design. To reduce the power consumption and further improve the performance of the ternary SRAM cell, we propose a low standby-power fast ternary SRAM cell based on carbon nanotube field effect transistors (CNFETs). The performance is simulated in terms of three criteria including standby-power, delay (write and read) and stability (RSNM). Compared to the novel ternary SRAM cell, our results show that the average standby-power, write and read delay of the proposed cell are reduced by 78.1%, 39.6% and 58.2%, respectively. In addition, the RSNM under process variations is 2.01× and 1.95× of the conventional and novel ternary SRAM cells, respectively.-

Keywords:

- CNFETs,

- ternary SRAM cell,

- low standby-power,

- high stability

-

References

[1] Cho G, Lombardi F. Design and process variation analysis of CNTFET-based ternary memory cells. Integr VLSI J, 2011, 54(C): 97[2] Kamar Z, Nepal K. Noise margin-optimized ternary CMOS SRAM delay and sizing characteristics. IEEE International Midwest Symposium on Circuits and Systems (MWSCAS), 2010: 801[3] Zhang Y J, Wang P J, Xiong B Y, et al. Design of a high information-density multiple valued 2-read 1-write register file. IEICE Electron Express, 2012, 9(11): 958 doi: 10.1587/elex.9.958[4] Appenzeller J. Carbon nanotubes for high-performance electronics—progress and prospect. Proc IEEE, 2008, 96(2): 201 doi: 10.1109/JPROC.2007.911051[5] Lin Y M, Appenzeller J, Knoch J, et al. High performance carbon nanotube field-effect transistor with tunable polarities. IEEE Trans Nanotechnol, 2005, 4(5): 481 doi: 10.1109/TNANO.2005.851427[6] Qiu C, Zhang Z, Xiao M, et al. Scaling carbon nanotube complementary transistors to 5-nm gate lengths. Science, 2017, 355(6322): 271 doi: 10.1126/science.aaj1628[7] You K, Nepal K. Design of a ternary static memory cell using carbon nanotube-based transistors. IET Micro & Nano Lett, 2011, 6(6): 381[8] Lin S, Kim Y B, Lombardi F. Design of a ternary memory cell using CNTFETs. IEEE Trans Nanotechnol, 2012, 11(5): 1019 doi: 10.1109/TNANO.2012.2211614[9] Ghanatghestani M M, Pedram H, Ghavami B. Design of a low-standby power and high-speed ternary memory cell based on carbon nanotube field-effect transistor. J Comput Theor Nanosci, 2015, 12(12): 5457 doi: 10.1166/jctn.2015.4546[10] Ebrahim A, Abdolreza D. A novel design of low power and high read stability ternary SRAM (T-SRAM), memory based on the modified gate diffusion input (m-GDI) method in nanotechnology. Microelectron J, 2016, 58: 44 doi: 10.1016/j.mejo.2016.10.009[11] Shin K, Choi W, Park J. Half-select free and bit-line sharing 9T SRAM for reliable supply voltage scaling. IEEE Trans Circ Syst I, 2017, 64(8): 2036[12] Deng J, Wong H S P. A compact SPICE model for carbon-nanotube field effect transistors including nonidealities and its application-part II: model of the intrinsic channel region. IEEE Trans Electron Devices, 2007, 54(12): 3186 doi: 10.1109/TED.2007.909030[13] Tabrizchi S, Azimi N, Navi K. A novel ternary half adder and multiplier based on carbon nanotube field effect transistors. Front Inform Technol Electron Eng, 2017, 18(3): 423 doi: 10.1631/FITEE.1500366[14] Prabhu C M R, Singh A K. Low-power fast (LPF) SRAM cell for write/read operation. IEICE Electron Express, 2011, 8(18): 1473 doi: 10.1587/elex.8.1473 -

Proportional views

DownLoad:

DownLoad: