| Citation: |

Huan Li, Haimeng Huang, Xingbi Chen. An improved SOI trench LDMOST with double vertical high-k insulator pillars[J]. Journal of Semiconductors, 2018, 39(9): 094009. doi: 10.1088/1674-4926/39/9/094009

****

H Li, H M Huang, X B Chen, An improved SOI trench LDMOST with double vertical high-k insulator pillars[J]. J. Semicond., 2018, 39(9): 094009. doi: 10.1088/1674-4926/39/9/094009.

|

An improved SOI trench LDMOST with double vertical high-k insulator pillars

DOI: 10.1088/1674-4926/39/9/094009

More Information

-

Abstract

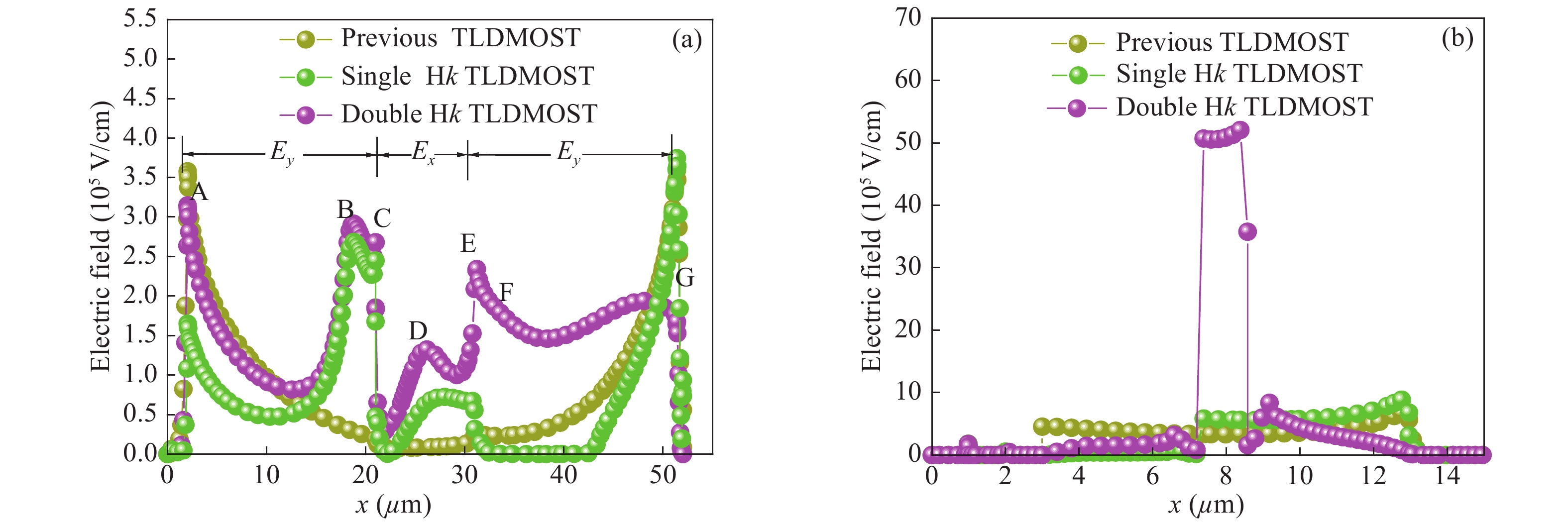

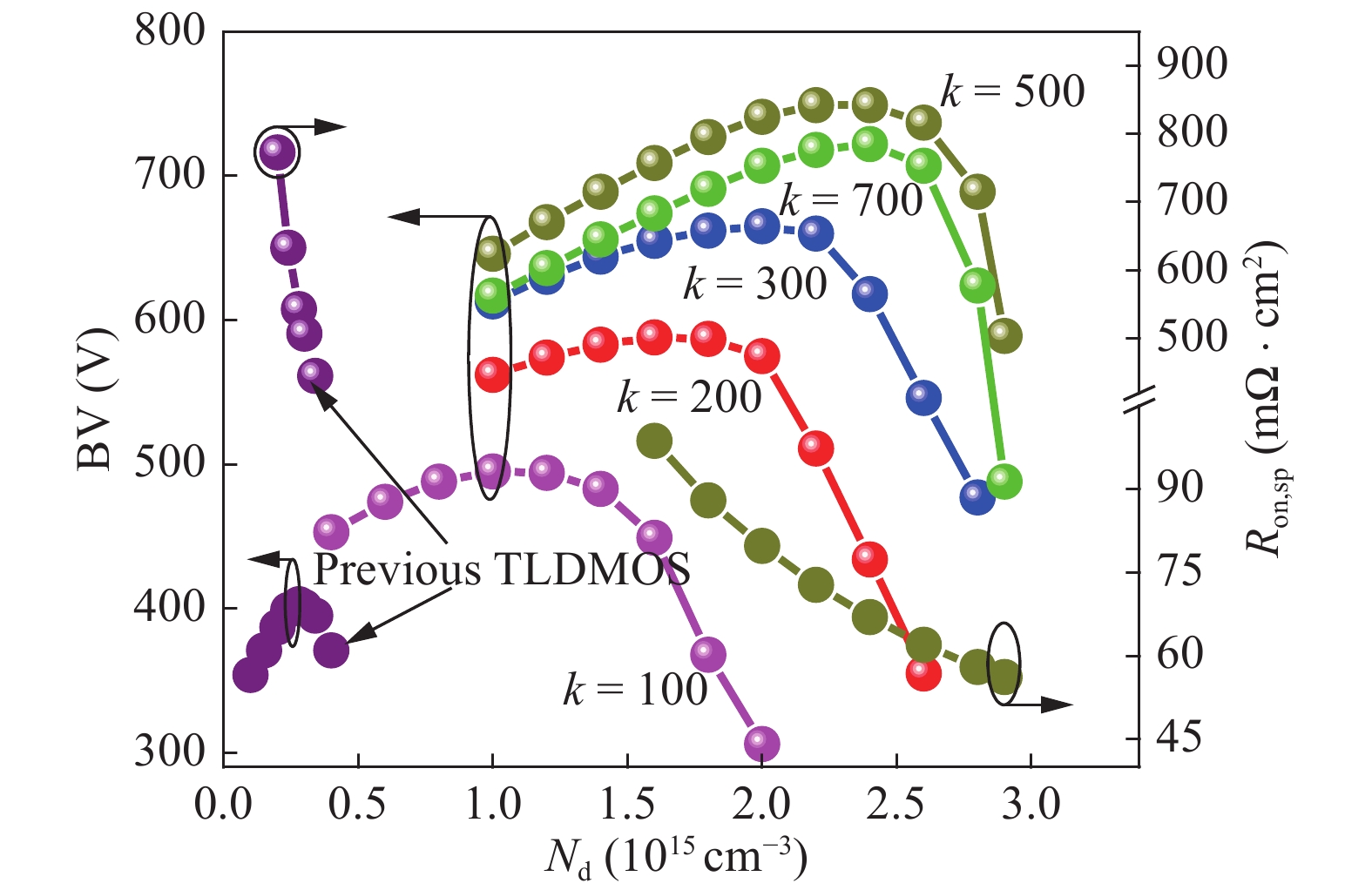

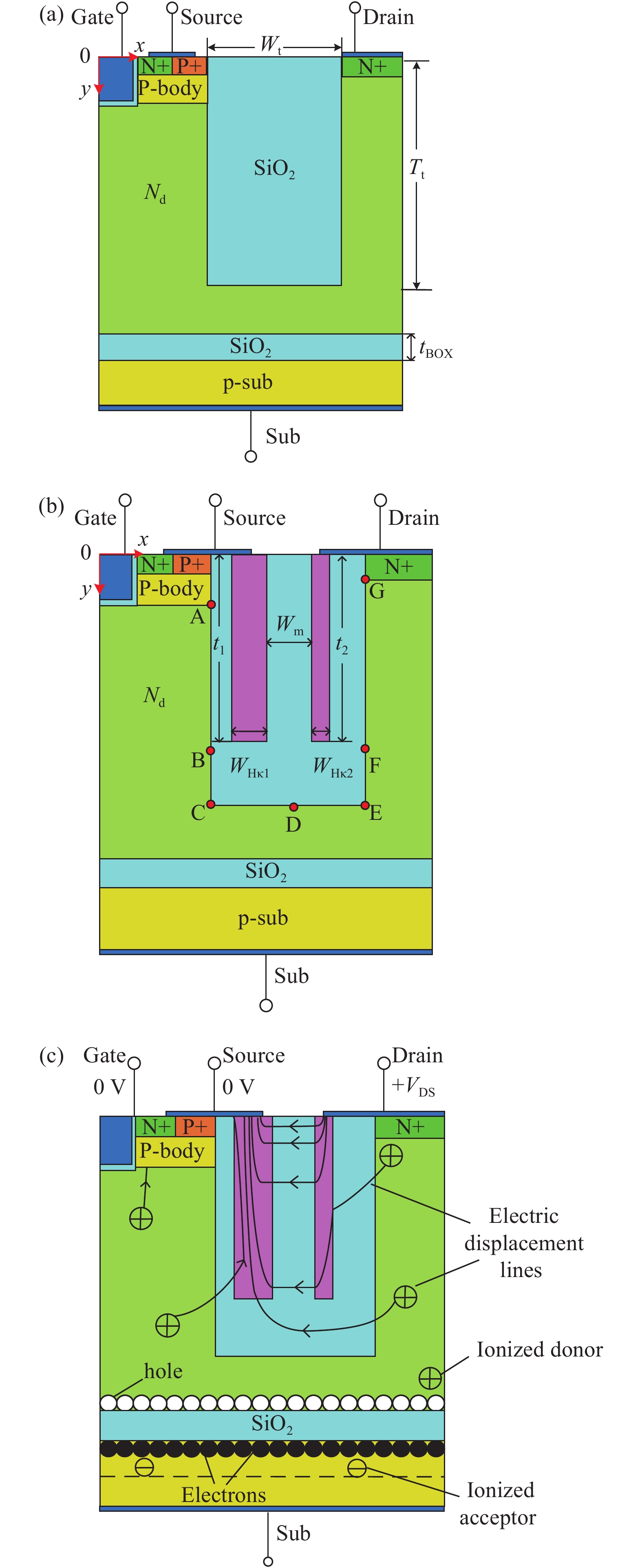

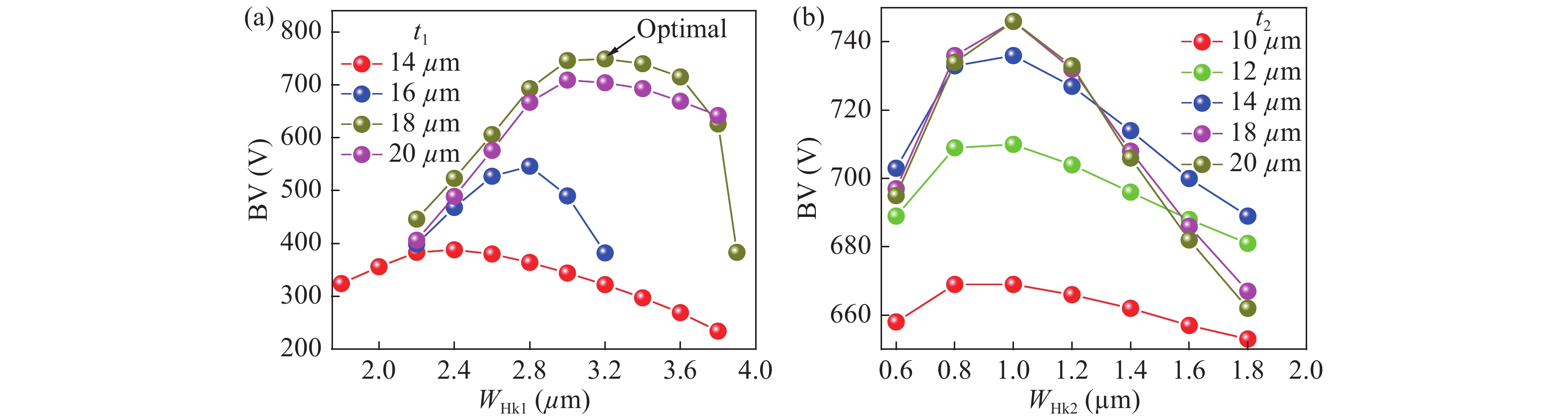

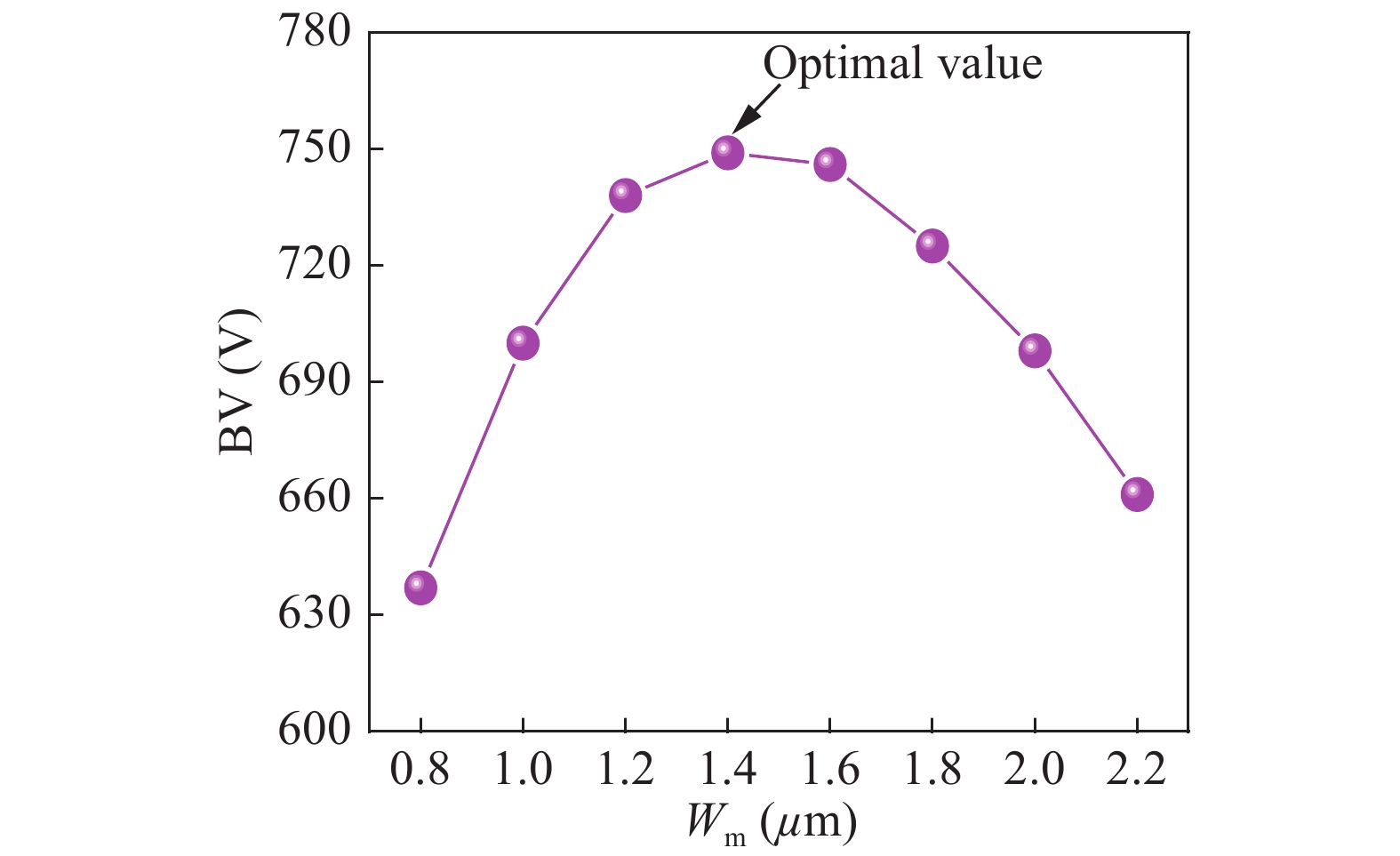

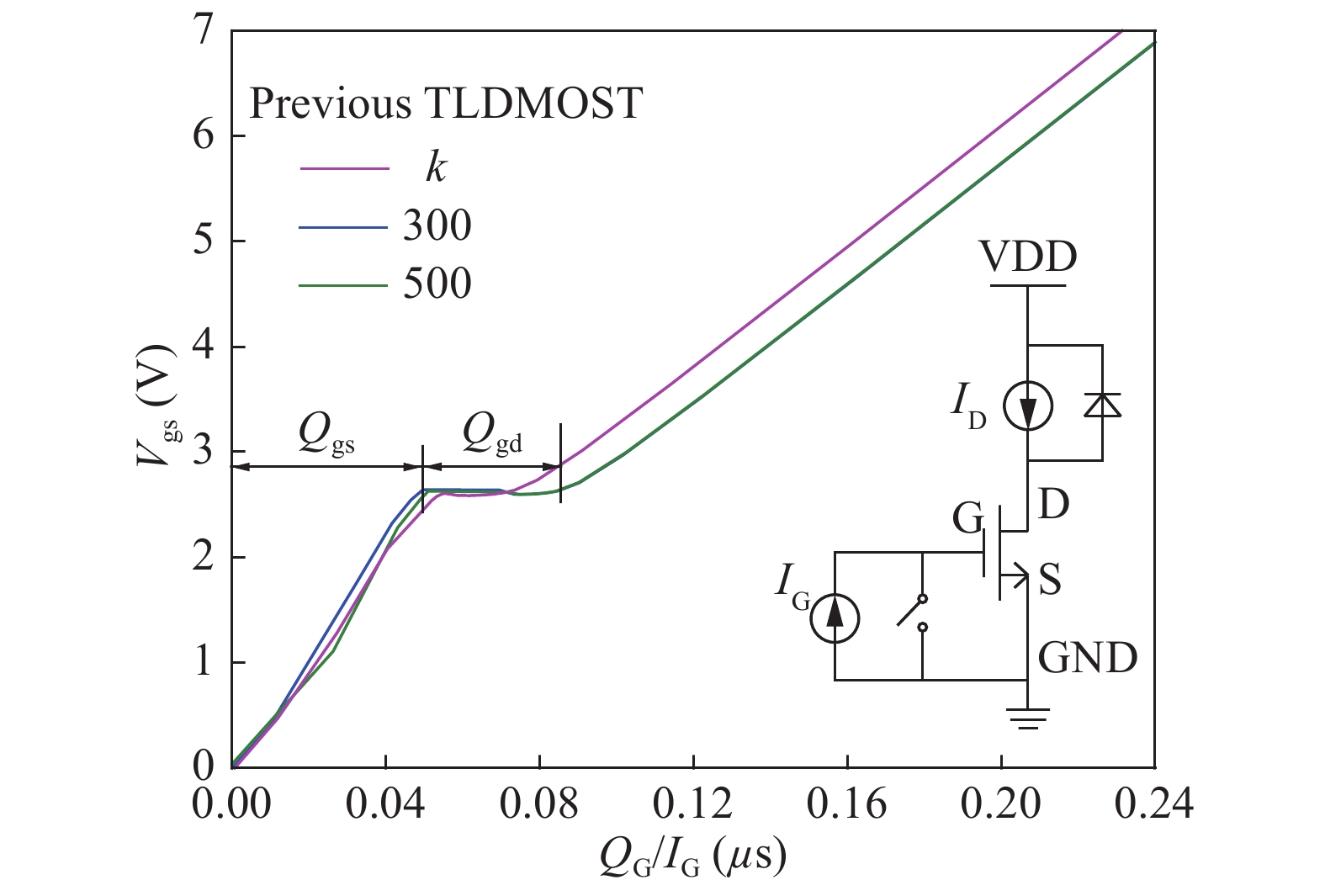

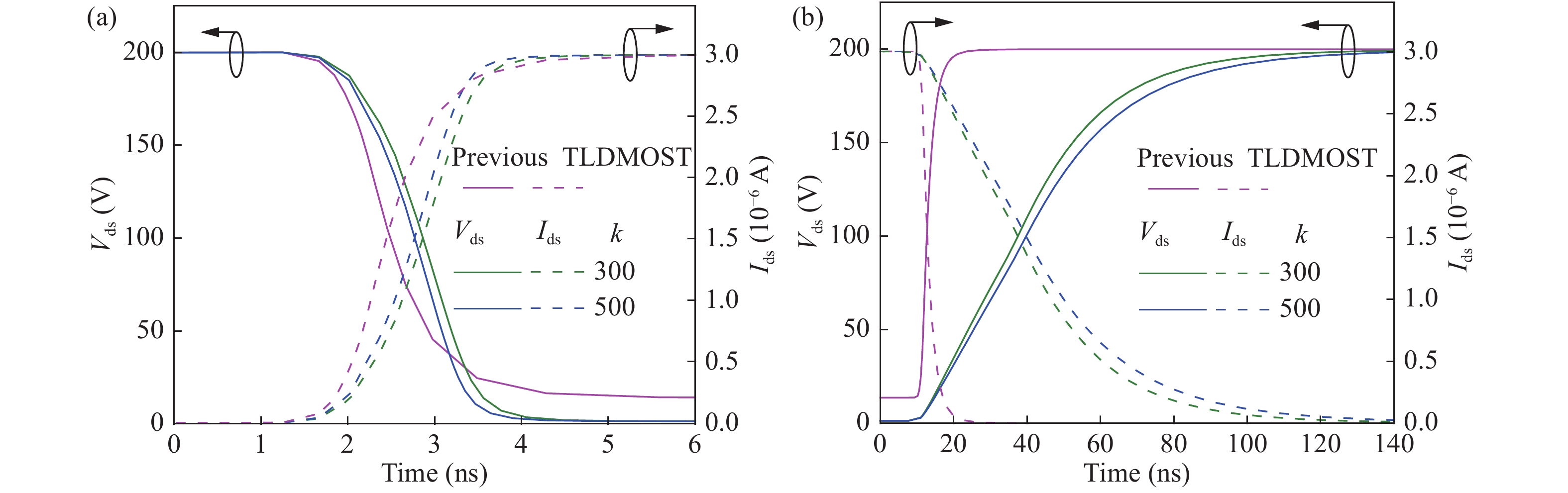

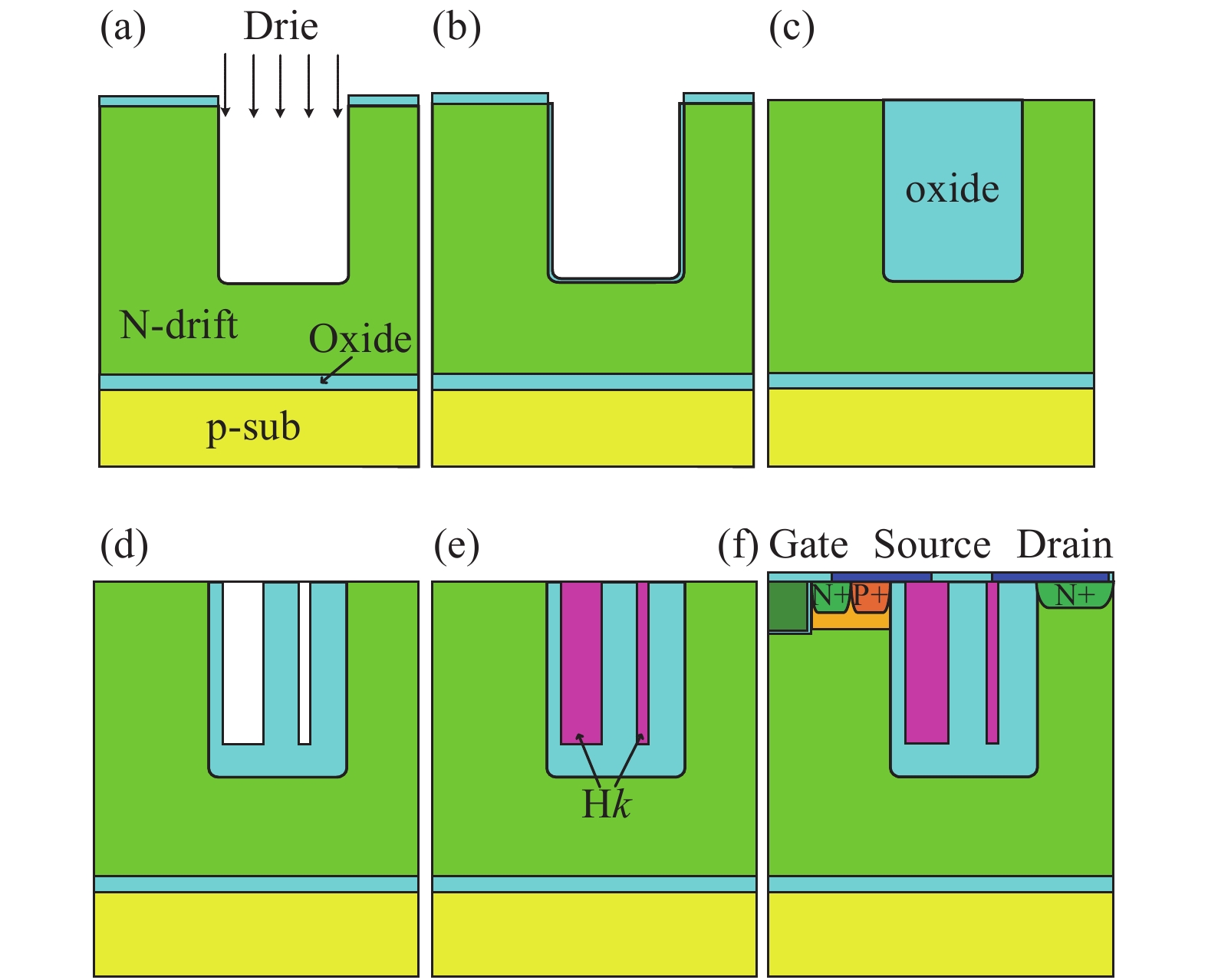

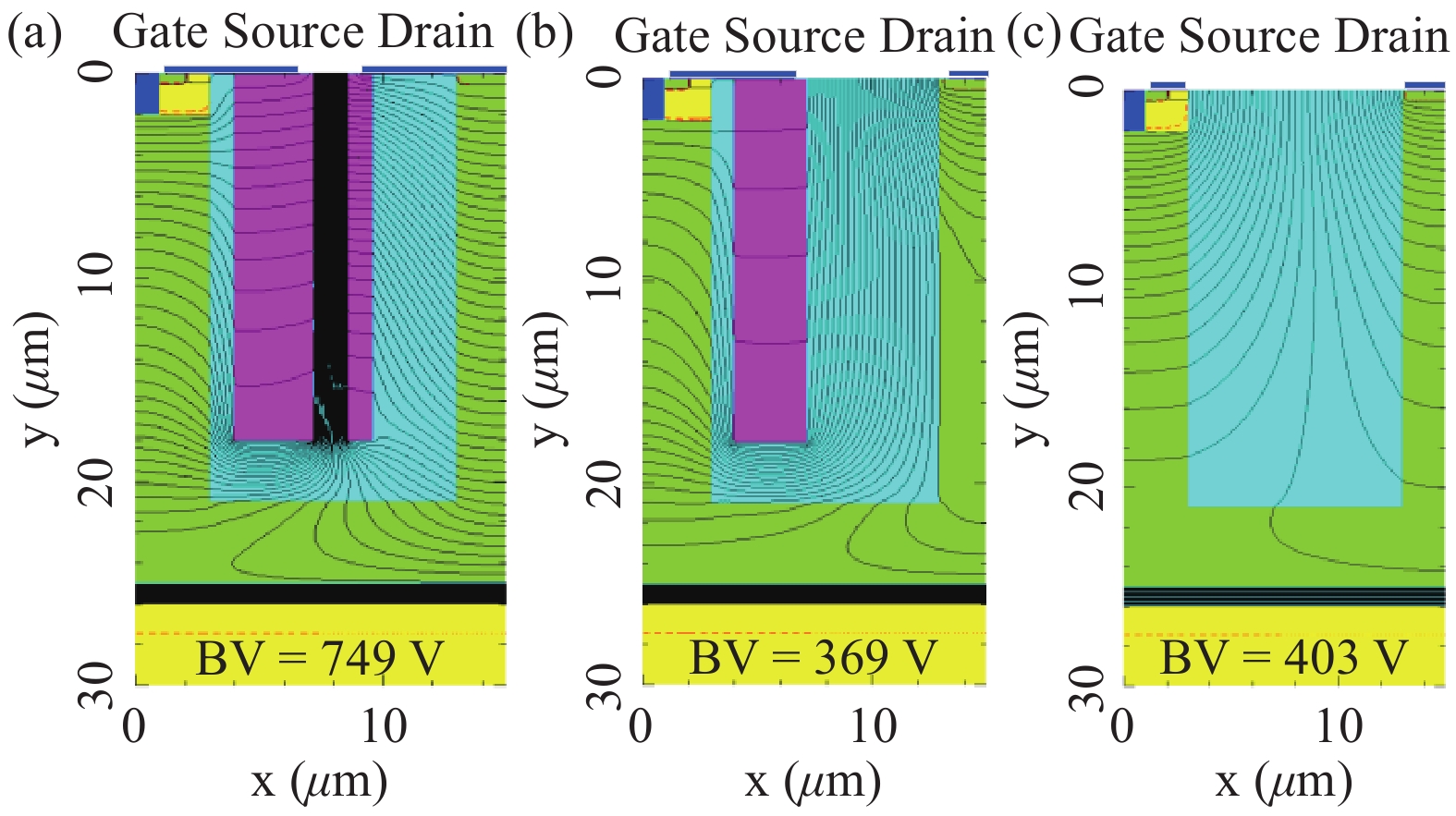

An SOI trench LDMOST (TLDMOST) with ultra-low specific on-resistance (Ron,sp) is proposed. It features double vertical high-k insulator pillars (Hk1 and Hk2) in the oxide trench, which are connected to the source electrode and drain electrode, respectively. Firstly, under reverse bias voltage, most electric displacement lines produced by the charges of the depleted drift region in the source side go through the Hk1, and thus the average electric field strength under the source can be enhanced. Secondly, two additional electric field peaks are induced by the Hk1, which further modulate the electric field in the drift region under the source. Thirdly, most electric displacement lines produced by the charges of the depleted drift region in the drain side enter into the Hk2. This not only introduces one more electric field peak at the corner of the oxide trench around the Hk2, but also forms the enhanced vertical reduced surface field effect, which modulates the electric field in the drift region under the drain. With the effects of the two Hk insulator pillars, the breakdown voltage (BV) and the drift region doping concentration are significantly improved. The simulation results indicate that compared with the oxide trench LDMOST (previous TLDMOST) with the same geometry, the proposed double Hk TLDMOST enhances the BV by 86% and reduces the Ron,sp by 88%.-

Keywords:

- breakdown voltage,

- high-k,

- specific on-resistance,

- trench LDMOST

-

References

[1] Qiao M, Wang Z K, Wang Y R, et al. 3-D Edge termination design and Ron,sp-BV model of a 700-V triple RESURF LDMOS with n-type top layer. IEEE Trans Electron Devices, 2017, 64(6): 2579 doi: 10.1109/TED.2017.2694451[2] Miao R Y, Lu F, Wang Y Y, et al. Deep oxide trench termination structure for super-junction MOSFET. Electron Lett, 2012, 48(16): 1018 doi: 10.1049/el.2012.2061[3] Varadarajan K R, Chow T P, Wang J, et al. 250 V integrable silicon lateral trench power MOSFETs with superior specific on-resistance. Proceedings of the 19th International Symposium on Power Semiconductor Devices and IC’s (ISPSD), 2007: 233[4] Lu D H F, Jimbo S, Fujishima N. A low on-resistance high voltage SOI LIGBT with oxide trench in drift region and hole bypass gate configuration. IEEE International Electron Devices Meeting, 2005: 381[5] Zhang W T, Qiao M, Wu L J, et al. Ultra-low specific on-resistance SOI high voltage trench LDMOS with dielectric field enhancement based on ENBULF concept. Proceedings of the 25th ISPSD, 2013: 329[6] Chao X, Cheng X H, Wang Z J, et al. Improvement of SOI trench LDMOS performance with double vertical metal field plate. IEEE Trans Electron Devices, 2014, 61(10): 3477 doi: 10.1109/TED.2014.2349553[7] He G, Chen X S, Sun Z Q. Interface engineering and chemistry of Hf-based high-k dielectrics on III–V substrates. Surf Sci Rep, 2013, 68(1): 68 doi: 10.1016/j.surfrep.2013.01.002[8] He G, Deng B, Chen H S, et al. Effect of dimethylaluminumhydride-derived aluminum oxynitride passivation layer on the interface chemistry and band alignment of HfTiO–InGaAs gate stacks. APL Mater, 2013, 1: 012104 doi: 10.1063/1.4808243[9] He G, Liu J W, Chen H S, et al. Interface control and modification of band alignment and electrical properties of HfTiO/GaAs gate stacks by nitrogen incorporation. J Mater Chem C, 2014, 2(27): 5299 doi: 10.1039/C4TC00572D[10] Zhang J W, He G, Zhou L, et al. Microstructure optimization and optical and interfacial properties modulation of sputtering-derived HfO2 thin films by TiO2 incorporation. J Alloys Comp, 2014, 611: 253 doi: 10.1016/j.jallcom.2014.05.074[11] He G, Gao J, Chen H S, et al. Modulating the interface quality and electrical properties of HfTiO/InGaAs gate stack by atomic-layer-deposition-derived Al2O3 passivation layer. ACS Appl Mater Interfaces, 2014, 6(24): 22013 doi: 10.1021/am506351u[12] Chen X B, Huang M M. A vertical power MOSFET with an interdigitated drift region using high-k insulator. IEEE Trans Electron Devices, 2012, 59(9): 2430 doi: 10.1109/TED.2012.2204890[13] Chen X B. Super-junction voltage sustaining layer with alternating semiconductor and high-k dielectric regions. US Patent, No. 7230310, 2007[14] Li J H, Li P, Huo W R, et al. Analysis and fabrication of an LDMOS with high-permittivity dielectric. IEEE Electron Device Lett, 2011, 32(9): 1266 doi: 10.1109/LED.2011.2158383[15] Guo Y F, Yao J F, Zhang B, et al. Variation of lateral width technique in SOI high-voltage lateral double-diffused metal–oxide–semiconductor transistors using high-k dielectric. IEEE Electron Device Lett, 2015, 36(3): 262 doi: 10.1109/LED.2015.2393913[16] Cai X Y, Frisbie C D, Leighton C. Optimized dielectric properties of SrTiO3 : Nb/SrTiO3 (001) films for high field effect charge densities. Appl Phys Lett, 2006, 89(24): 242915 doi: 10.1063/1.2404610[17] User’s Manual of Two-Dimensional Device Simulation Program MEDICI, Version 2001.2, Synopsys MEDICI User’s Manual, Synopsys Inc., Mountain View, CA, USA, 2010[18] Naugarhiya A, Kondekar P N. High permittivity material selection for design of optimum Hk VDMOS. Superlatt Microstruct, 2015, 83: 310 doi: 10.1016/j.spmi.2015.02.045[19] Chen X B. Surface (lateral) voltage-sustaining region with an insulator film containing conductive particles. US Patent, No. 0175657, 2013[20] Yi B, Lin Z, Chen X B. Study on HK-VDMOS with deep trench termination. Superlatt Microstruct, 2014, 83: 278[21] Donohue L A, Hopkins J, Barnett R, et al. Developments in Si and SiO2 etching for MEMS-based optical applications. Proc SPIE, 2003, 5347: 44[22] Schaepkens M, Oehrlein G S. A review of SiO2 etching studies in inductively coupled fluorocarbon plasmas. J Electrochem Soc, 2001, 148(3): C211 doi: 10.1149/1.1348260 -

Proportional views

DownLoad:

DownLoad: