| Citation: |

Ruiqi Luo, Xiaolei Chen, Yajun Ha. A routing algorithm for FPGAs with time-multiplexed interconnects[J]. Journal of Semiconductors, 2020, 41(2): 022405. doi: 10.1088/1674-4926/41/2/022405

****

R Q Luo, X L Chen, Y J Ha, A routing algorithm for FPGAs with time-multiplexed interconnects[J]. J. Semicond., 2020, 41(2): 022405. doi: 10.1088/1674-4926/41/2/022405.

|

A routing algorithm for FPGAs with time-multiplexed interconnects

DOI: 10.1088/1674-4926/41/2/022405

More Information

-

Abstract

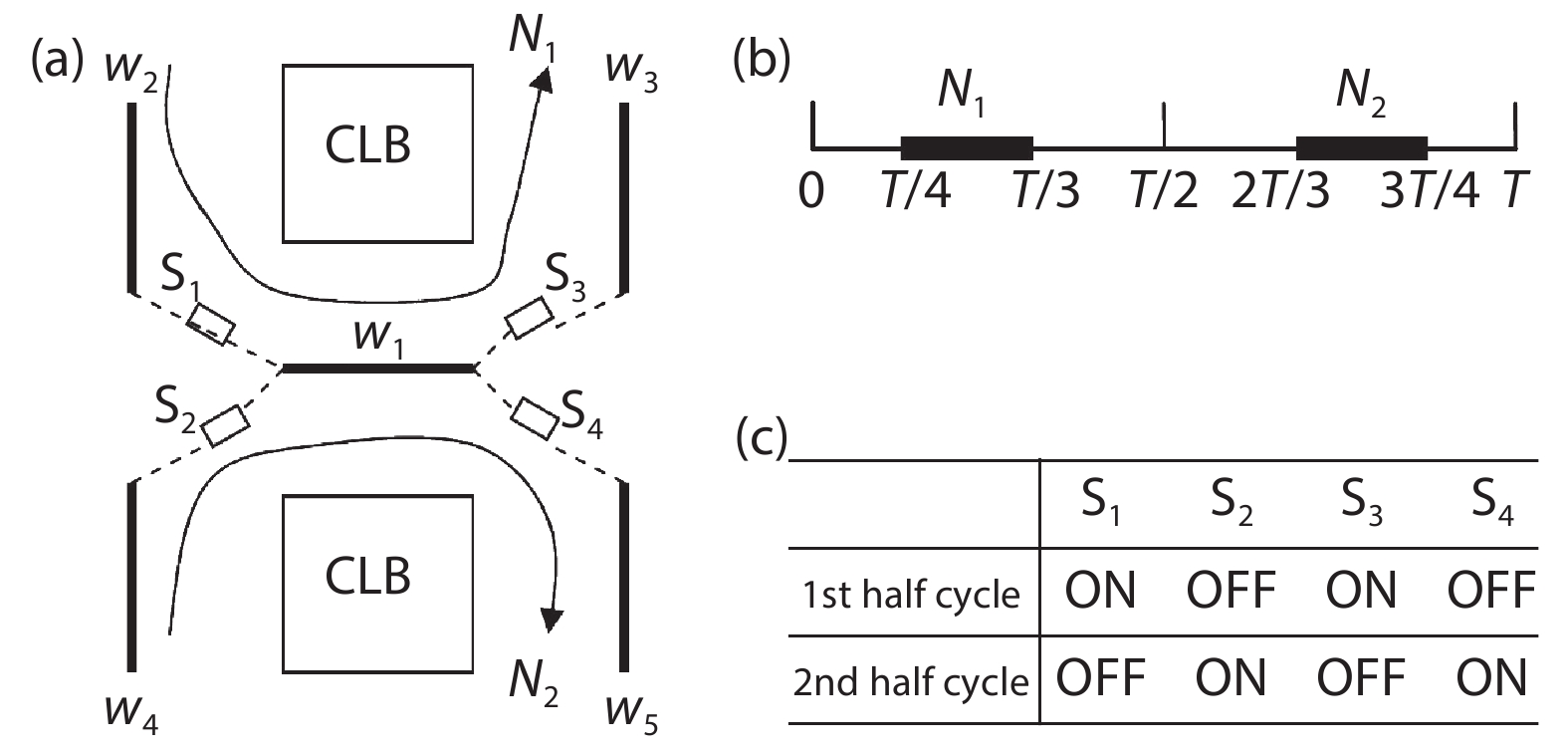

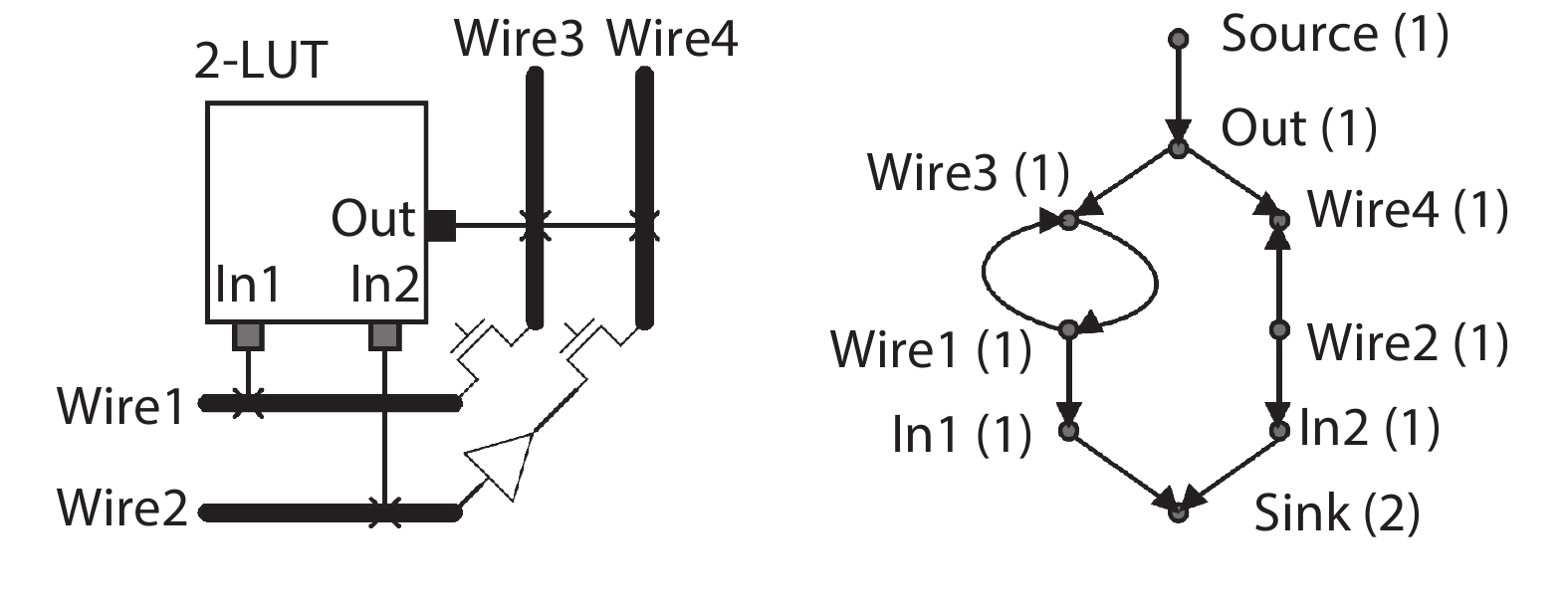

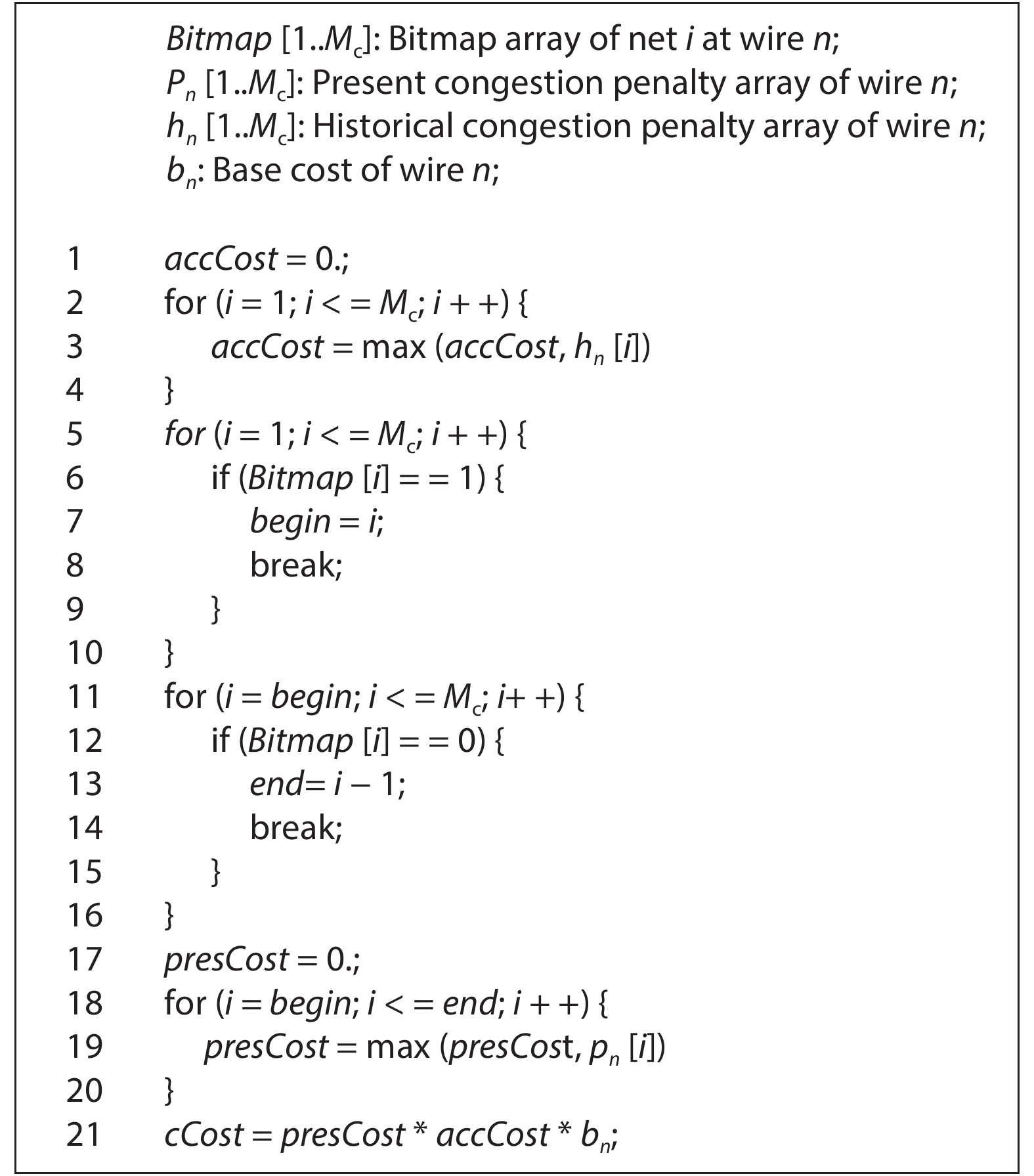

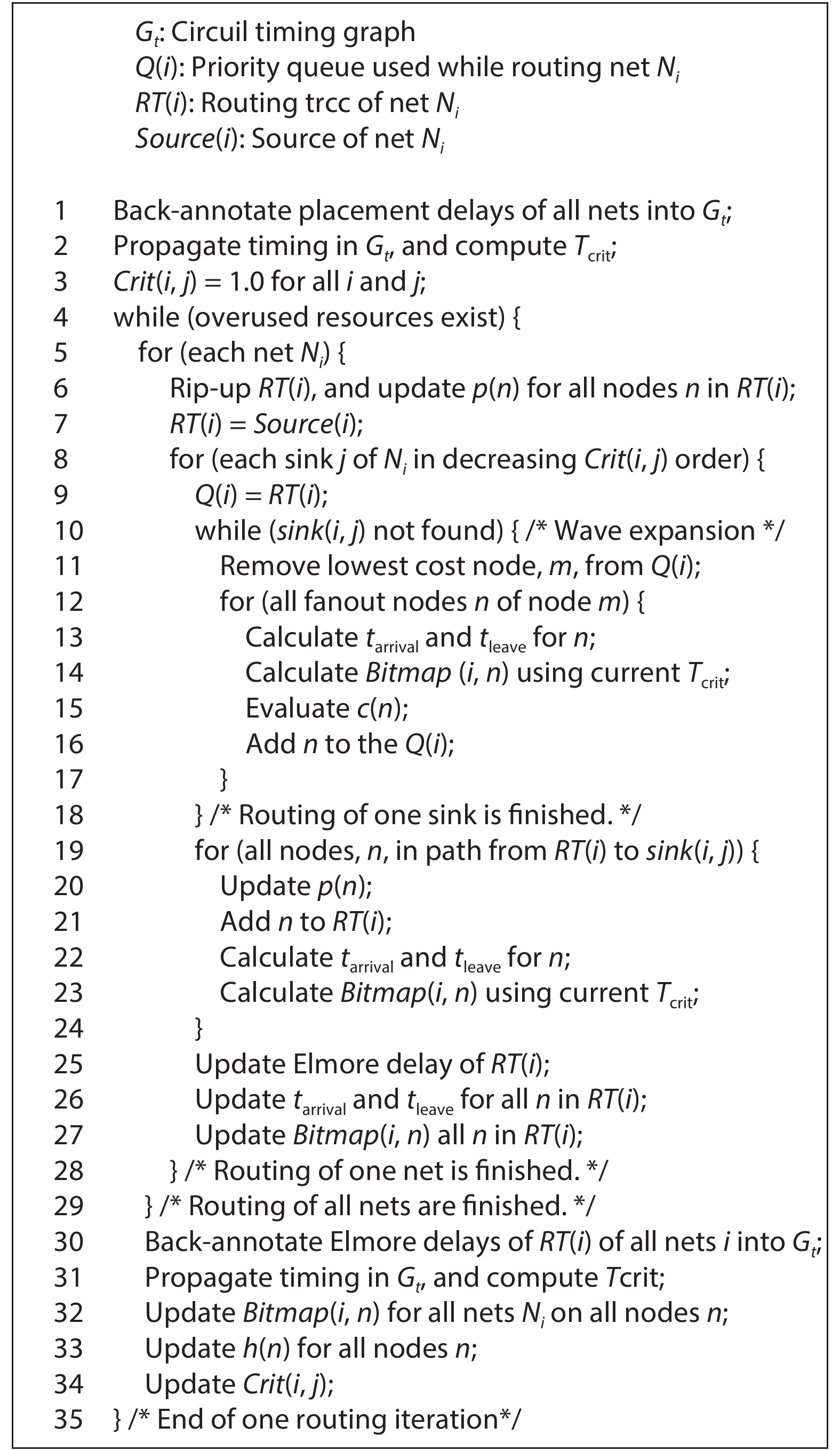

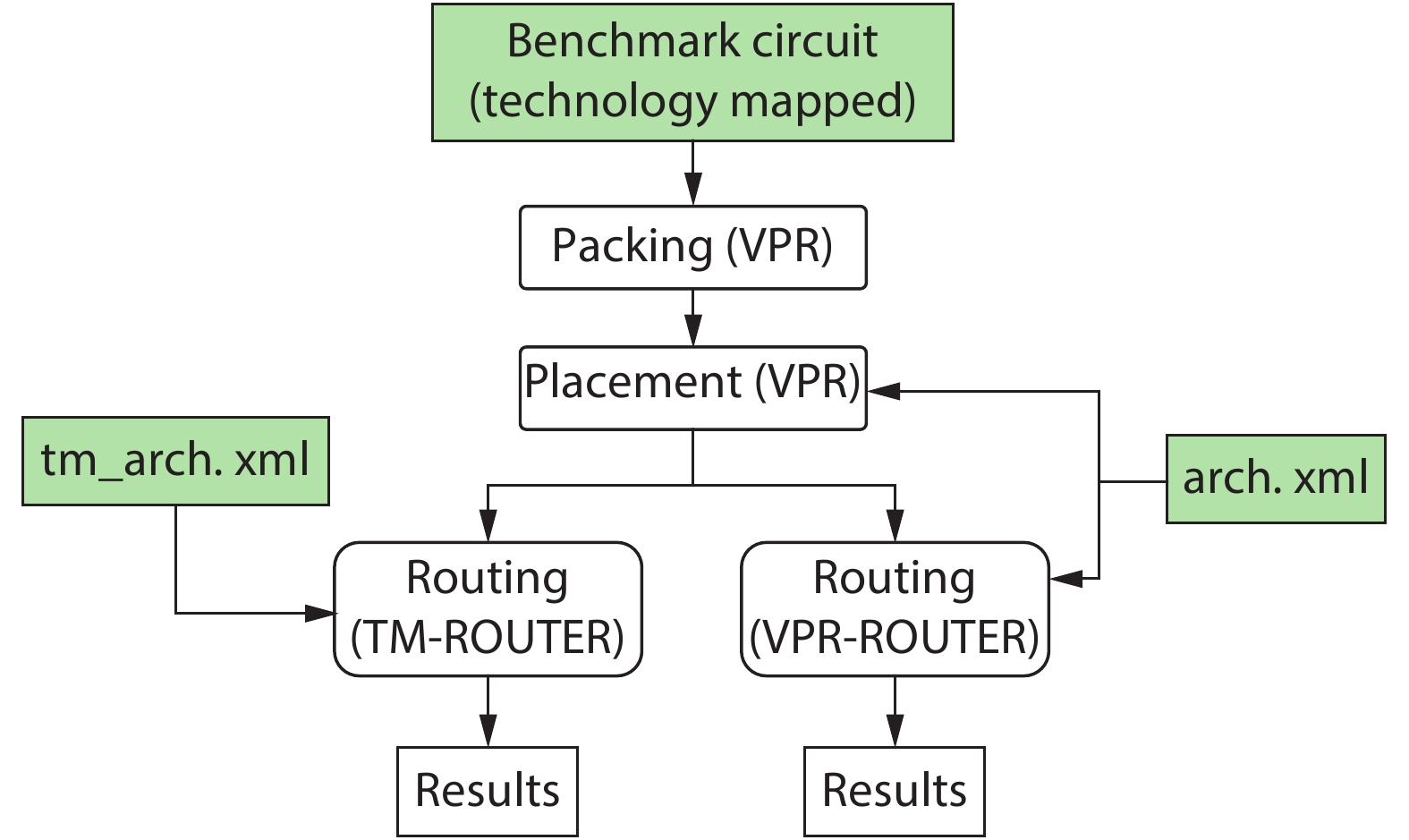

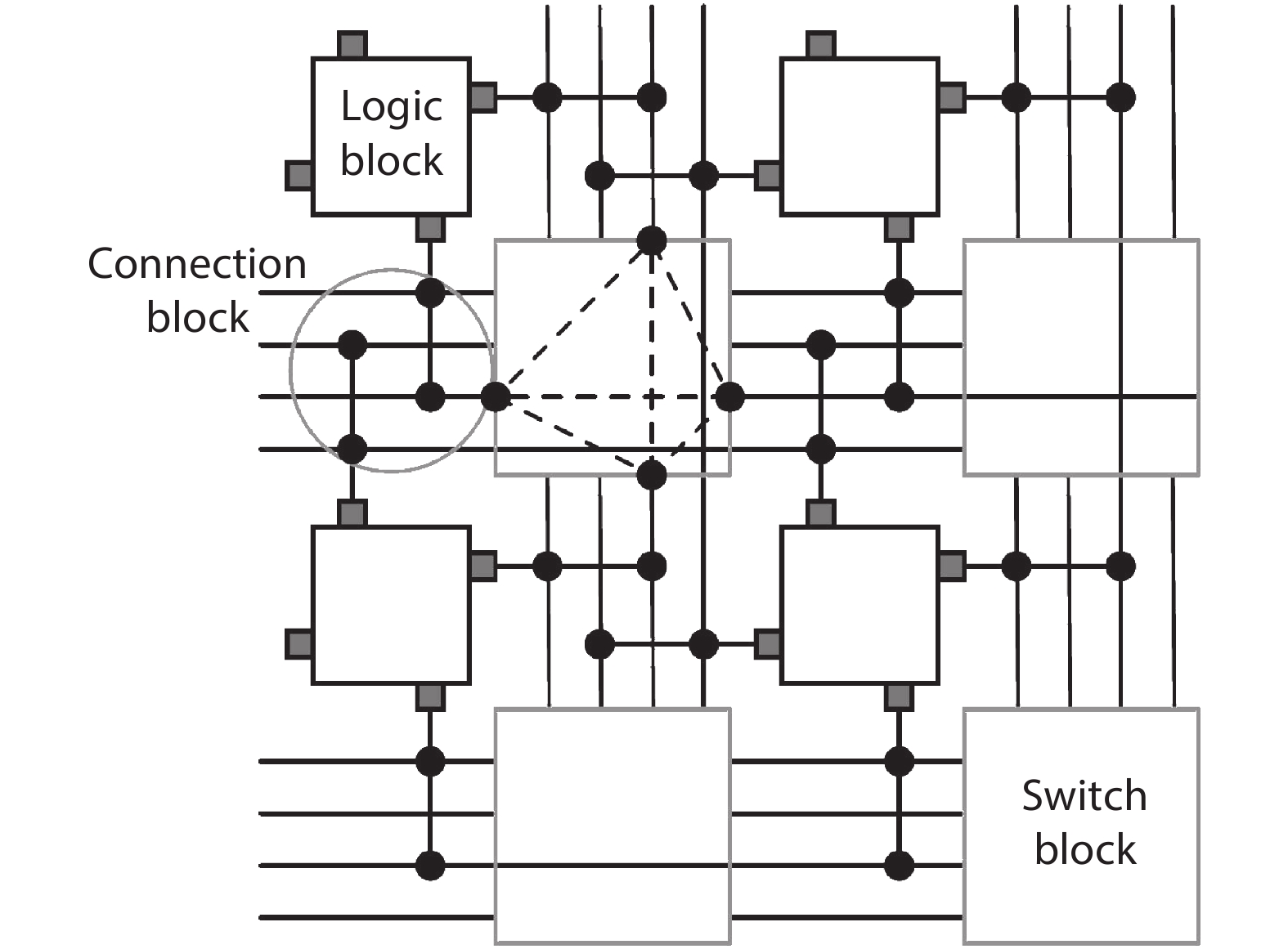

Previous studies show that interconnects occupy a large portion of the timing budget and area in FPGAs. In this work, we propose a time-multiplexing technique on FPGA interconnects. In order to fully exploit this interconnect architecture, we propose a time-multiplexed routing algorithm that can actively identify qualified nets and schedule them to multiplexable wires. We validate the algorithm by using the router to implement 20 benchmark circuits to time-multiplexed FPGAs. We achieve a 38% smaller minimum channel width and 3.8% smaller circuit critical path delay compared with the state-of-the-art architecture router when a wire can be time-multiplexed six times in a cycle. -

References

[1] Lemieux G, Lewis D. Design of interconnection networks for programmable logic. Dordrecht: Kluwer Academic Publishers, 2004[2] Trimberger S, Carberry D, Johnson A, et al. A time-multiplexed FPGA. The 5th Annual IEEE Symposium on Field-Programmable Custom Computing Machines, 1997, 22[3] Betz V, Rose J. VPR: A new packing, placement and routing tool for FPGA research. International Workshop on Field Programmable Logic and Applications. Springer, Berlin, Heidelberg, 1997, 213[4] Luu J, Kuon I, Jamieson P, et al. VPR 5.0: FPGA CAD and architecture exploration tools with single-driver routing, heterogeneity and process scaling. ACM Trans Reconfig Technol Syst, 2011, 4(4), 32 doi: 10.1145/2068716.2068718[5] Trimberger S. Scheduling designs into a time-multiplexed FPGA. Proceedings of the 1998 ACM/SIGDA Sixth International Symposium on Field Programmable Gate Arrays, 1998, 153[6] Lin C C, Chang D, Wu Y L, et al. Time-multiplexed routing resources for FPGA design. Proceedings of Custom Integrated Circuits Conference, 1996, 152[7] Francis R, Moore S, Mullins R. A network of time-division multiplexed wiring for FPGAs. Proceedings of the Second ACM/IEEE International Symposium on Networks-on-Chip, 2008, 35[8] Shen M, Zhang W, Luo G, et al. Serial-equivalent static and dynamic parallel routing for FPGAs. IEEE Trans Comput-Aid Des Integr Circuits Syst, 2018 doi: 10.1109/TCAD.2018.2887050[9] Shen M, Luo G, Xiao N. Exploiting box expansion and grid partitioning for parallel FPGA routing. 2018 IEEE 26th Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM), 2018, 209[10] Shen M, Luo G. Accelerate FPGA routing with parallel recursive partitioning. Proceedings of the IEEE/ACM International Conference on Computer-Aided Design, 2015, 118[11] Shen M, Xiao N. Fine-grained parallel routing for FPGAs with selective expansion. 2018 IEEE 36th International Conference on Computer Design (ICCD), 2018, 577[12] Shen M, Xiao N. Raparo: resource-level angle-based parallel routing for FPGAs. 2019 IEEE 27th Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM), 2019, 312[13] Shen M, Luo G. Megrez: Parallelizing FPGA routing with strictly-ordered partitioning. 2017 IEEE 25th Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM), 2017, 27[14] Vercruyce D, Vansteenkiste E, Stroobandt D. CRoute: a fast high-quality timing-driven connection-based FPGA router. 2019 IEEE 27th Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM), 2019, 53[15] Wang D, Duan Z, Tian C, et al. A runtime optimization approach for FPGA routing. IEEE Trans Comput-Aid Des Integ Circuits Syst, 2017, 37(8), 1706 doi: 10.1109/TCAD.2017.2768416[16] Patil S B, Liu T, Tessier R. A bandwidth-optimized routing algorithm for hybrid FPGA networks-on-chip. 2018 IEEE 26th Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM), 2018, 25[17] Chaplygin Y, Novozhilov I, Losev V, et al. Algorithm for design and structure optimization of the FPGA routing block with a given number of trace signals. 2019 IEEE Conference of Russian Young Researchers in Electrical and Electronic Engineering (EIConRus), 2019, 1589[18] Farooq U, Chotin-Avot R, Azeem M, et al. Using timing-driven inter-FPGA routing for multi-FPGA prototyping exploration. 2016 Euromicro Conference on Digital System Design (DSD), 2016, 641[19] Omam S R, Tang X, Gaillardon P E, et al. A study on buffer distribution for RRAM-based FPGA routing structures. 2015 IEEE 6th Latin American Symposium on Circuits and Systems (LASCAS), 2015, 1[20] Chen S C, Chang Y W. FPGA placement and routing. Proceedings of the 36th International Conference on Computer Aided Design, 2017, 914[21] Huriaux C, Sentieys O, Tessier R. Effects of I/O routing through column interfaces in embedded FPGA fabrics. 2016 26th International Conference on Field Programmable Logic and Applications (FPL), 2016, 1[22] Kashif A, Khalid M A S. Experimental evaluation and comparison of time-multiplexed multi-FPGA routing architectures. 2016 IEEE 59th International Midwest Symposium on Circuits and Systems (MWSCAS), 2016, 1[23] Palczewski M. Plane parallel A* maze router and its application to FPGAs. Proceedings 29th ACM/IEEE Design Automation Conference, 1992, 6911[24] McMurchie L, Ebeling C. PathFinder: a negotiation-based performance-driven router for FPGAs. Proceedings of the 1995 ACM Third International Symposium on Field-Programmable Gate Arrays, 1995, 111[25] Sapatnekar S. Timing. Springer Science & Business Media, 2004[26] Kuon I, Rose J. iFAR–intelligent FPGA architecture repository. 2008 -

Proportional views

DownLoad:

DownLoad: