| Citation: |

Jiaqi Yang, Ting Li, Mingyuan Yu, Shuangshuang Zhang, Fujiang Lin, Lin He. On the design of high-speed energy-efficient successive-approximation logic for asynchronous SAR ADCs[J]. Journal of Semiconductors, 2017, 38(8): 085007. doi: 10.1088/1674-4926/38/8/085007

****

J Q Yang, T Li, M Y Yu, S S Zhang, F J Lin, L He. On the design of high-speed energy-efficient successive-approximation logic for asynchronous SAR ADCs[J]. J. Semicond., 2017, 38(8): 085007. doi: 10.1088/1674-4926/38/8/085007.

|

On the design of high-speed energy-efficient successive-approximation logic for asynchronous SAR ADCs

DOI: 10.1088/1674-4926/38/8/085007

More Information

-

Abstract

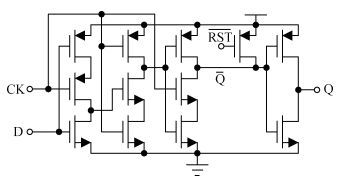

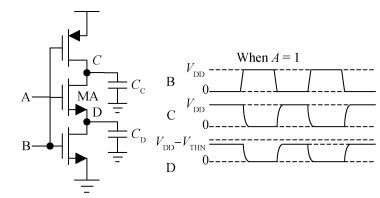

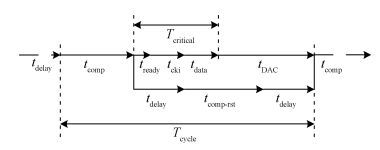

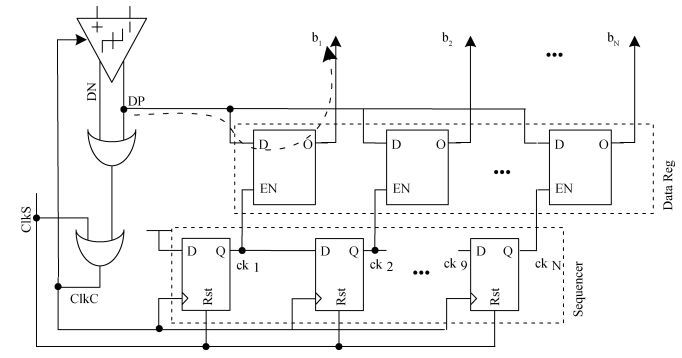

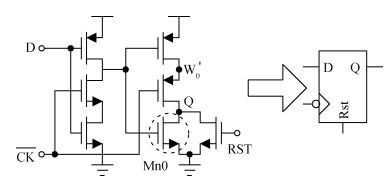

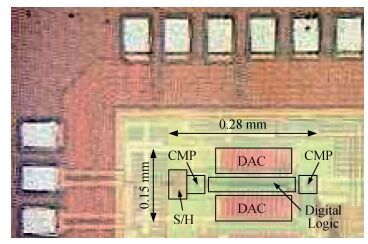

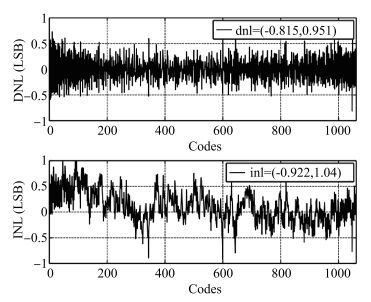

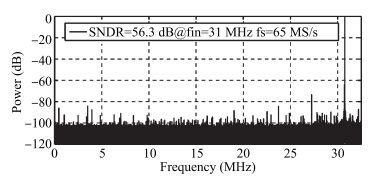

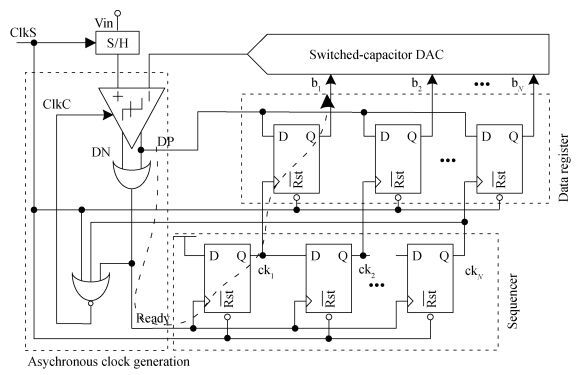

This paper analyzes the power consumption and delay mechanisms of the successive-approximation (SA) logic of a typical asynchronous SAR ADC, and provides strategies to reduce both of them. Following these strategies, a unique direct-pass SA logic is proposed based on a full-swing once-triggered DFF and a self-locking tri-state gate. The unnecessary internal switching power of a typical TSPC DFF, which is commonly used in the SA logic, is avoided. The delay of the ready detector as well as the sequencer is removed from the critical path. A prototype SAR ADC based on the proposed SA logic is fabricated in 130 nm CMOS. It achieves a peak SNDR of 56.3 dB at 1.2 V supply and 65 MS/s sampling rate, and has a total power consumption of 555 μ W, while the digital part consumes only 203 μ W. -

References

[1] Harpe P J A, Zhou C, Bi Y, et al. A 26 W 8 bit 10 MS/s asynchronous SAR ADC for low energy radios. IEEE J Solid-State Circuits, 2011, 46(7):1585 doi: 10.1109/JSSC.2011.2143870[2] Zhu Z, Qiu Z, Liu M, et al. A 6-to-10-bit 0.5 V-to-0.9 V reconfigurable 2 MS/s power scalable SAR ADC in 0.18μm CMOS. IEEE Trans Circuits Syst I, 2015, 62(3):689 doi: 10.1109/TCSI.2014.2377431[3] Zhang D, Bhide A, Alvandpour A. A 53-nW 9.1-ENOB 1-kS/s SAR ADC in 0.13-μm CMOS for medical implant devices. IEEE J Solid-State Circuits, 2012, 47(7):1585 doi: 10.1109/JSSC.2012.2191209[4] Huang H, Ao K, Guo Z, et al. A 0.5 V rate-resolution scalable SAR ADC with 63.7 dB SFDR. IEEE Int Symp Circuits and Systems (ISCAS), 2013:2030[5] Zhu Z, Liang Y. A 0.6-V 38-nW 9.4-ENOB 20-kS/s SAR ADC in 0.18-CMOS for medical implant devices. IEEE Trans Circuits Syst I, 2015, 62(9):2167 doi: 10.1109/TCSI.2015.2451812[6] Liu C C, Chang S J, Huang G Y, et al. A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure. IEEE J Solid-State Circuits, 2010, 45(4):731 doi: 10.1109/JSSC.2010.2042254[7] Zhu Y, Chan C H, Chio U F, et al. A 10-bit 100-MS/s reference-free SAR ADC in 90 nm CMOS. IEEE J Solid-State Circuits, 2010, 45(6):1111 doi: 10.1109/JSSC.2010.2048498[8] Cho S H, Lee C K, Kwon J K, et al. A 550-10-b 40-MS/s SAR ADC with multistep addition-only digital error correction. IEEE J Solid-State Circuits, 2011, 46(8):1881 doi: 10.1109/JSSC.2011.2151450[9] Wei H, Chan C H, Chio U F, et al. An 8-b 400-MS/s 2-b-per-cycle SAR ADC with resistive DAC. IEEE J Solid-State Circuits, 2012, 47(11):2763 doi: 10.1109/JSSC.2012.2214181[10] Huang G Y, Chang S J, Liu C C, et al. 10-bit 30-MS/s SAR ADC using a switchback switching method. IEEE Trans Very Large Scale Integr Syst, 2013, 21(3):584 doi: 10.1109/TVLSI.2012.2190117[11] Ginsburg B P, Chandrakasan A P. An energy-efficient charge recycling approach for a SAR converter with capacitive DAC. IEEE International Symposium on Circuits and Systems (ISCAS), 2005:184 http://www.mtl.mit.edu/researchgroups/icsystems/pubs/conferences/2005/ginsburg_iscas2005_slides.pdf[12] Hariprasath V, Guerber J, Lee S H, et al. Merged capacitor switching based SAR ADC with highest switching energy-efficiency. Electron Lett, 2010, 46(9):620 doi: 10.1049/el.2010.0706[13] Sanyal A, Sun N. SAR ADC architecture with 98% reduction in switching energy over conventional scheme. Electron Lett, 2013, 49(4):1 http://ieeexplore.ieee.org/iel7/2220/6464656/06464667.pdf[14] Zhu Z, Xiao Y, Song X. V_CM-based monotonic capacitor switching scheme for SAR ADC. Electron Lett, 2013, 49(5):1[15] Wang X, Zhou X, Li Q. A high-speed energy-efficient segmented prequantize and bypass DAC for SAR ADCs. IEEE Trans Circuits Syst Ⅱ, 2015, 62(8):756 doi: 10.1109/TCSII.2015.2435432[16] Chen S W M, Brodersen R W. A 6-bit 600-MS/s 5.3-mW asynchronous ADC in 0.13-CMOS. IEEE J Solid-State Circuits, 2006, 41(12):2669 doi: 10.1109/JSSC.2006.884231[17] Jiang T, Liu W, Zhong F Y, et al. A single-channel, 1.25-GS/s, 6-bit, 6.08-mW asynchronous successive-approximation ADC with improved feedback delay in 40-nm CMOS. IEEE J Solid-State Circuits, 2012, 47(10):2444 doi: 10.1109/JSSC.2012.2204543[18] Verbruggen B, Iriguchi M, Craninckx J. A 1.7 mW 11 b 250 MS/s 2×interleaved fully dynamic pipelined SAR ADC in 40nm digital CMOS. IEEE International Solid-State Circuits Conference (ISSCC), 2012:466 http://ieeexplore.ieee.org/xpl/articleDetails.jsp?arnumber=6332545&sortType%3Dasc_p_Sequence%26filter%3DAND%28p_IS_Number%3A6392234%29[19] Kull L, Toifl T, Schmatz M, et al. A 3.1 mW 8 b 1.2 GS/s single-channel asynchronous SAR ADC with alternate comparators for enhanced speed in 32 nm digital SOI CMOS. IEEE J Solid-State Circuits, 2013, 48(12):3049 doi: 10.1109/JSSC.2013.2279571[20] Kapusta R, Shen J, Decker S, et al. A 14b 80 MS/s SAR ADC with 73.6 dB SNDR in 65 nm CMOS. IEEE J Solid-State Circuits, 2013, 48(12):3059 doi: 10.1109/JSSC.2013.2274113[21] Rabaey J M, Chandrakasan A P, Nikolic B. Digital integrated circuits. Englewood Cliffs: Prentice Hall, 2002[22] Guerber J, Venkatram H, Gande M, et al. A 10-b ternary SAR ADC with quantization time information utilization. IEEE J Solid-State Circuits, 2012, 47(11):2604 doi: 10.1109/JSSC.2012.2211696[23] Huang G Y, Chang S J, Liu C C, et al. A 1-μW 10-bit 200-kS/s SAR ADC with a bypass window for biomedical applications. IEEE J Solid-State Circuits, 2012, 47(11):2783 doi: 10.1109/JSSC.2012.2217635[24] Miyahara M, Asada Y, Paik D, et al. A low-noise self-calibrating dynamic comparator for high-speed ADCs. IEEE Asian Solid-State Circuits Conference (ASSCC), 2008:269 http://www.ssc.pe.titech.ac.jp/publications/2008/ASSCC/9-2_Miyahara_3.pdf -

Proportional views

DownLoad:

DownLoad: