| Citation: |

Mengxuan Jiang, Z. John Shen, Jun Wang, Zhikang Shuai, Xin Yin, Bingbing Sun, Linyuan Liao. An insulated gate bipolar transistor with surface n-type barrier[J]. Journal of Semiconductors, 2015, 36(12): 124004. doi: 10.1088/1674-4926/36/12/124004

****

M X Jiang, Z. John Shen, J Wang, Z K Shuai, X Yin, B B Sun, L Y Liao. An insulated gate bipolar transistor with surface n-type barrier[J]. J. Semicond., 2015, 36(12): 124004. doi: 10.1088/1674-4926/36/12/124004.

|

An insulated gate bipolar transistor with surface n-type barrier

DOI: 10.1088/1674-4926/36/12/124004

More Information

-

Abstract

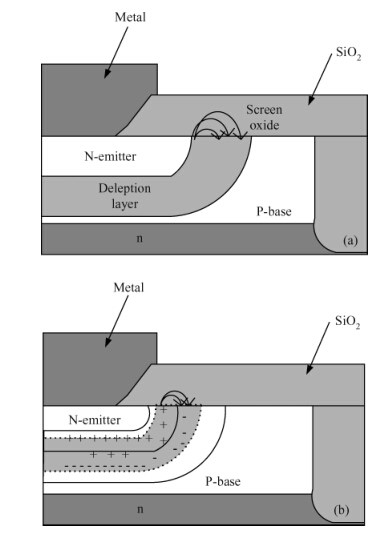

This letter proposes a novel IGBT structure with an n-type barrier(NB-IGBT) formed on the silicon surface to enhance the conductivity modulation effect with a relatively simple fabrication process. TCAD simulation indicates that the NB-IGBT offers a current density 49% higher and turn-off losses 25% lower than a conventional field-stop IGBT(FS-IGBT) with a similar breakdown voltage, turn-off time and avalanche energy. Furthermore, the NB-IGBT exhibits extremely large transconductance, which is favorable to turn-on and turn-off. Therefore, the proposed IGBT offers an attractive option for high-voltage and large-power electronics applications.-

Keywords:

- breakdown voltage,

- conductivity modulation,

- current density,

- latch up,

- IGBT

-

References

[1] [2] [3] [4] [5] [6] [7] [8] [9] [10] [11] [12] [13] [14] [15] [16] [17] [18] [19] [20] [21] -

Proportional views

DownLoad:

DownLoad: