| Citation: |

Fanyang Li. A 0.9 V PSRR improved voltage reference using a wide-band cascaded current mode differentiator[J]. Journal of Semiconductors, 2018, 39(10): 105002. doi: 10.1088/1674-4926/39/10/105002

****

F Y Li, A 0.9 V PSRR improved voltage reference using a wide-band cascaded current mode differentiator[J]. J. Semicond., 2018, 39(10): 105002. doi: 10.1088/1674-4926/39/10/105002.

|

A 0.9 V PSRR improved voltage reference using a wide-band cascaded current mode differentiator

DOI: 10.1088/1674-4926/39/10/105002

More Information

-

Abstract

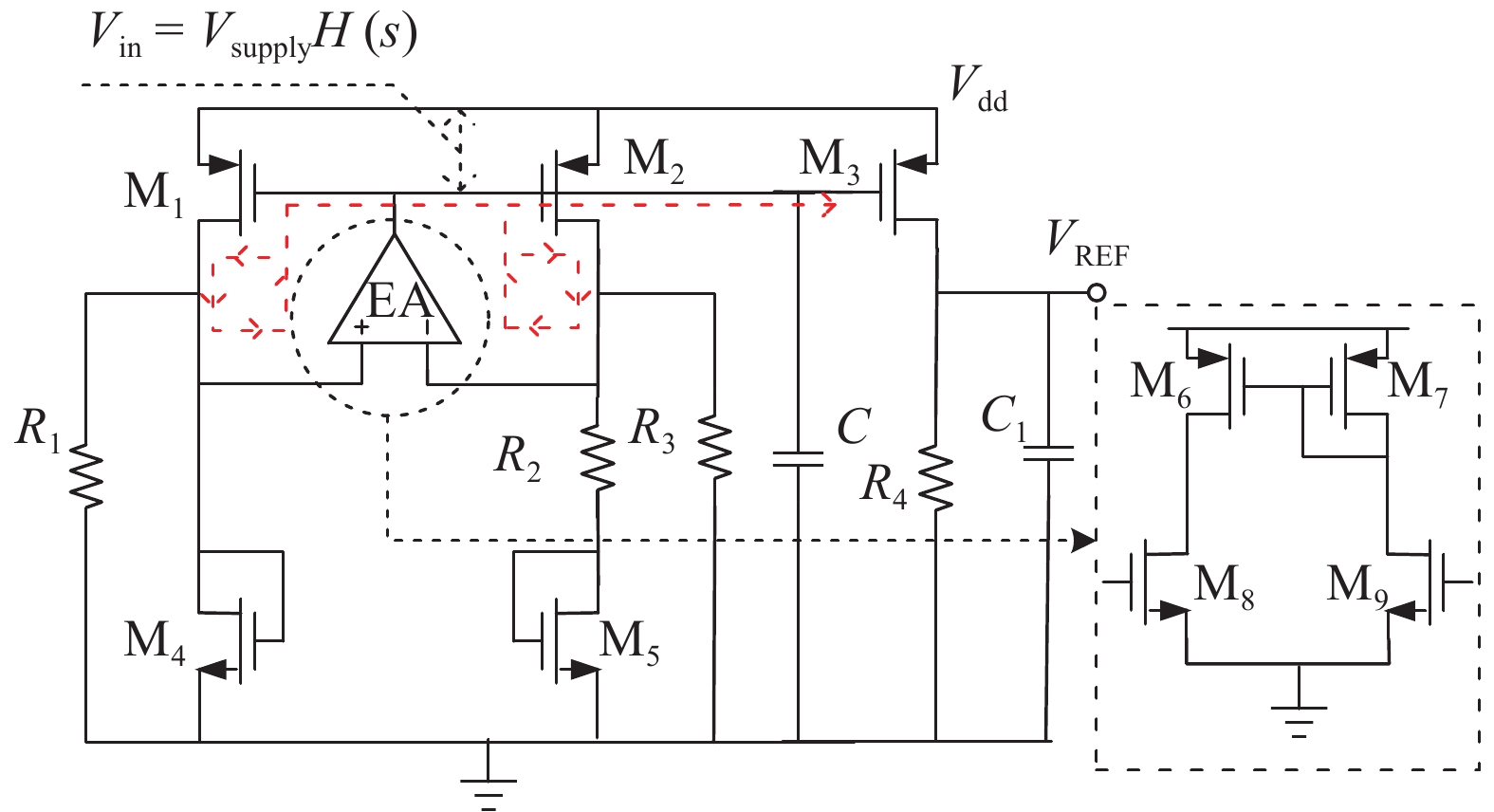

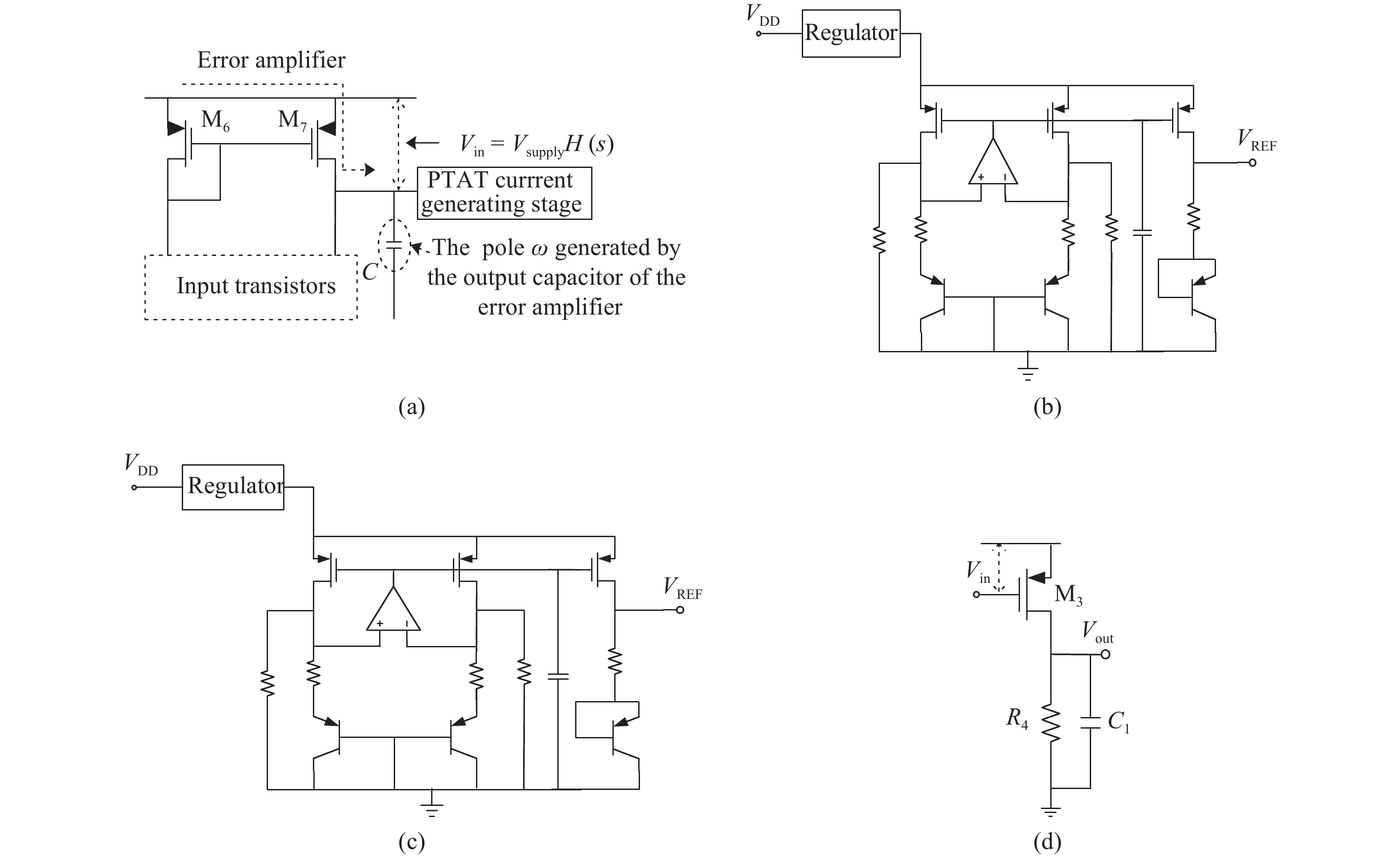

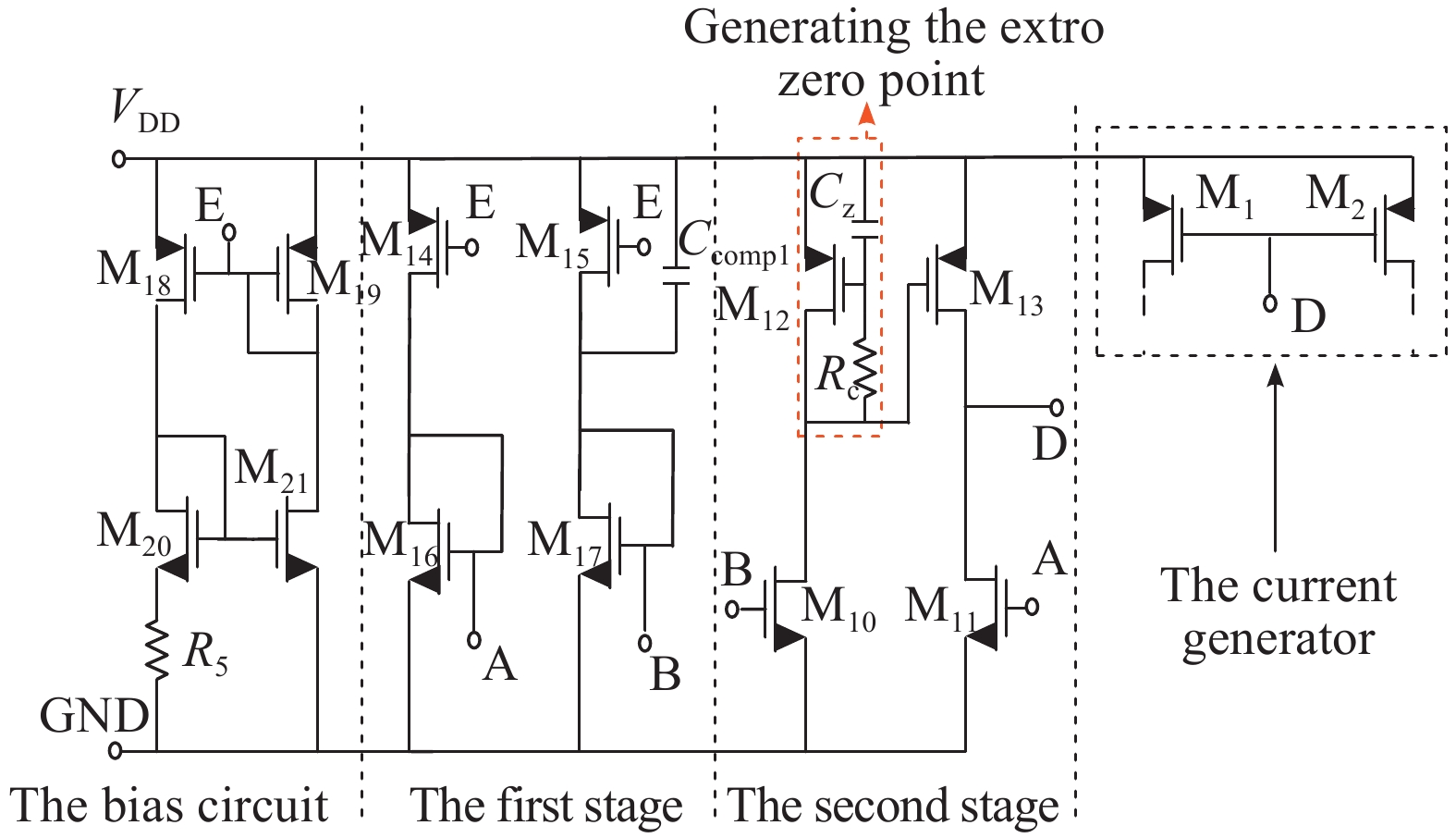

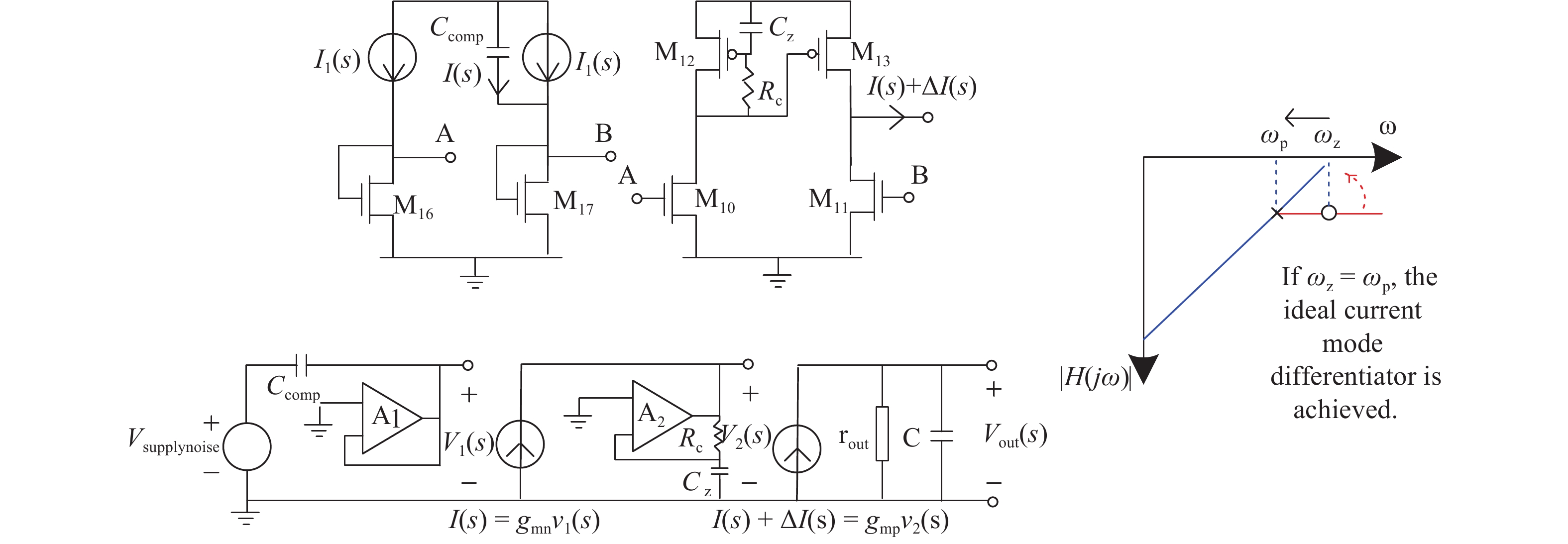

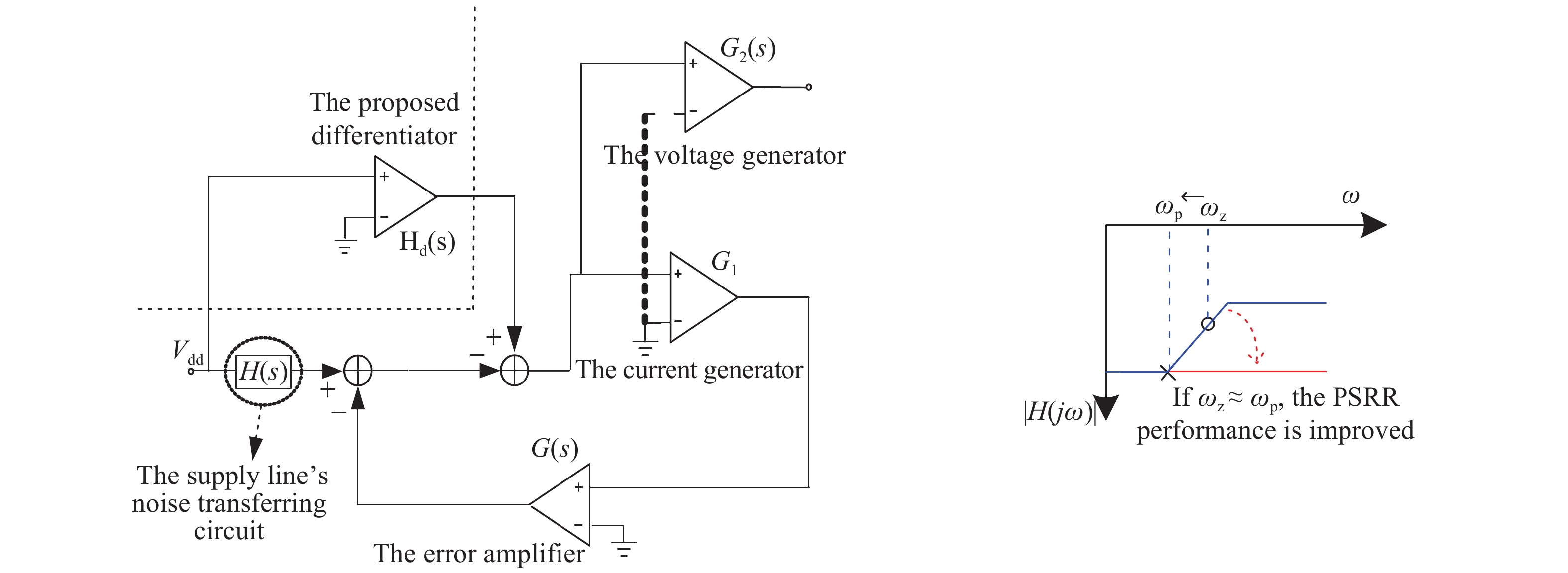

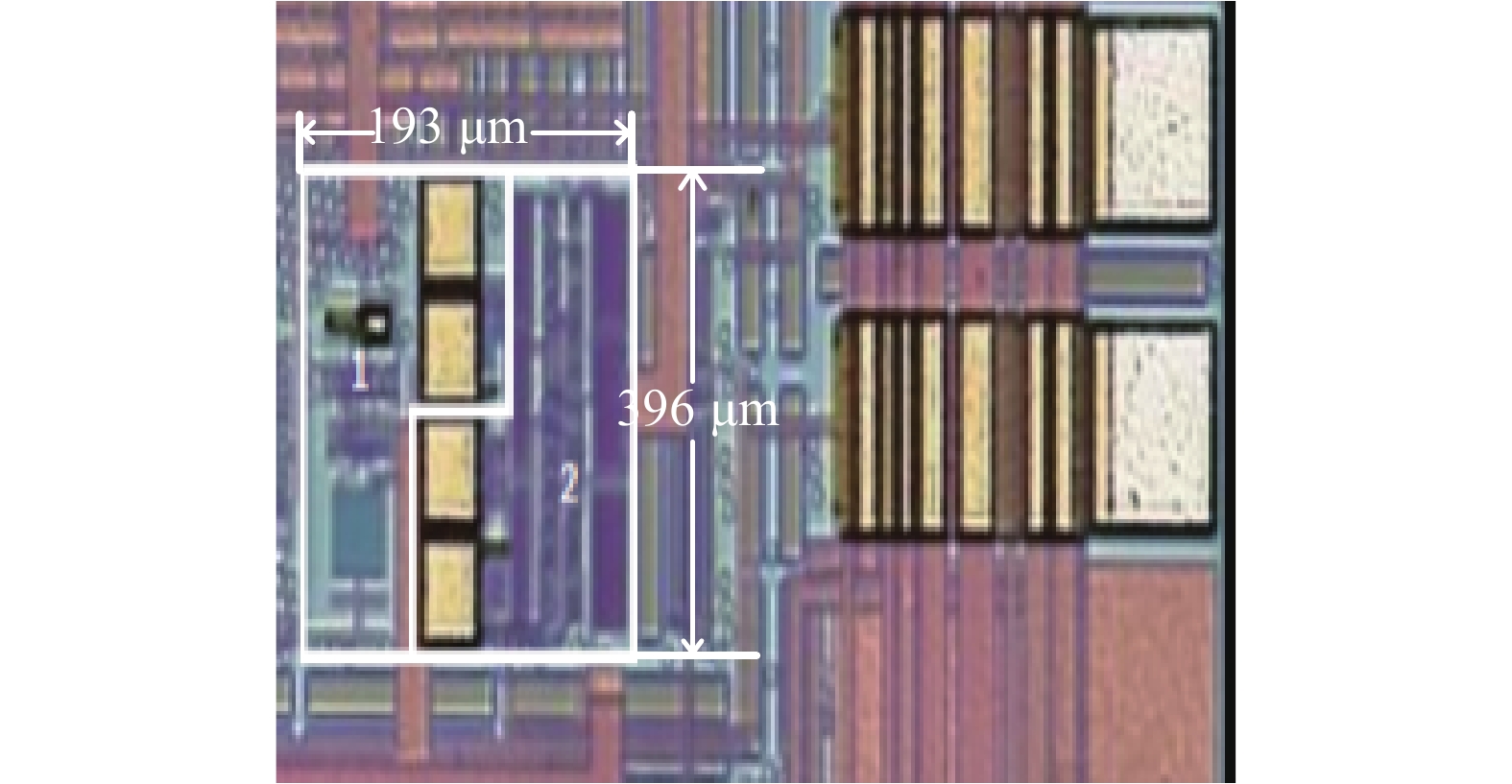

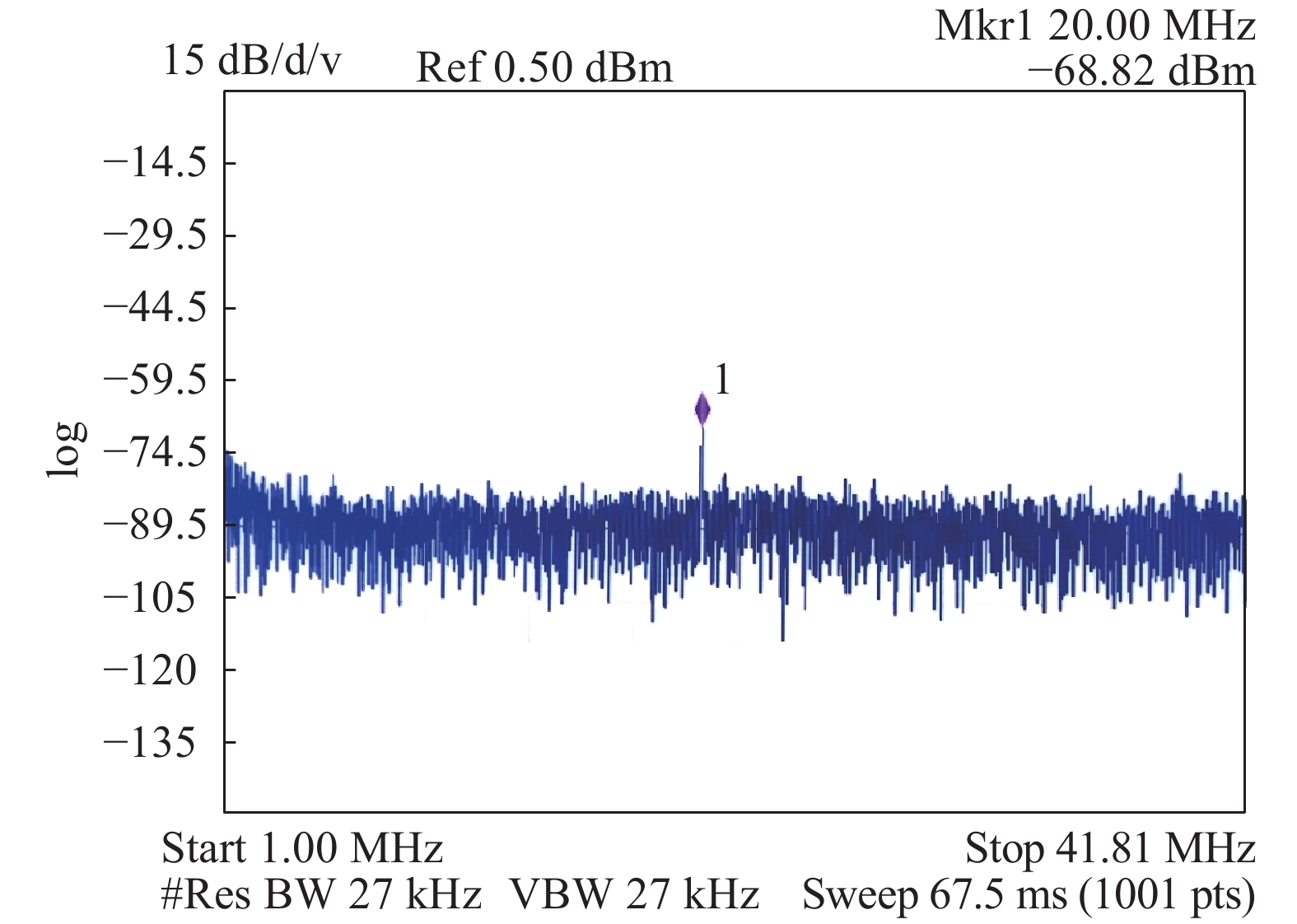

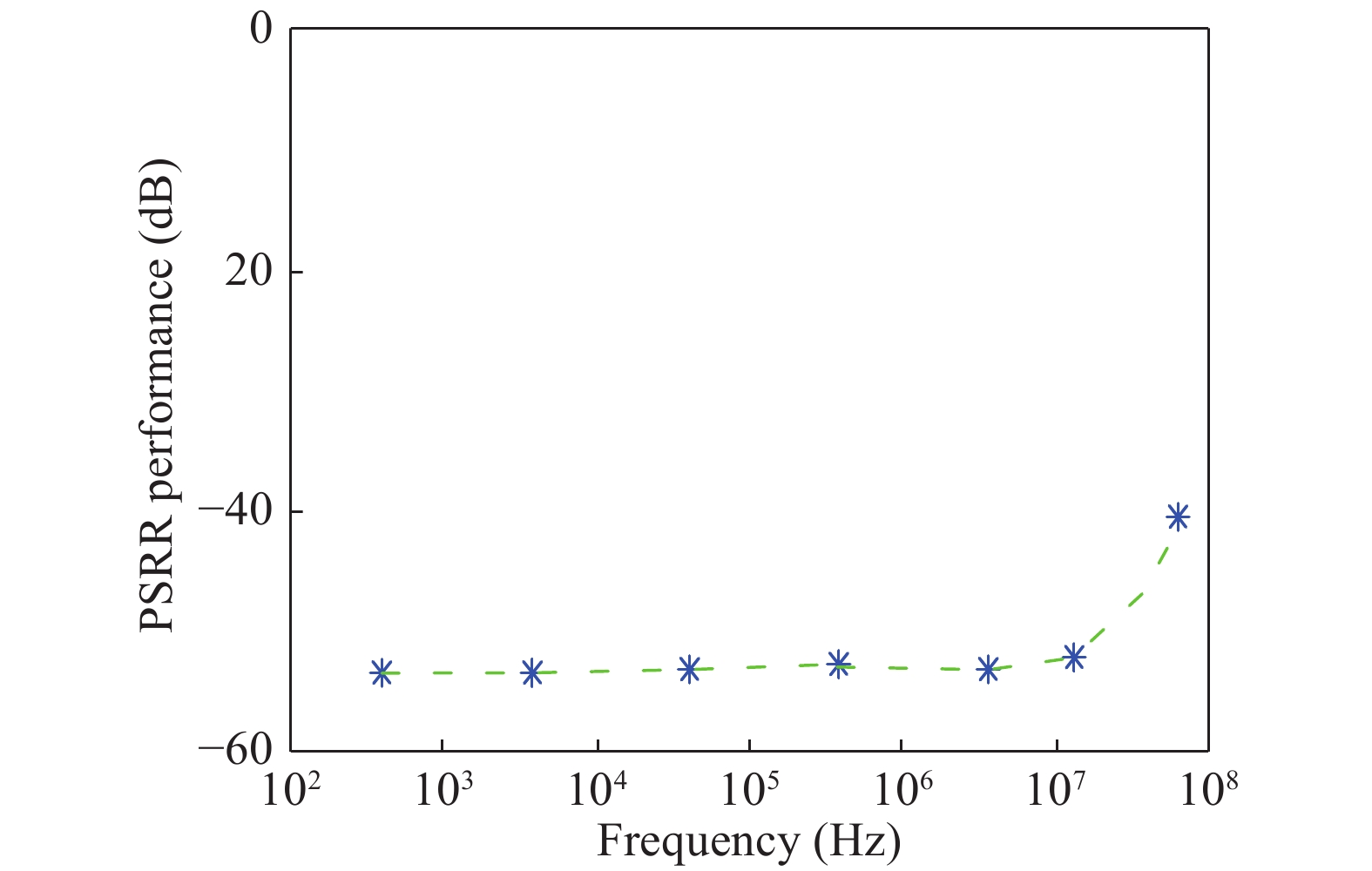

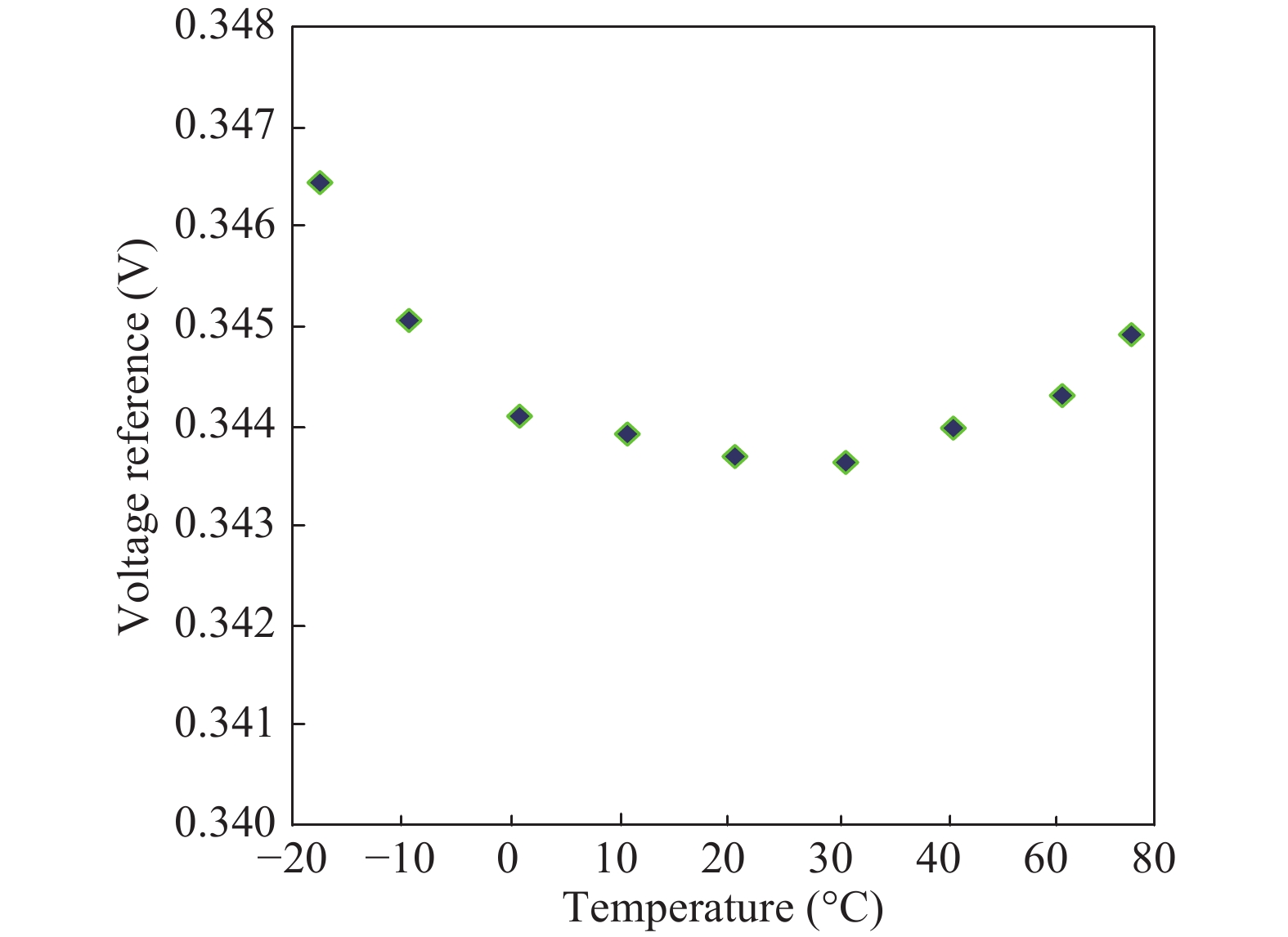

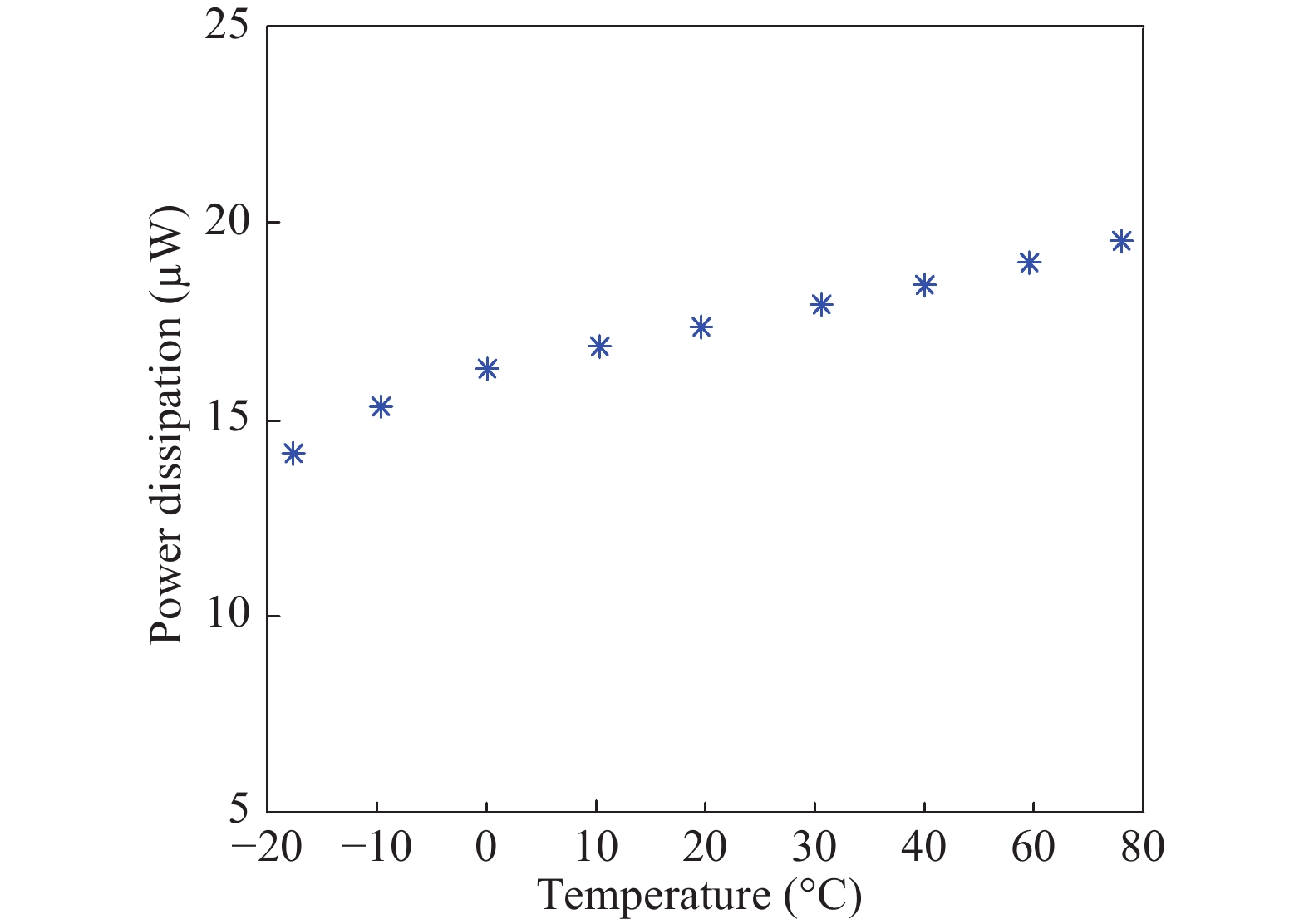

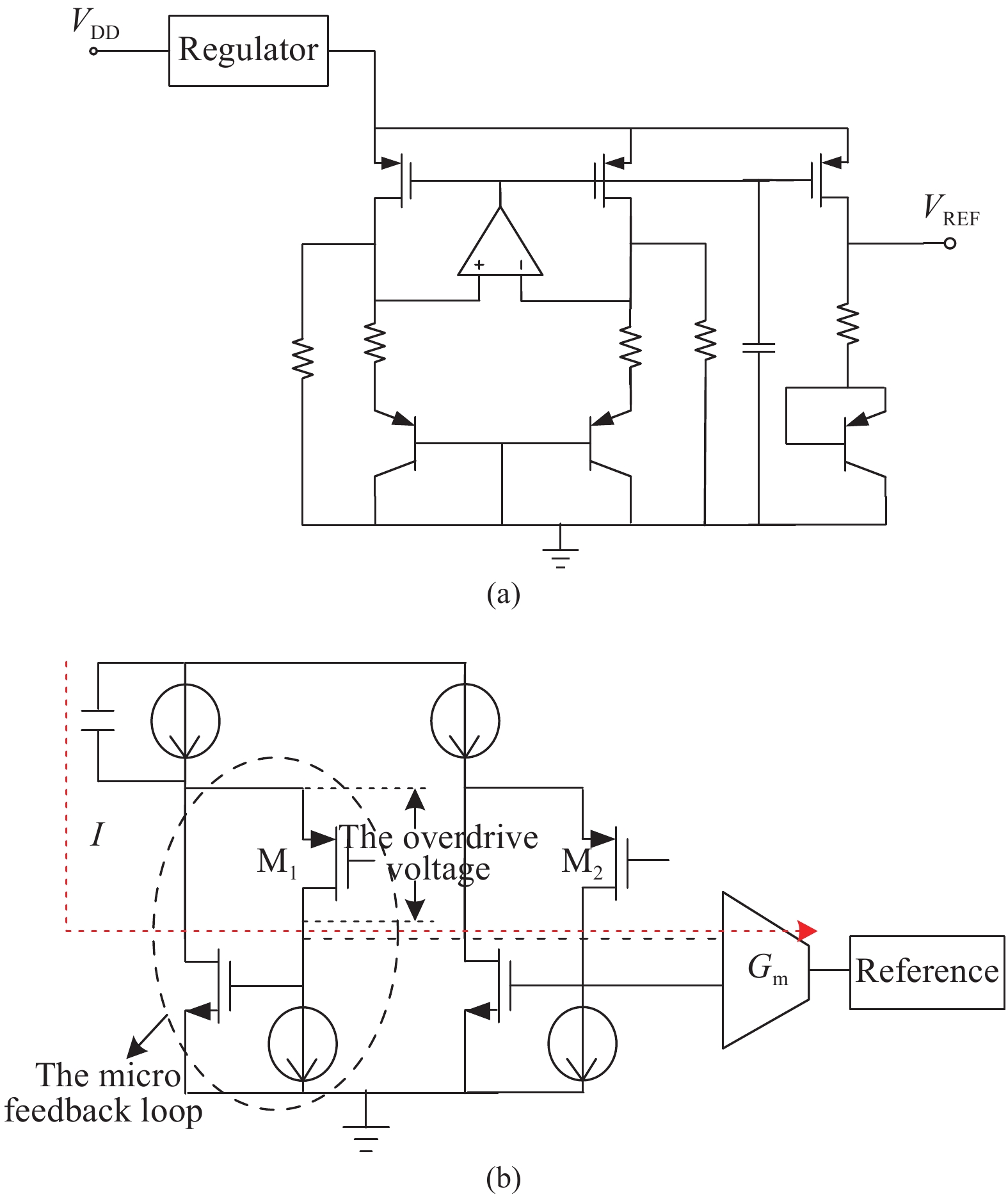

We present a voltage reference using a wide-band cascaded current mode differentiator, for the improved PSRR performance. Compared with the conventional references, the reference with the technique is mainly characterized by a two cascaded stages current mode signal differentiator. In the differentiator, a zero OTA Gm is proposed, to achieve the wide-band differential characteristic. With the technique, the PSRR beyond the pole’s corresponding frequency can be significantly improved with the minimum supply voltage only about VGS_PMOS + (VGS_NMOS − VTH). Fabricated with a 0.18 μm CMOS process, with the 0.9 V supply voltage, the PSRR @ 20 MHz of the reference is achieved at −54 dB. Moreover, the power dissipation is 19 μW.-

Keywords:

- reference,

- current mode,

- differentiator

-

References

[1] De Vita G, Iannaccone G. A sub-1-V, 10 ppm/C, nanopower voltage reference generator. IEEE J Solid-State Circuits, 2007, 42(7): 1536 doi: 10.1109/JSSC.2007.899077[2] Peng L J, Jin X L, Liu M L. Design and optimization of a low-noise voltage reference using chopper stabilization technique. Chin J Electron, 2017, 26(5): 981 doi: 10.1049/cje.2017.03.020[3] Ueno K, Hirose T, Asai T, et al. A 300 nW, 15 ppm/C, 20 ppm/V CMOS voltage reference circuit consisting of subthreshold MOSFETs. IEEE Solid-State Circuits, 2009, 44(7): 2047 doi: 10.1109/JSSC.2009.2021922[4] Zhou Z, Zhu P S, Shi Y, et al. A CMOS voltage reference based on mutual compensation of Vtn and Vtp. IEEE Trans Circuits Syst II, 2012, 59(6): 341 doi: 10.1109/TCSII.2012.2195065[5] Chahardori M, Atarodi M, Sharifkhani M. A sub 1 V high PSRR CMOS bandgap voltage reference. J Microelectron, 2011, 42: 1057 doi: 10.1016/j.mejo.2011.06.010[6] Zhang W J, Zhao Y, Wang J, et al. A band-gap voltage reference for LDO circuit. Appl Mechan Mater, 2014, 599(6): 626[7] Zhang B, Feng Q Y. A high PSRR bandgap reference circuit. Microelectronics, 2010, 40(1): 58[8] Zhu Y M, Liu F, Yang Y J, et al. A –115 dB PSRR CMOS band gap reference with a novel voltage self-regulating technique. IEEE Trans Circuits Syst II, 2012, 59(6): 341 doi: 10.1109/TCSII.2012.2195065[9] Li F Y, Jiang H. A high-PSRR low dropout regulator in lnb using first–stage reference-included coarse-filtering technique. J Circuits Syst Comput, 2015, 24(2): 1550022 doi: 10.1142/S021812661550022X[10] Qu Y, Peng X H, Hou L G, et al. A 0.662 ppm/°C high PSRR CMOS bandgap voltage reference. 13th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT), 2016: 1363[11] Wang L D, Zhan C C, Zhao S X, et al. Design of high-PSRR current-mode bandgap reference with improved frequency compensation. IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC), 2016: 410[12] Ardalan S, Chen D, Sachdev M, et al. Current mode sense amplifier. 48th IEEE Midw Symp Circuits Syst, 2005: 17[13] Park C J, Onabajo M, Silva-Martinaz J. External capacitor-lesss low drop-out regulator with 25 dB superior power supply rejection in the 0.4–4 MHz range. IEEE J Solid-State Circuits, 2014, 49(2): 486 doi: 10.1109/JSSC.2013.2289897[14] Zhao J, Peng X H, Hou L G, et al. A 12.42 μA 0.192 ppm/°C high PSRR curvature-compensated CMOS bandgap voltage reference. 2nd IEEE International Conference on Integrated Circuits and Microsystems (ICICM), 2017: 191[15] Liu Y, Zhan C C, Wang L D, et al. A 0.4-V wide temperature range all-MOSFET subthreshold voltage reference with 0.027%/v line sensitivity. IEEE Trans Circuits Syst II, 2018, 99: 1[16] Kushwaha D, Mishra D K. A nano power voltage reference generator using of sub threshold MOSFETs. International Conference on Information, Communication, Instrumentation and Control (ICICIC), 2017: 1[17] Kushwaha D, Mishra D K. A 415 nW 0.8 V voltage reference circuit using MOSFETs in saturation and sub-threshold regions. 11th International Conference on Industrial and Information Systems (ICIIS), 2016: 149[18] Zeng Y H, Li Y A, Zhang X, et al. Ultra-low-power, high PSRR CMOS voltage reference with negative feedback. IET Circuits, Devices & Systems, 2017, 11(6): 535 -

Proportional views

DownLoad:

DownLoad: