| Citation: |

Yutong Zhang, Bei Chen, Heping Ma. A sample and hold circuit for pipelined ADC[J]. Journal of Semiconductors, 2018, 39(11): 115002. doi: 10.1088/1674-4926/39/11/115002

****

Y T Zhang, B Chen, H P Ma, A sample and hold circuit for pipelined ADC[J]. J. Semicond., 2018, 39(11): 115002. doi: 10.1088/1674-4926/39/11/115002.

|

-

Abstract

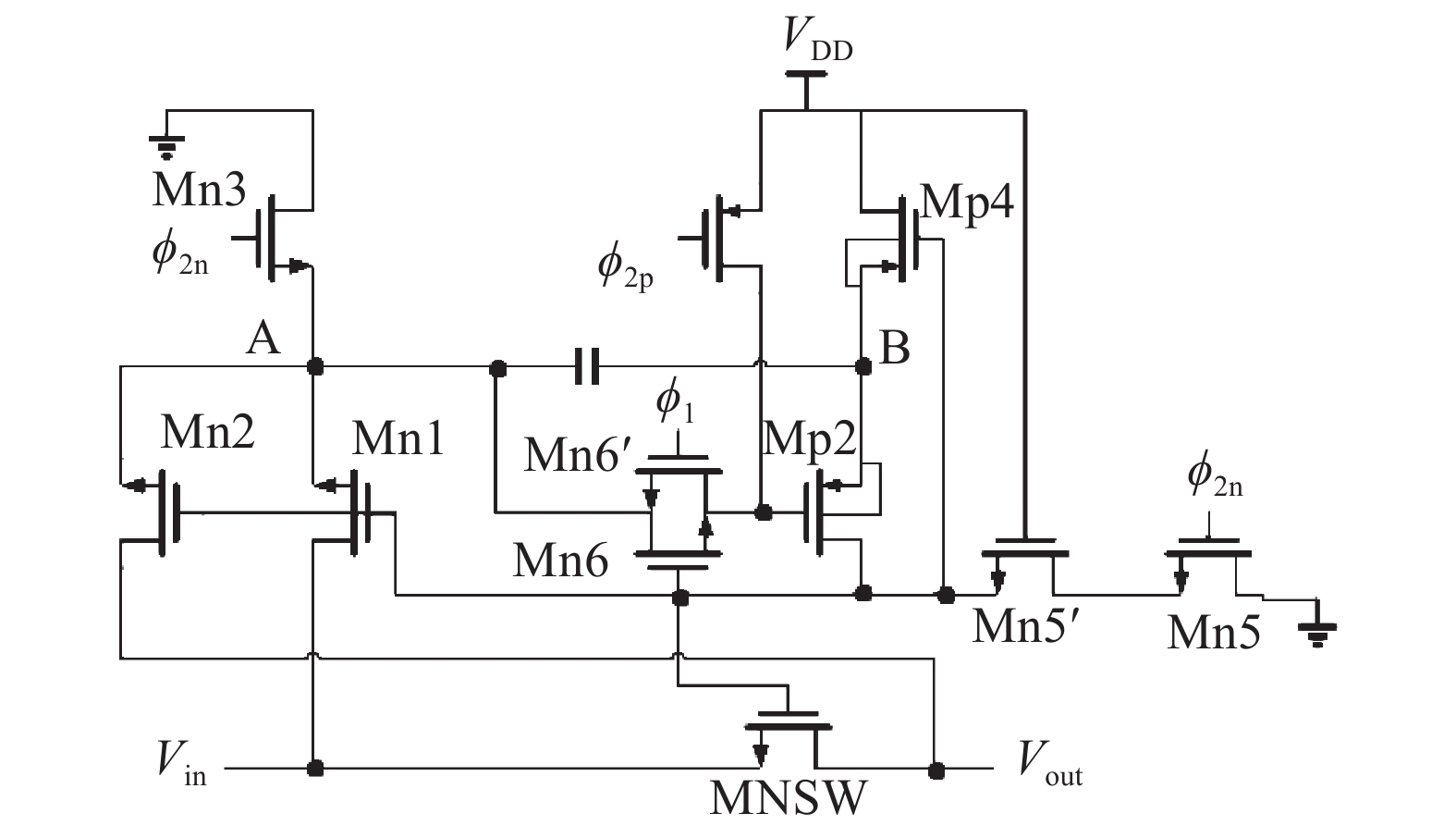

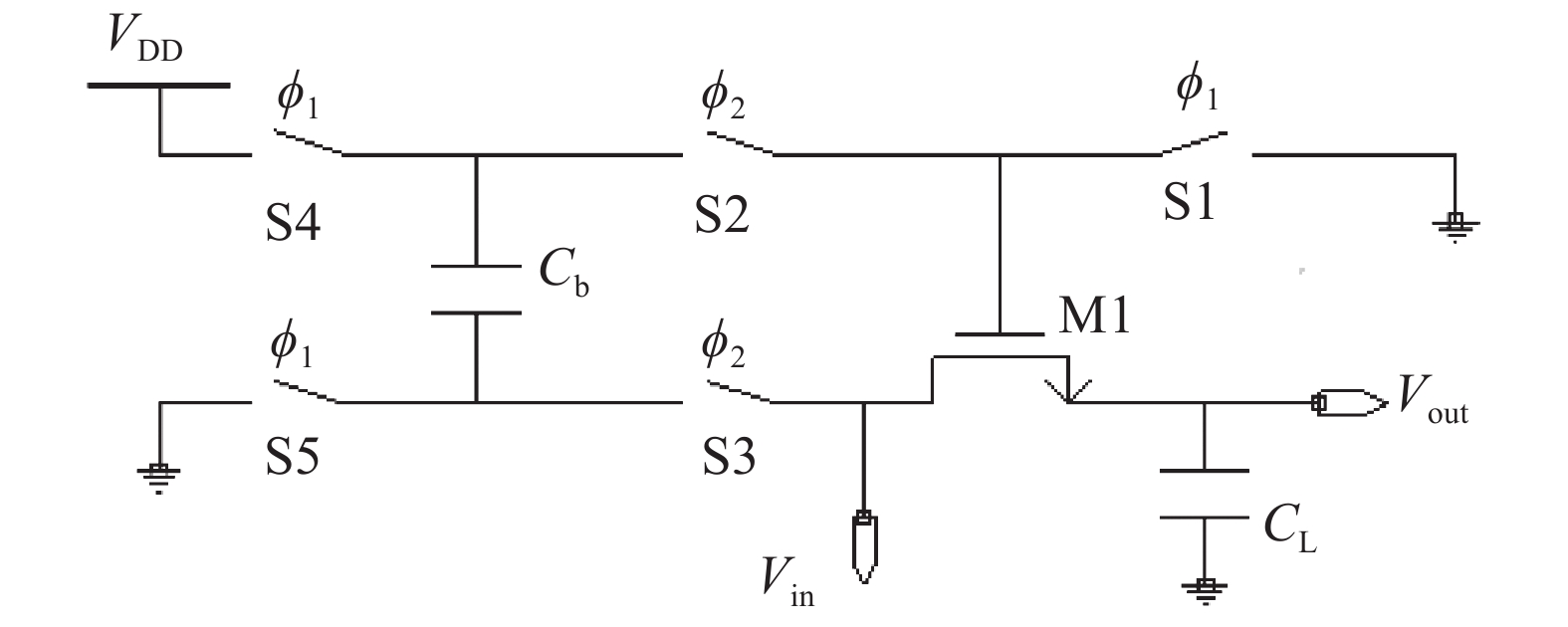

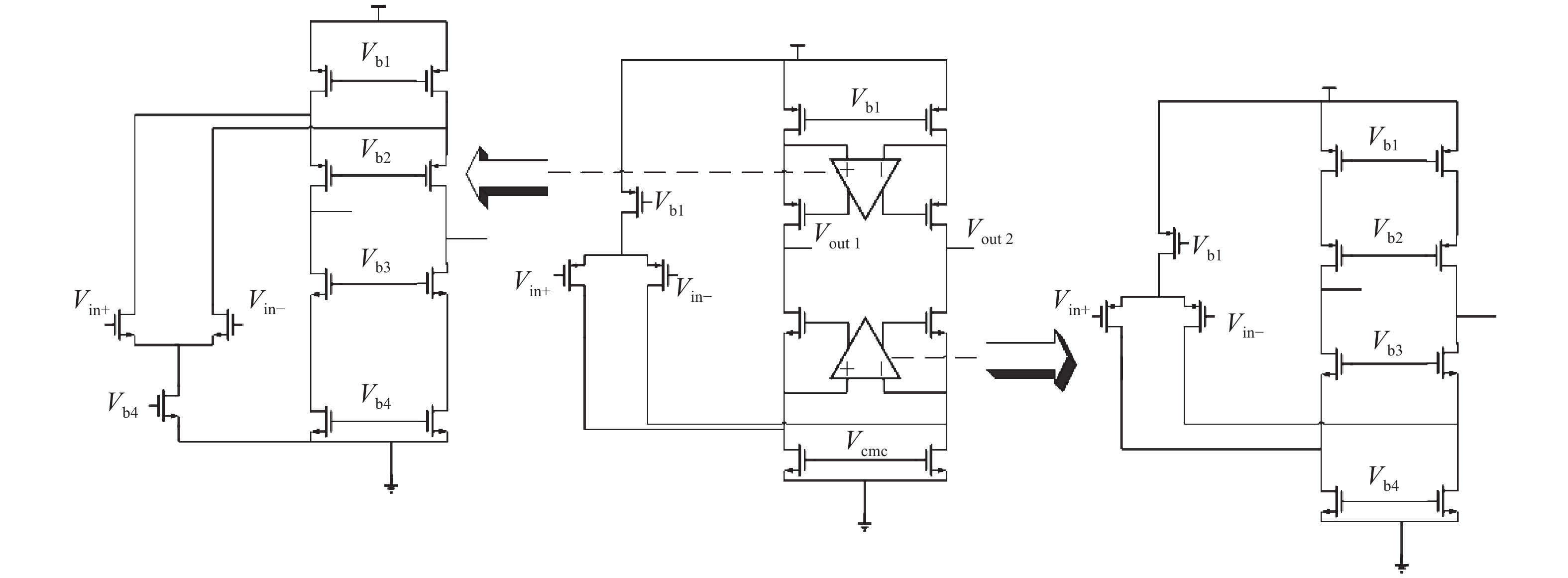

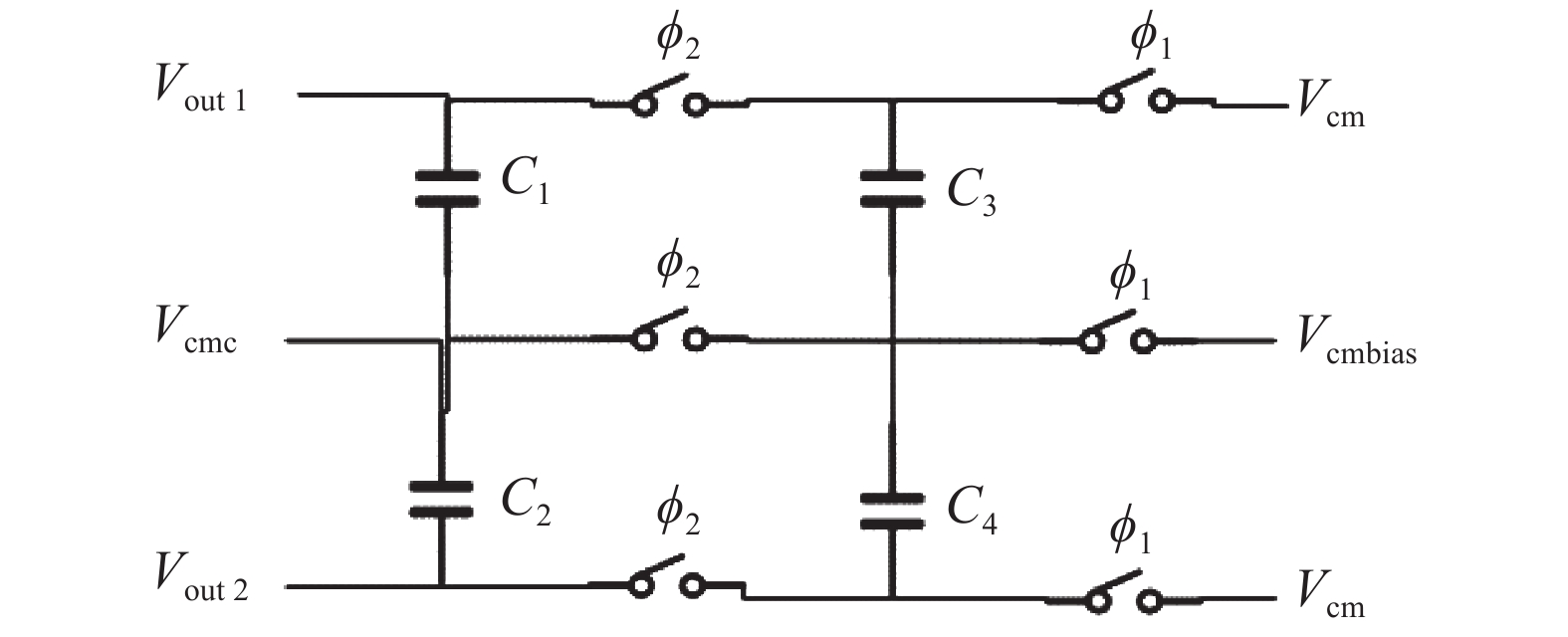

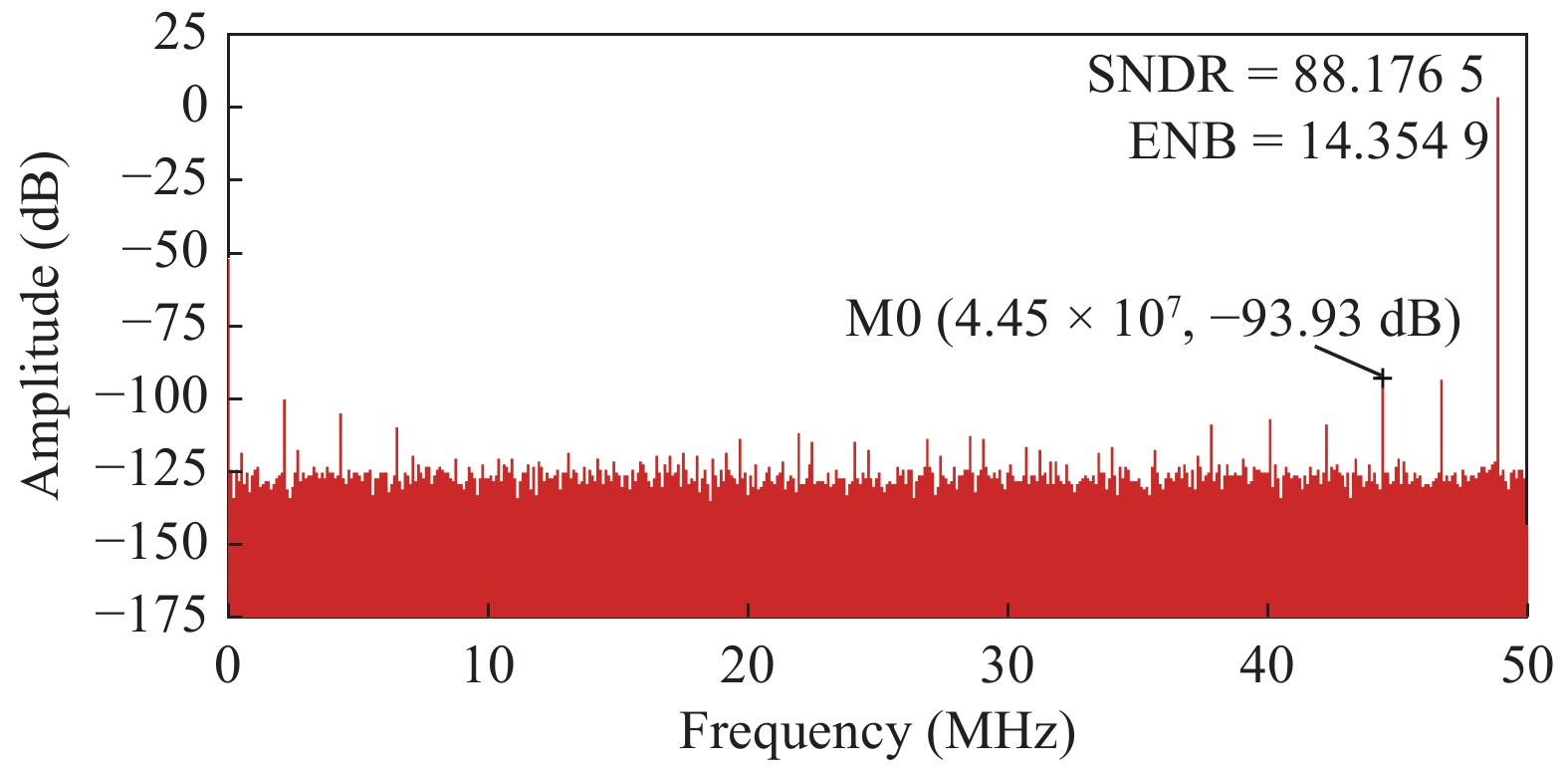

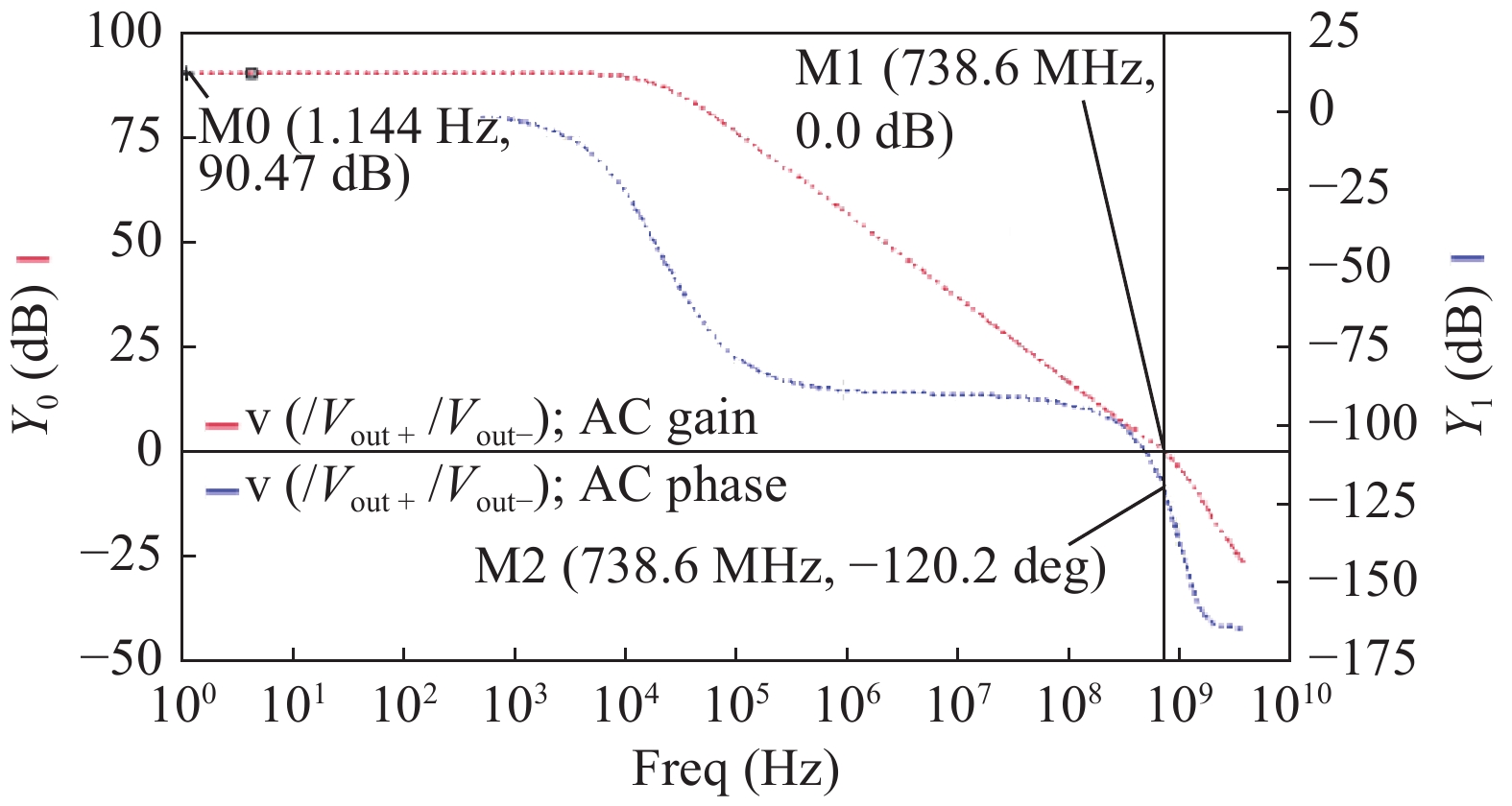

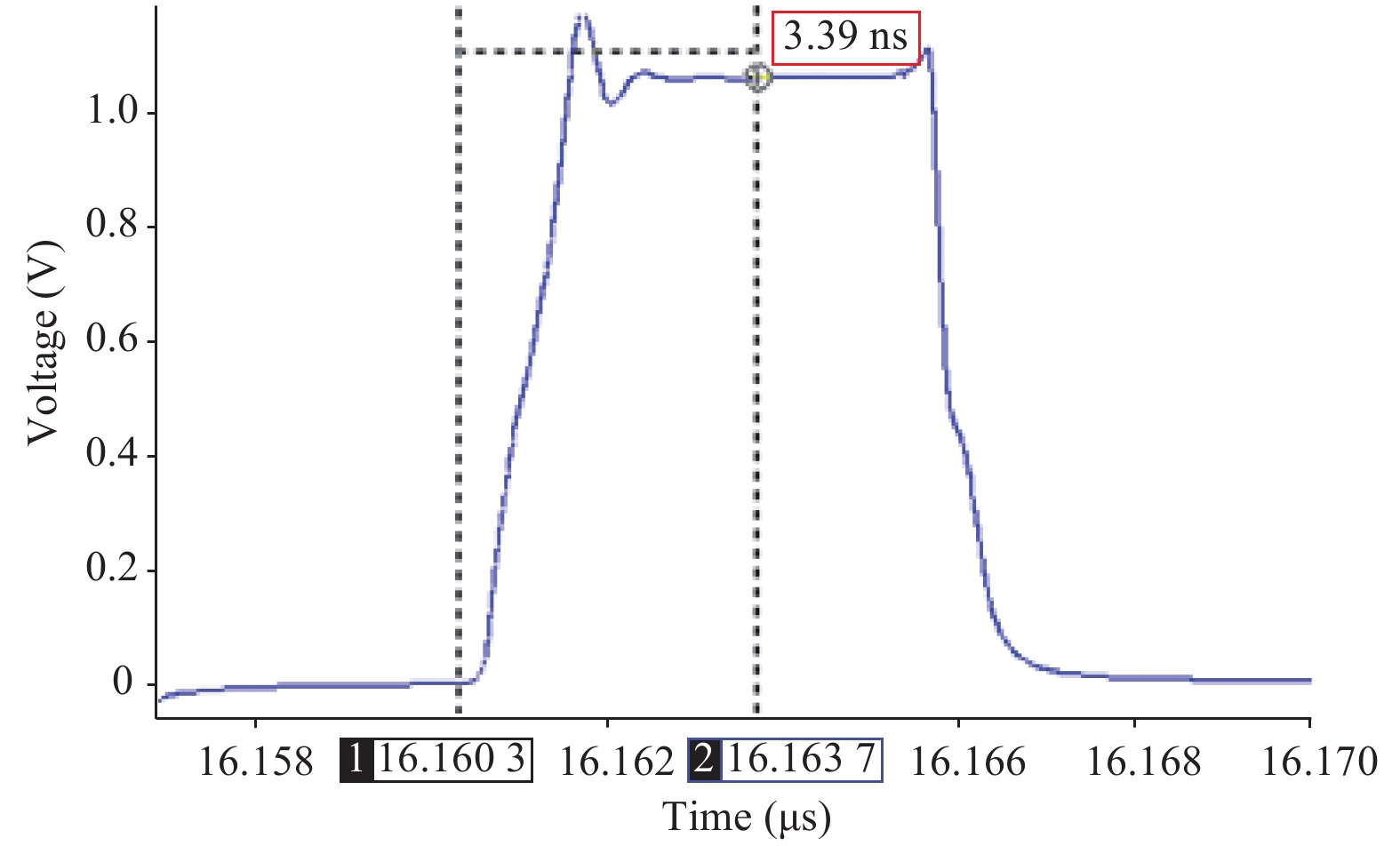

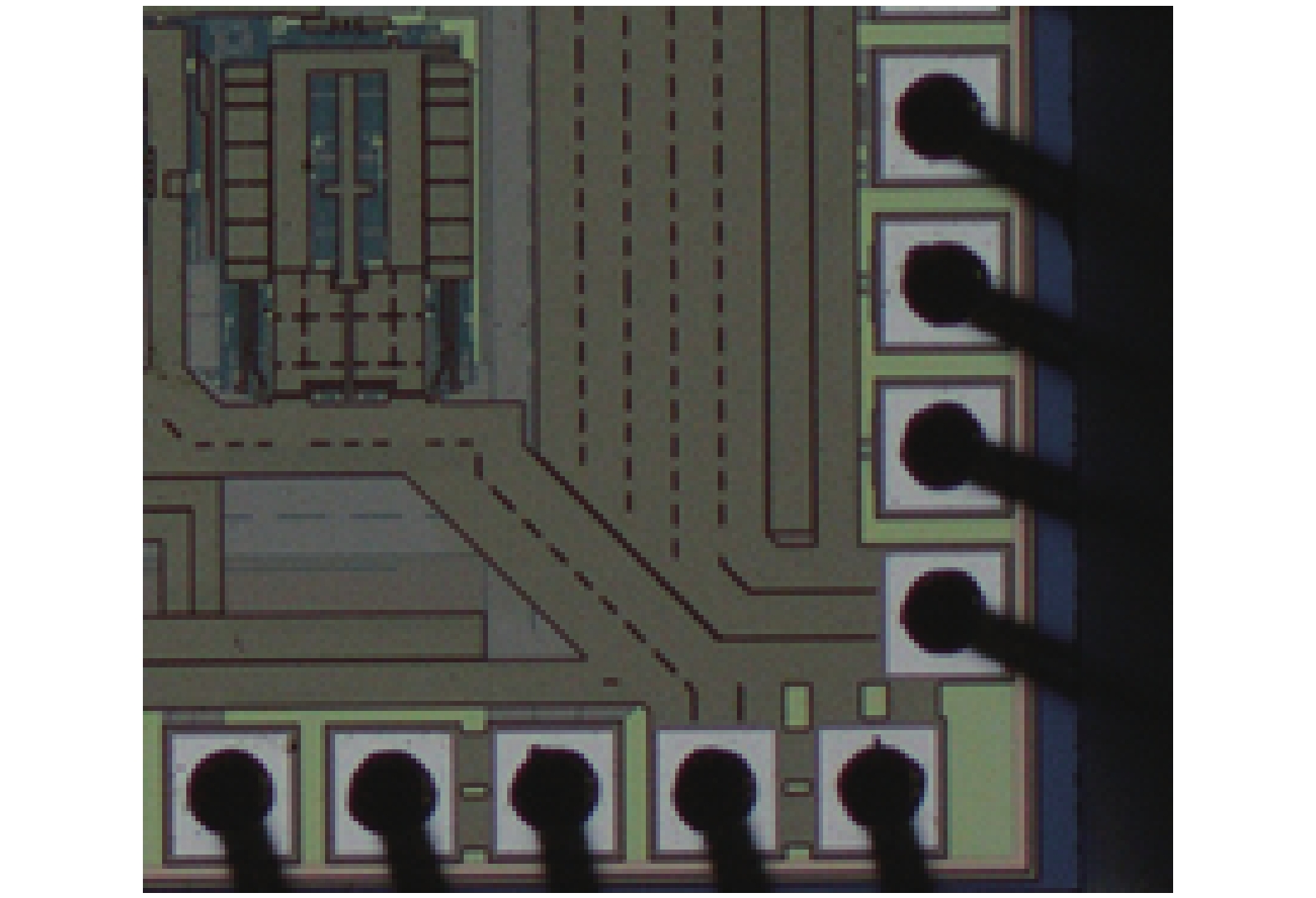

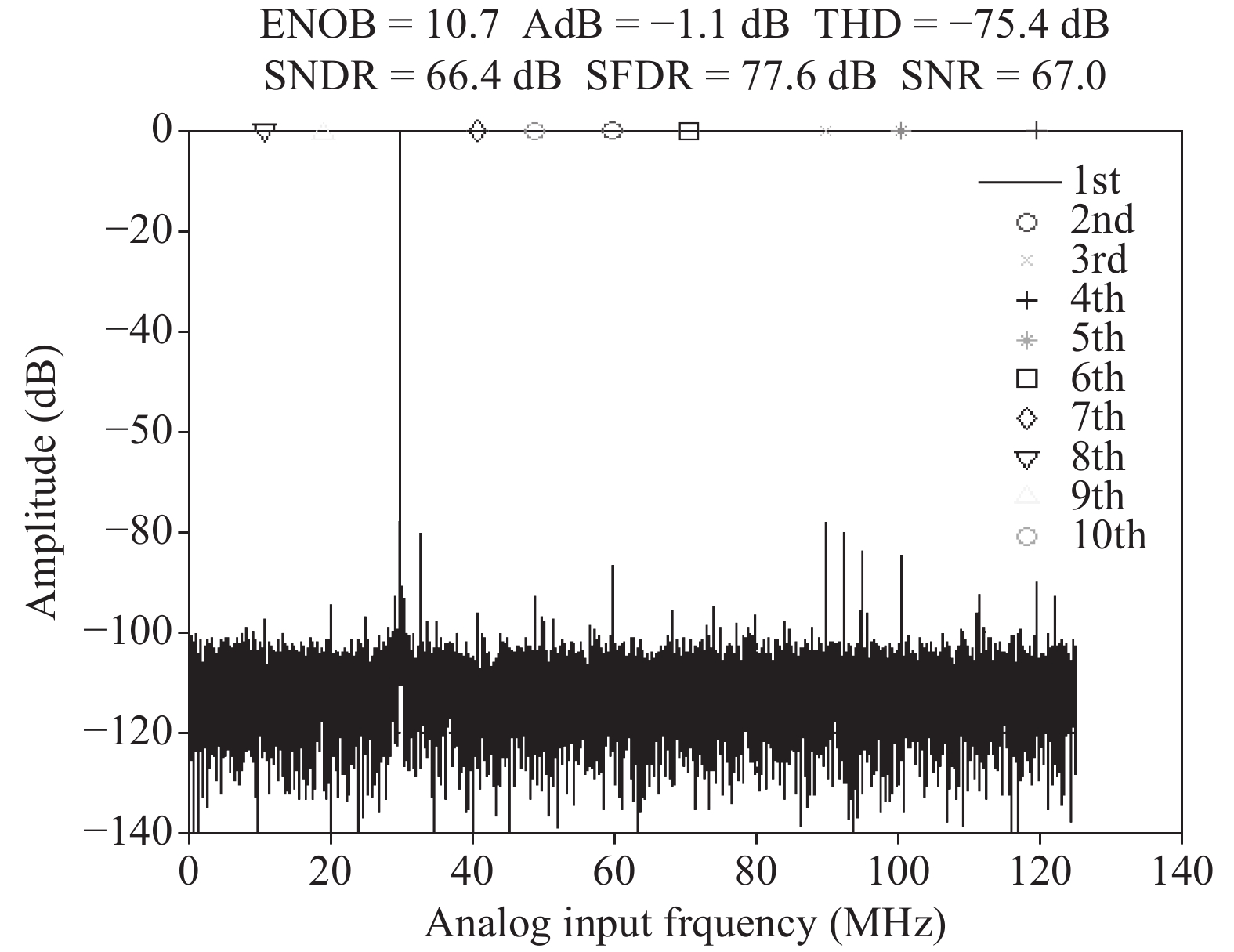

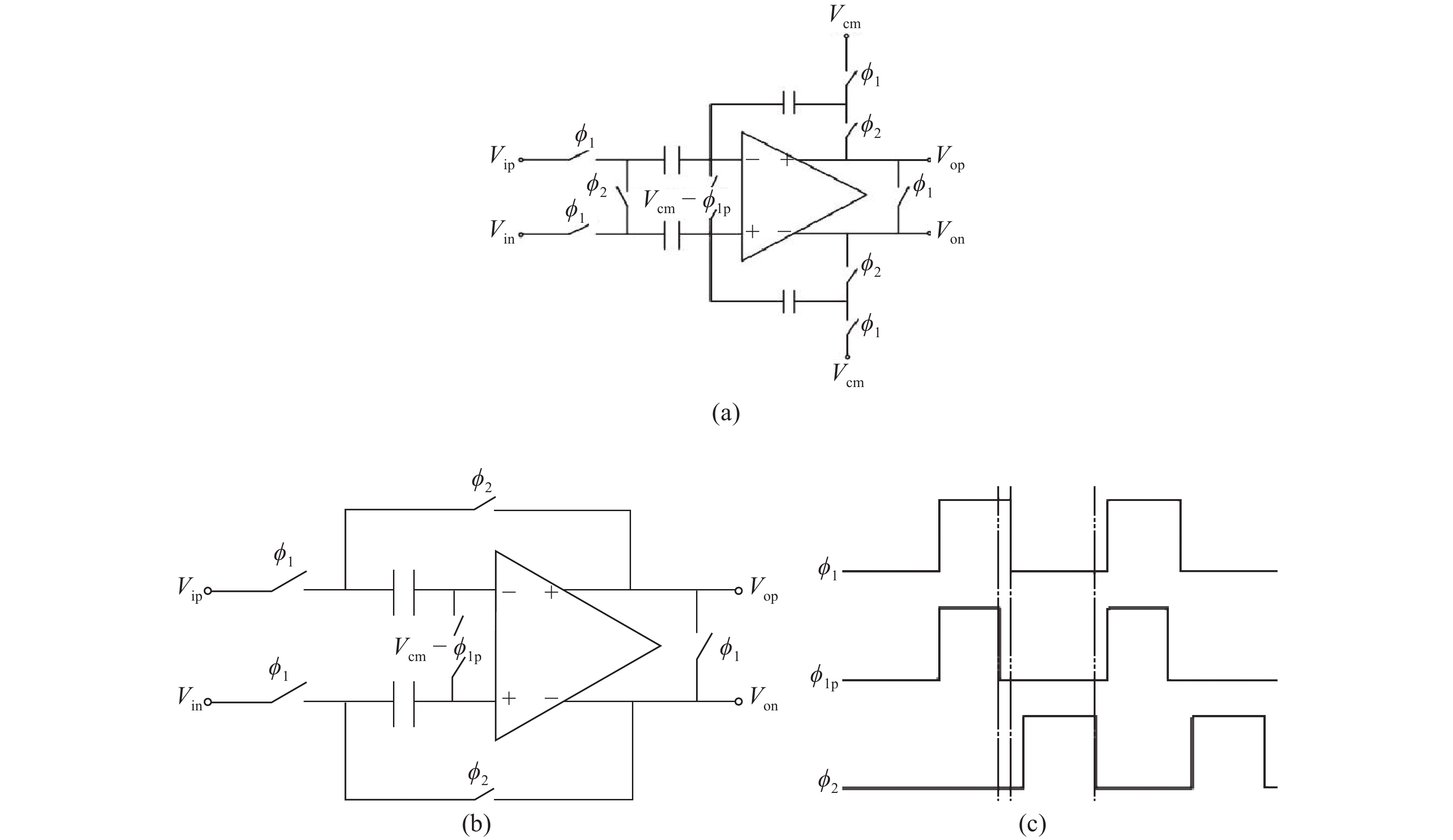

A high performance sample-and-hold (S/H) circuit used in a pipelined analog-to-digital converter (ADC) is presented in this paper. Fully-differential capacitor flip-around architecture was used in this S/H circuit. A gain-boosted folded cascode operational transconductance amplifier (OTA) with a DC gain of 90 dB and a GBW of 738 MHz was designed. A low supply voltage bootstrapped switch was used to improve the linearity of the S/H circuit. With these techniques, the designed S/H circuit can reach 94 dB SFDR for a 48.9 MHz input frequency with 100 MS/s sampling rate. Measurement results of a 14-bit 100-MS/s pipeline ADC with designed S/H circuit are presented.-

Keywords:

- S/H circuit,

- bootstrapped switch,

- gain-boosted OTA

-

References

[1] Zheng X, Wang Z, Li F, et al. A 14-bit 250 MS/s IF sampling pipelined ADC in 180 nm CMOS Process. IEEE Trans Circuits Syst I, 2016, 63(9): 1381 doi: 10.1109/TCSI.2016.2580703[2] Zhang H, Li D, Wan L, et al. A 430 mW 16 b 170 MS/s CMOS pipelined ADC with 77.2 dB SNR and 97.6 dB SFDR. J Semicond, 2016, 37(3): 035003 doi: 10.1088/1674-4926/37/3/035003[3] Li W T, Li F L, Yang C, et al. An 85 mW 14-bit 150 MS/s pipelined ADC with a merged first and second MDAC. Chin Commun, 2015, 12(5): 14 doi: 10.1109/CC.2015.7112040[4] Ahmed M, Tang F, Bermak A. A 14-bit 70 MS/s pipeline ADC with power-efficient back-end stages. IEEE International Conference on Electron Devices and Solid-State Circuits, 2015: 154[5] Prakruthi T G, Yellampalli S. Design and implementation of sample and hold circuit in 180 nm CMOS technology. International Conference on Advances in Computing, Communications and Informatics, 2015: 1148[6] Yang L, Wang Z, Zhou L, et al. A low power sample and hold circuit for 16 bit 100 MS/s pipelined ADC. China Semiconductor Technology International Conference, 2016: 1[7] Yue S, Zhao Y, Pang R, et al. A14-bit 50 MS/s sample-and-hold circuit for pipelined ADC. J Semicond, 2014, 35(5): 055009 doi: 10.1088/1674-4926/35/5/055009[8] Zhu X B, Ni W N, Shi Y. A 10-bit 50-MS/s sample-and-hold circuit with low distortion sampling switches. J Semicond, 2009, 30(5): 055011 doi: 10.1088/1674-4926/30/5/055011[9] Centurelli F, Monsurro P, Trifiletti A. A model for the distortion due to switch on-resistance in sample-and-hold circuits. IEEE International Symposium on Circuits and Systems, 2006: 4[10] Dessouky M, Kaiser A. Very low-voltage digital-audio ΔΣ modulator with 88-dB dynamic range using local switch bootstrapping. IEEE J Solid-State Circuits, 2015, 36(3): 349[11] Sahoo B D, Razavi B. A 12-bit 200-MHz CMOS ADC. IEEE J Solid-State Circuits, 2009, 44(9): 2366 doi: 10.1109/JSSC.2009.2024809[12] Razavi B. Design of analog CMOS integrated circuits. Beijing: China Machine Press, 2013[13] Bult K, Geelen G J G M. A fast-settling CMOS op amp for SC circuits with 90-dB DC gain. IEEE J Solid-State Circuits, 2002, 25(6): 1379[14] Zou R. Design of a fully differential gain boosted operational amplifier for high performance ADC. Sixth International Conference on Business Intelligence and Financial Engineering, 2014: 539[15] Ghosh N N, Todani R, Chaudhuri C, et al. Simplified design method for fully differential gain-boosted folded cascade OTA. Information & Communication Technologies, 2013: 943[16] Choksi O, Carley L R. Analysis of switched-capacitor common-mode feedback circuit. IEEE Trans Circuits Systems II, 2003, 50(12): 906 doi: 10.1109/TCSII.2003.820253[17] Wang H, Hong H, Sun L, et al. A sample-and-hold circuit for 10-bit 100 MS/s pipelined ADC. IEEE International Conference on ASIC, 2011: 480 -

Proportional views

DownLoad:

DownLoad: